【嵌入式C】数据的大小端存储与数据格式转换

以Cortex-M内核为例,实际应用中大部分内核都是 **小端 **存储,以STM32为例,全部都是小端,而且是芯片设计之初就固化进去的,不可修改。

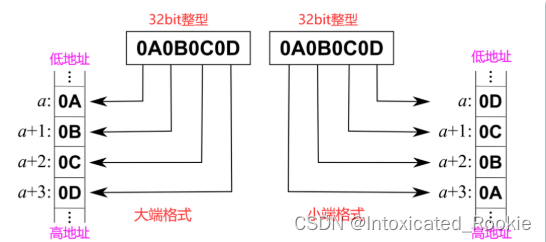

1. 大小端存储格式图解

通俗的将:

- 大端:低字节存储在高地址,高字节存储在低地址

- 小端:低字节存储在低地址,高字节存储在高地址 低低,高高

2. 数据类型转换函数

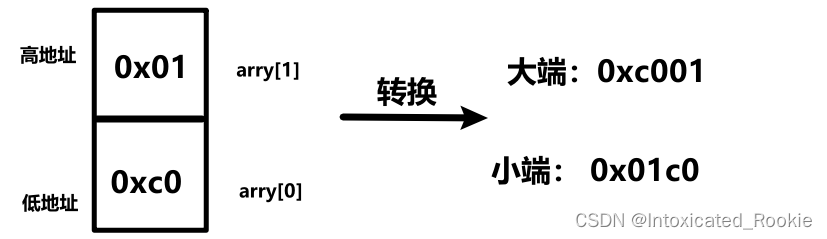

u8 数组与 u16 数值的转换

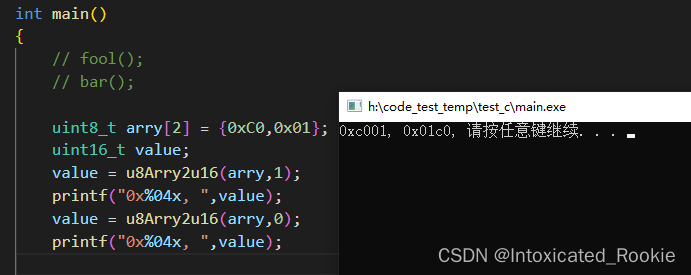

2.1 u8数组转u16

// uModeFlag: 1 big-endian 0: little-endian

uint16_t u8Arry2u16(uint8_t *pBuffer, uint8_t uModeFlag)

{

uint16_t uShort = 0;

uShort = *pBuffer++;

if(1 == uModeFlag){

uShort = (uShort << 8) | (*pBuffer);

}else if(0 == uModeFlag){

uShort |= (*pBuffer) << 8;

}

return uShort;

}

// 测试

uint8_t arry[2] = {0xC0,0x01};

uint16_t value;

value = u8Arry2u16(arry,1); // 大端,输出 0xC001

printf("0x%04x, ",value);

value = u8Arry2u16(arry,0); // 小端,输出 0x01c0

printf("0x%04x, ",value);

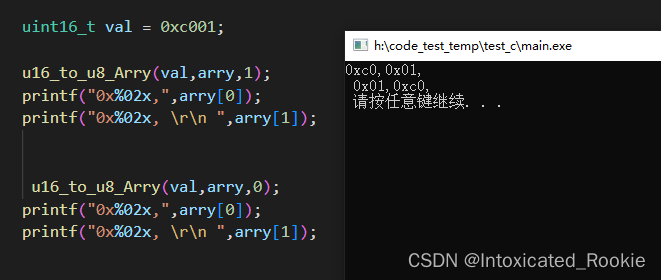

2.2 u16数转u8数组

// uModeFlag: 1 big-endian 0: little-endian

void u16_to_u8_Arry(uint16_t srcdata,uint8_t *destdata,uint8_t uModeFlag)

{

switch (uModeFlag)

{

case 1:{

*(destdata) = (uint8_t)(srcdata >>8 & 0xFF);

*(destdata +1) = (uint8_t)(srcdata & 0xFF);

break;

}

case 0:{

*(destdata+1) = (uint8_t)(srcdata >>8 & 0xFF); //

*destdata = (uint8_t)(srcdata & 0xFF); //

break;

}

default:

break;

}

}

// 测试

uint16_t val = 0xc001;

u16_to_u8_Arry(val,arry,1);

printf("0x%02x,",arry[0]);

printf("0x%02x, \r\n ",arry[1]); // 0xc0 0x01

u16_to_u8_Arry(val,arry,0);

printf("0x%02x,",arry[0]);

printf("0x%02x, \r\n ",arry[1]); // 0x01,0xc0

2590

2590

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?