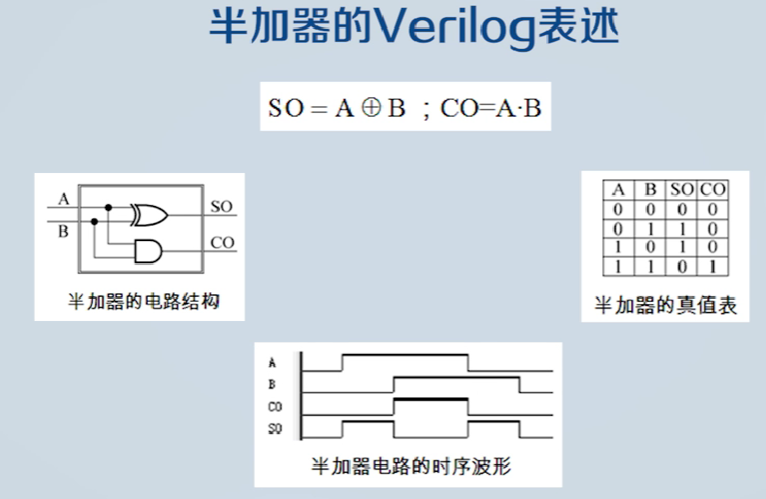

半加器

半加器不考虑低位进位来的进位值,只有两个输入,两个输出。由一个与门和异或门构成.

h_adder.v:

// 2022-1-25 verilog 学习

// 组合逻辑电路,不需要时钟控制,信号一来就输出

// 半加器

`timescale 1ns/10ps

module h_adder(

a,

b,

so,

co

);

input a;

input b;

output so; // 进位,异或 so = a^b;

output co; // 本位,与,co = a&b;

assign so = a^b;

assign co = a&b;

endmodule

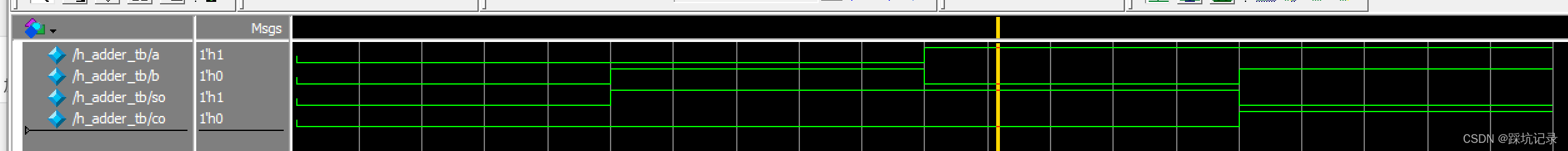

// testbench 测试台

module h_adder_tb;

reg a,b;

wire so,co;

h_adder h_adder(

.a(a),

.b(b),

.so(so),

.co(co)

);

initial begin

a<=0;b<=0;

#10 a<=0;b<=1;

#10 a<=1;b<=0;

#10 a<=1;b<=1;

#10 $stop;

end

endmodule

modelsim:

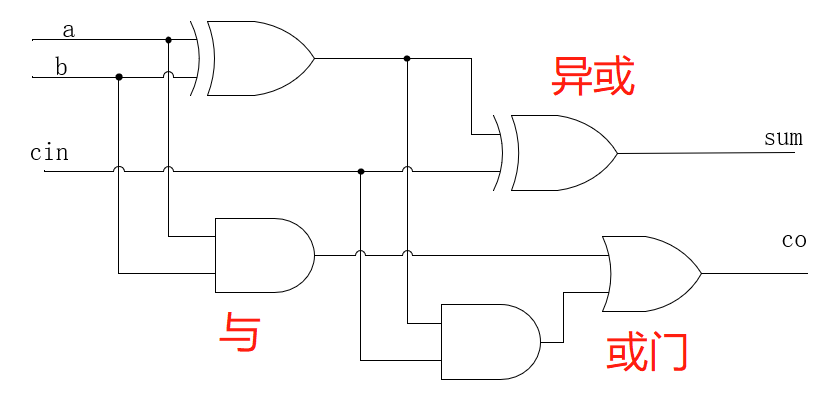

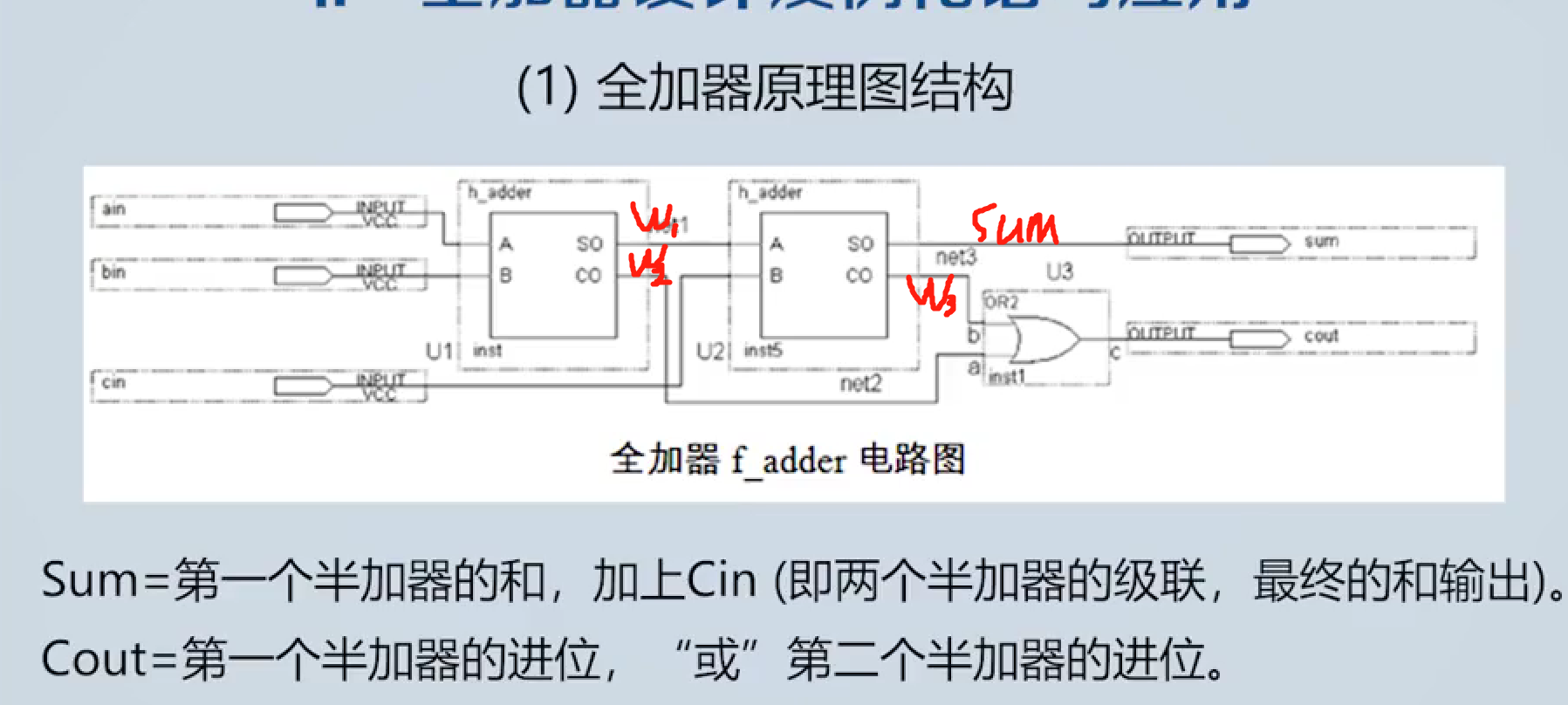

全加器

当多位数相加时,半加器可用于最低位求和,并给出进位数。第二位的相加有两个待加数和,还有一个来自前面低位送来的进位数。这三个数相加,得出本位和数(全加和数)和进位数。即“全加"

数据流级描述

写法一

sum = a ^ b ^ cin; // 本位 sum = a⊕b⊕c

co = a & b | (a ^ b) & cin; // 进位 co = a&b | (a⊕b)&c

写法二

sum = a ^ b ^ cin;

co = a & b | a & cin | b & cin;

数据流级描述

// 2022-1-25 verilog 学习

// 组合逻辑电路,不需要时钟控制,信号一来就输出

// 全加器

`timescale 1ns/10ps

module f_adder1(

a,

b,

cin,

cout,

sum); // cin进位输入,cout进位输出,sum本位

input a,b,cin;

output cout,sum;

assign sum=a^b^cin;

//assign cout=a&b | (a^b)&cin;

assign cout=(a&b) | (a&cin) | (b&cin);

endmodule

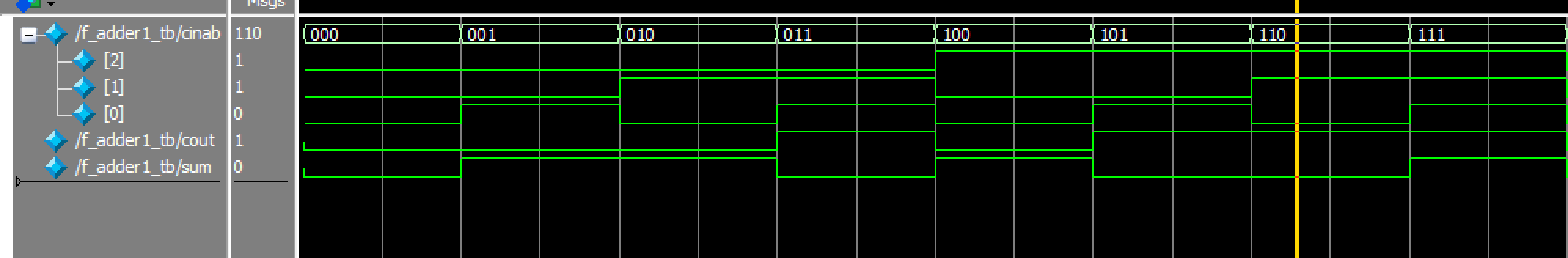

// ----testbench 测试台-------

module f_adder1_tb;

reg[2:0] cinab;

wire cout,sum;

f_adder1 f_adder1(

.a(cinab[1]),

.b(cinab[0]),

.cin(cinab[2]),

.cout(cout),

.sum(sum)

);

initial begin

cinab<=0; // 3位bit---,2^3=8种,8*10ns=80

#100 $stop;

end

always #10 cinab <= cinab+1;

endmodule

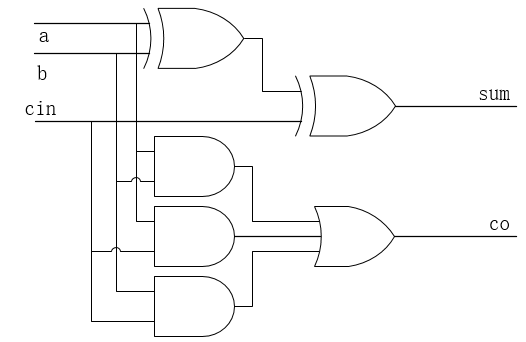

结构性描述

结构性描述

// 2022-1-25 verilog 学习

// 组合逻辑电路,不需要时钟控制,信号一来就输出

// 全加器 结构性描述

`timescale 1ns/10ps

module f_adder2(

a,

b,

cin,

sum,

cout

);

input a,b,cin;

output cout,sum;

//封装顶层

wire w1,w2,w3; // 顶层看两个半加器,或门中间的连线都是wire

// 半加器1

// 接口必须是h_adder.v中的命名:a,b,so,co

h_adder U1(

.a(a),

.b(b),

.so(w1),

.co(w2)

);

// 半加器2

h_adder U2(

.a(w1),

.b(cin),

.so(sum),

.co(w3)

);

// 或门

assign cout = w2|w3;

endmodule

//------testbench----

module f_adder2_tb;

reg[2:0] cinab;

wire cout,sum;

f_adder2 f_adder2(

.a(cinab[1]),

.b(cinab[0]),

.cin(cinab[2]),

.cout(cout),

.sum(sum)

);

initial begin

cinab<=0; // 3位bit---,2^3=8种,8*10ns=80

#100 $stop;

end

always #10 cinab <= cinab+1;

endmodule

行为级描述

// 2022-1-25 verilog 学习

// 组合逻辑电路,不需要时钟控制,信号一来就输出

// 全加器 行为级描述

`timescale 1ns/10ps

module f_adder3(

a,

b,

cin,

sum,

cout

);

input a,b,cin;

output cout,sum;

assign {cout,sum} = a+b+cin; // 进位给cout

endmodule

// testbench 测试台

module f_adder3_tb;

reg[2:0] cinab;

wire cout,sum;

f_adder3 f_adder3(

.a(cinab[1]),

.b(cinab[0]),

.cin(cinab[2]),

.cout(cout),

.sum(sum)

);

initial begin

cinab<=0; // 3位bit---,2^3=8种,8*10ns=80

#100 $stop;

end

always #10 cinab <= cinab+1;

endmodule

modelsim

本文介绍了半加器和全加器的设计原理及Verilog实现方法,包括数据流级、结构性与行为级描述,并提供了详细的代码示例。

本文介绍了半加器和全加器的设计原理及Verilog实现方法,包括数据流级、结构性与行为级描述,并提供了详细的代码示例。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?