0 英文缩写

- 环氧树脂模塑料(Epoxy Molding Compound,EMC)

- 引线框架封装(Leadframe)

- 基板封装(Substrate)

- 基板(Substrate)

- 晶圆片级芯片规模封装(Wafer Level Chip Scale Packaging)

- 重新分配层(Re-Distribution Layer)

- 硅穿孔(Through Silicon Via,TSV,也称做硅通孔)

- 锡球(Solder Balls)

- 切割胶带(Dicing Tape)

- 印刷电路板(Printed Circuit Board,PCB)

- 芯片键合(Die Bonding)

- 芯片贴装(Die Attach)

- 引线键合(Wire Bonding)

- 倒装芯片键合(Flip Chip Bonding)

- 凸块(Bump)

- SOT(Small Outline Transistor)小外形晶体管

- SOP(Small Outline Package)小外形封装

- QFN(Quad Flat No-leads Package)方形扁平无引脚封装

- BGA(Ball Grid Array)封裝,即球栅陣列封裝

- FC(Flip Chip)倒晶封装”或“倒晶封装法”

- FIWLP(Fan-inWafer-level packaging),也称WLCSP (Wafer level Chip Scale Package),扇入式晶圆级封装,也就是传统的晶晶圆级封裝

- FOWLP(Fan-out Wafer Level Packaging)无基板扇出型封装

- TSV(Through-Silicon Via)硅通孔

- SIP(System In a Package)系统级封装

- Wire Bonding:引线键合

- Flip Chip Bonding:加装芯片键合

1 背景

-

晶圆裸片易碎、线路没办法直接和外部电路连通,没办法直接作为芯片使用,需要做到:

- 给裸片上个保护壳

- 把电路接通

-

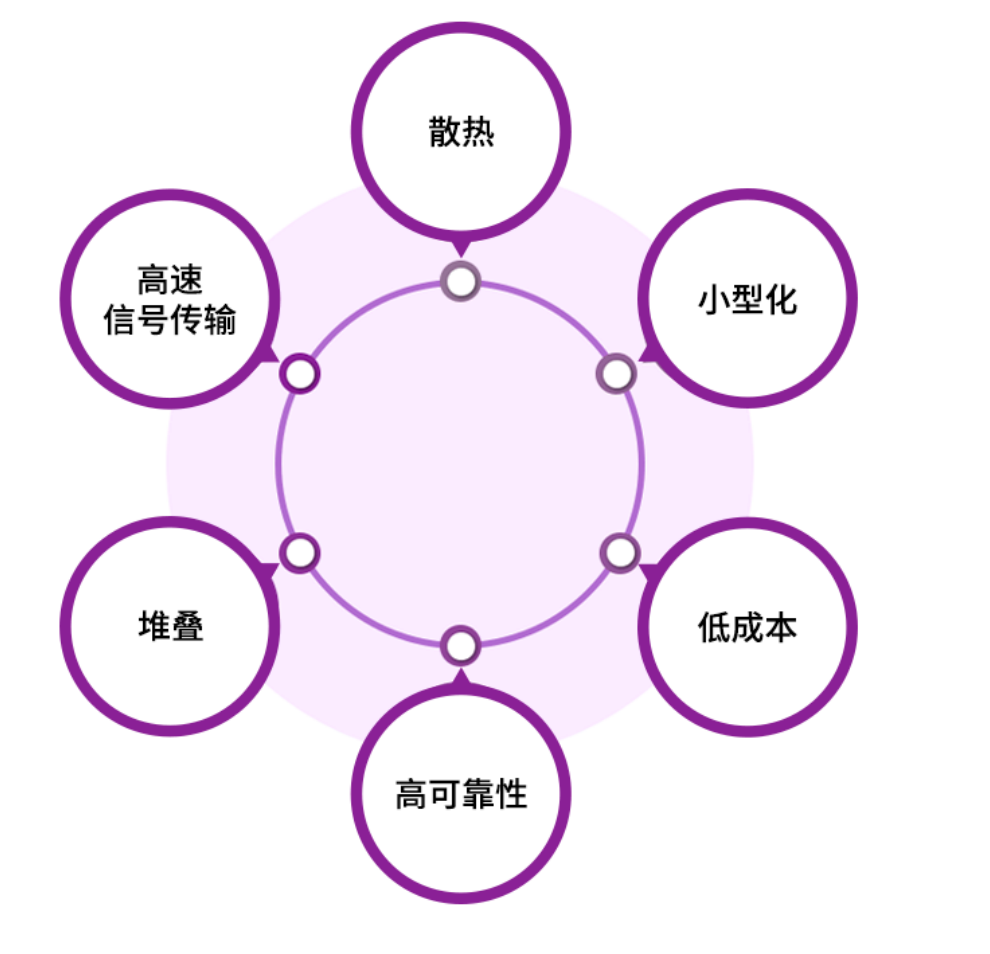

在AI时代,高算力对芯片的传输速率和信息密度有非常高的要求,为了不让封装拖芯片的后腿,工程师想方设法需要做到:

- 提高连接密度、提高传输速率

- 在保证连接质量的情况下,尽可能地降低生产成本、降低功耗、满足小型化等等需要

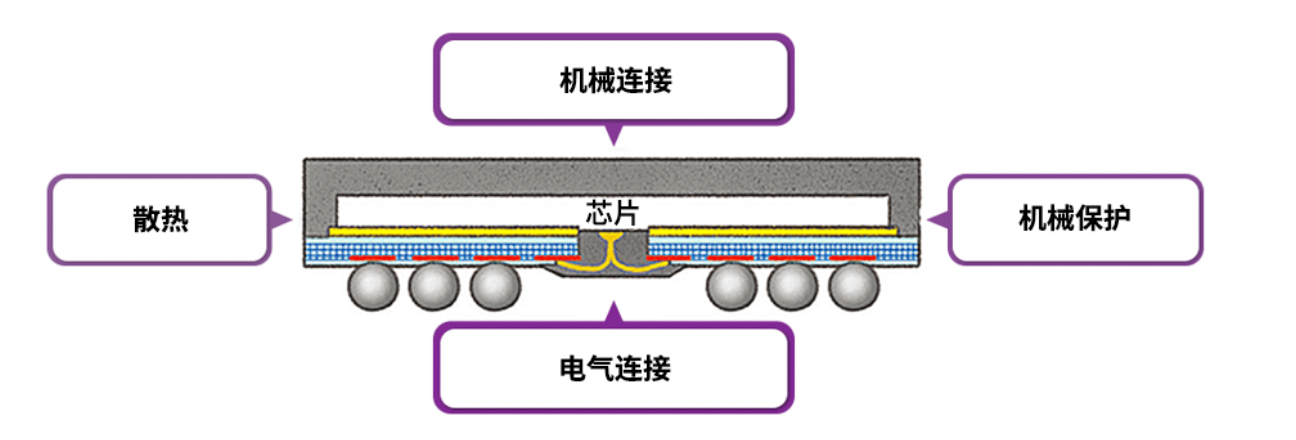

2 封装的作用

半导体封装的四个主要作用:机械保护、电气连接、机械连接和散热

- 机械保护:硅像玻璃一样,非常易碎,容易受到物理性和化学性损坏。半导体封装的主要作用是通过将芯片和器件密封在环氧树脂模塑料(EMC-Epoxy Molding Compound)等封装材料中,保护它们免受物理性和化学性损坏。

- 电气连接:封装通过芯片和系统之间的电气连接来为芯片供电,同时为芯片提供信号的输入和输出通路。

- 机械连接:需将芯片可靠地连接至系统,以确保使用时芯片和系统之间连接良好。

- 散热:如果半导体封装无法有效散热,则芯片可能会过热,导致内部晶体管升温过快而无法工作。

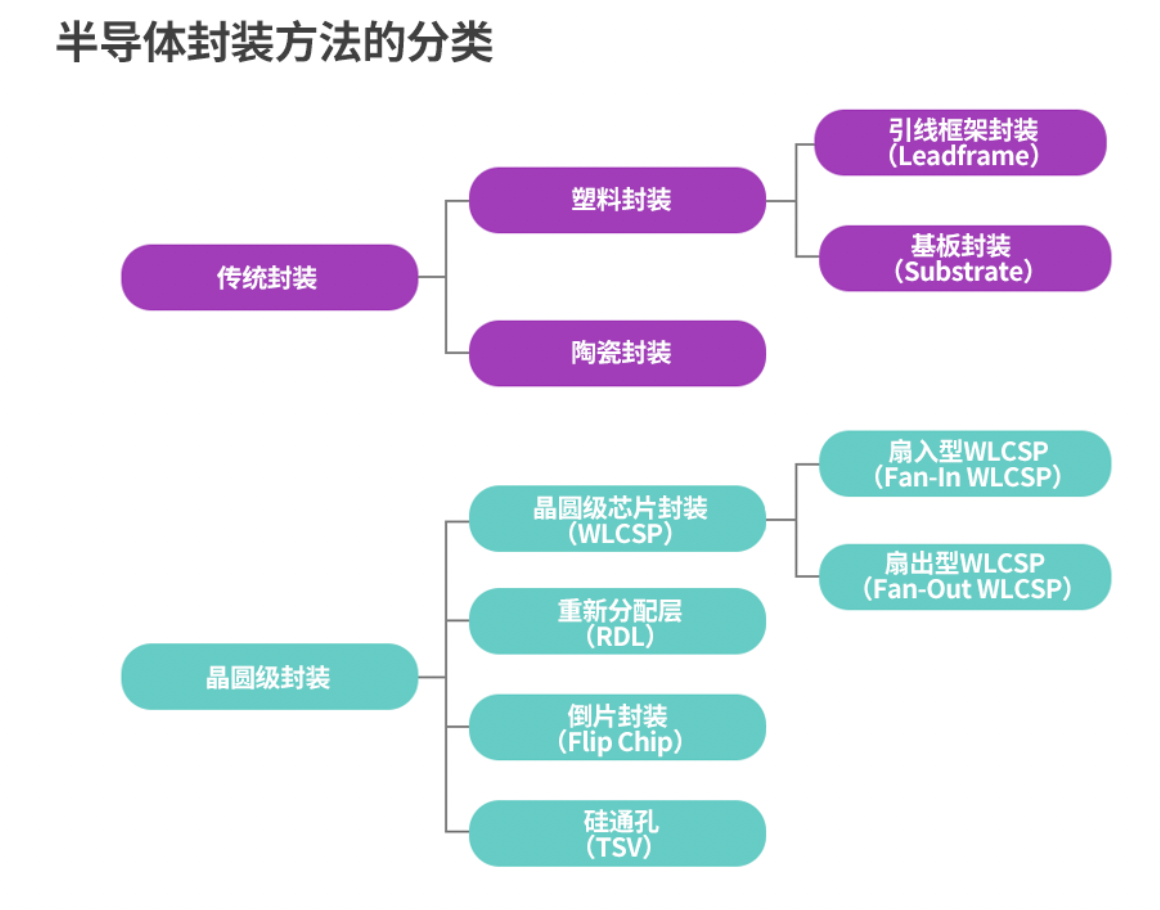

3 封装分类

分类标准:材料

根据封装材料的不同,传统封装方法可进一步细分为陶瓷封装和塑料封装。

分类标准:媒介

塑料封装中,根据封装媒介的不同,又可进一步分为引线框架封装(Leadframe)或基板封装(Substrate)。

分类标准:封装方法

根据晶圆级封装方法可进一步细分为四种不同类型:

- 晶圆级芯片封装(WLCSP),可直接在晶圆顶部形成导线和锡球(Solder Balls),无需基板;

- 重新分配层(RDL),使用晶圆级工艺重新排列芯片上的焊盘位置,焊盘与外部采取电气连接方式;

- 倒片(Flip Chip)封装,在晶圆上形成焊接凸点2进而完成封装工艺;

- 硅通孔(TSV)封装,通过硅通孔技术,在堆叠芯片内部实现内部连接。

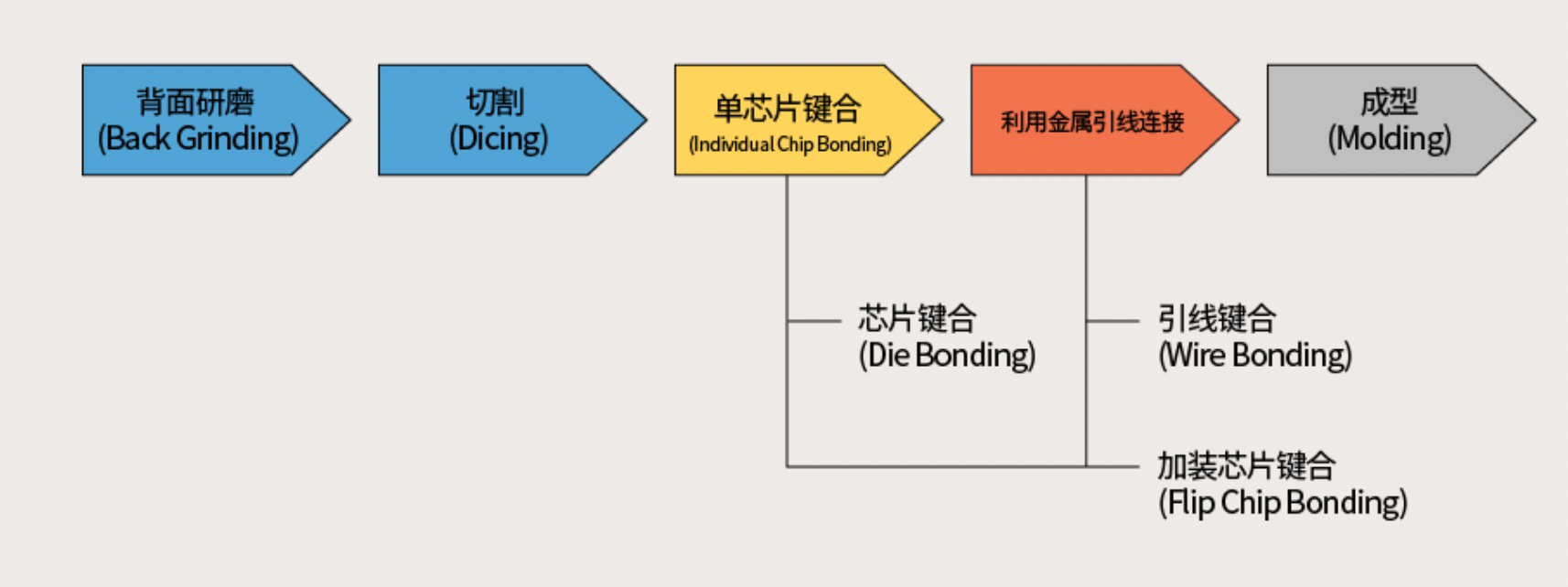

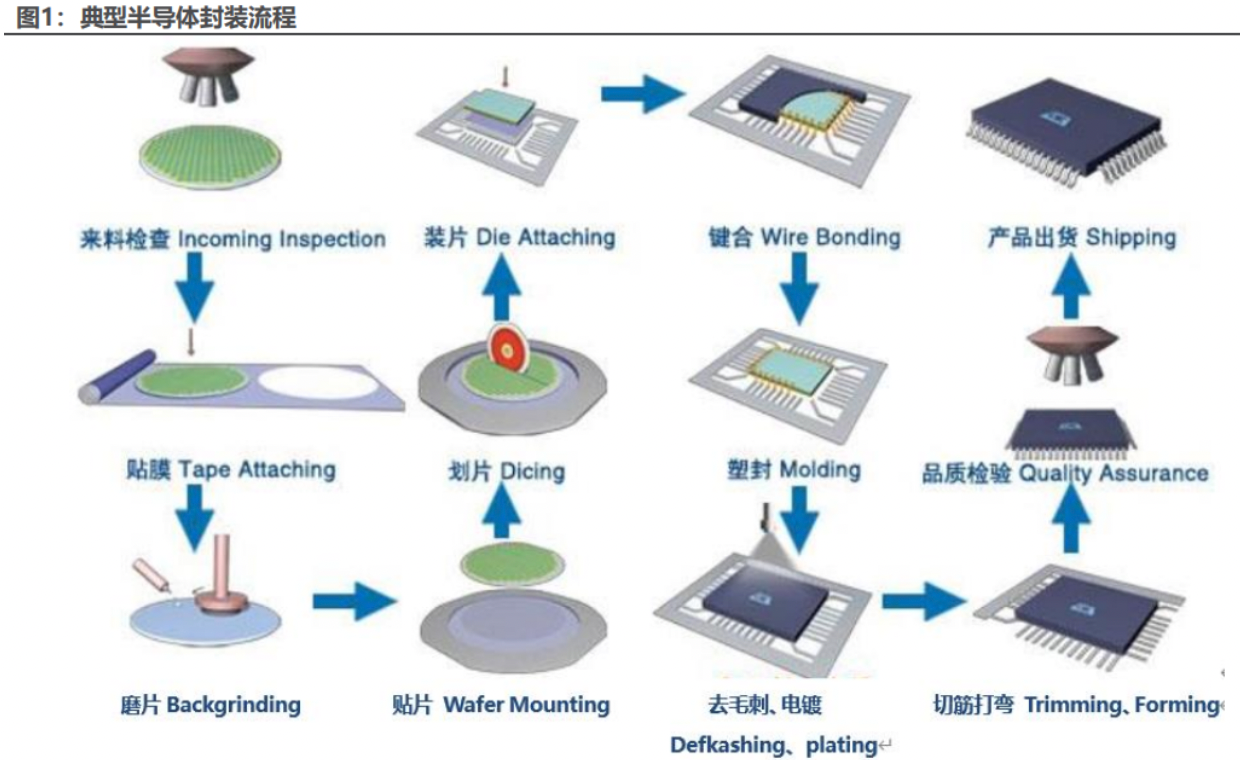

4 封装工艺步骤

封装工艺包含背面研磨(Back Grinding)、划片(Dicing)、芯片键合(Die Bonding)、引线键合(Wire Bonding)及成型(Molding)等步骤。

背部研磨

封装厂从晶圆厂那里得到的晶圆还是比较厚的,因为晶圆太薄的话易碎。封装厂需要把晶圆研磨到合适的厚度;

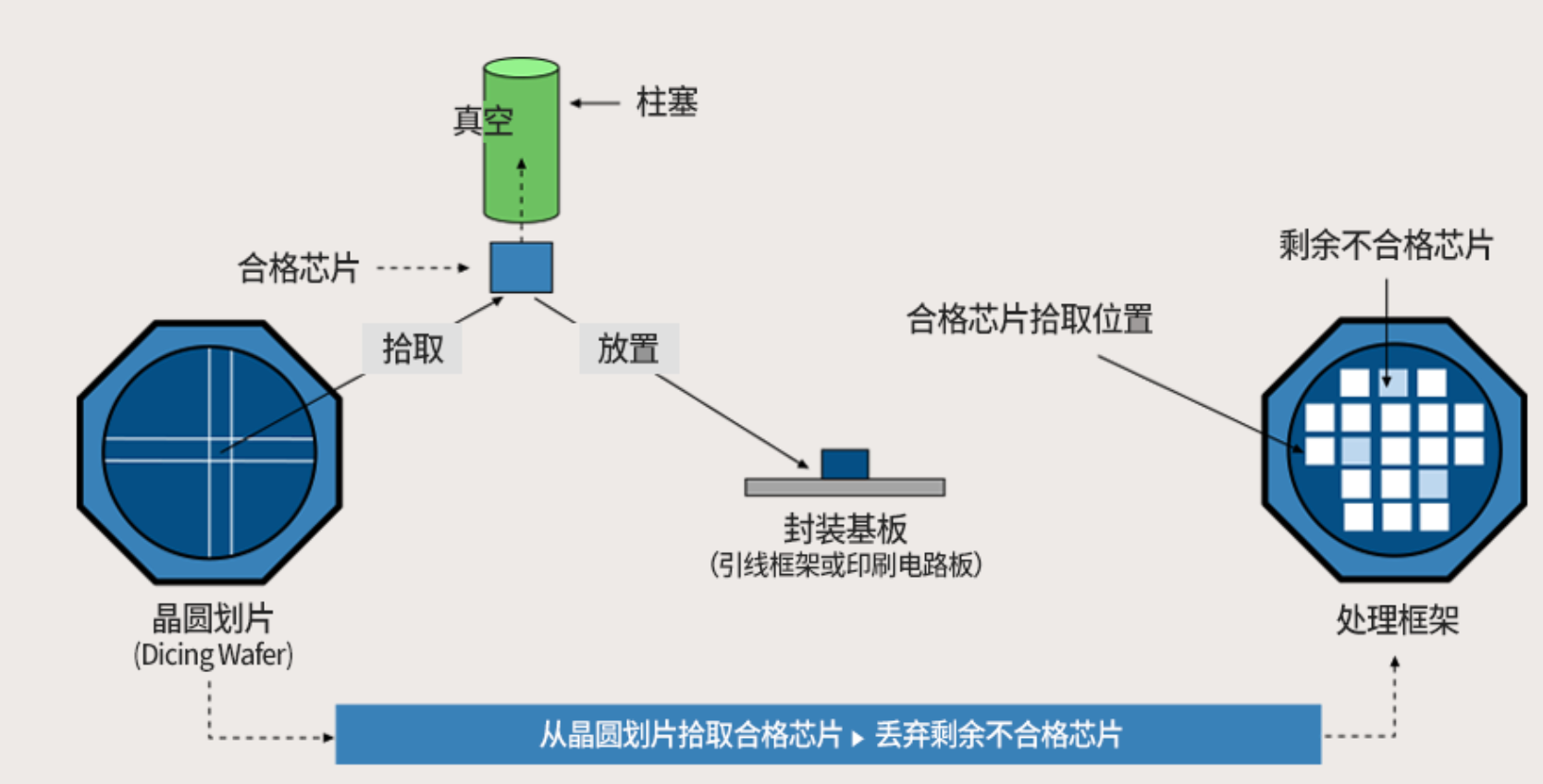

划片、拾取和放置

- 划片:切割得到裸片,通过划片,把一块晶圆切割成数百个芯片裸片,这时候切割出来的芯片会附着在一层胶带上。

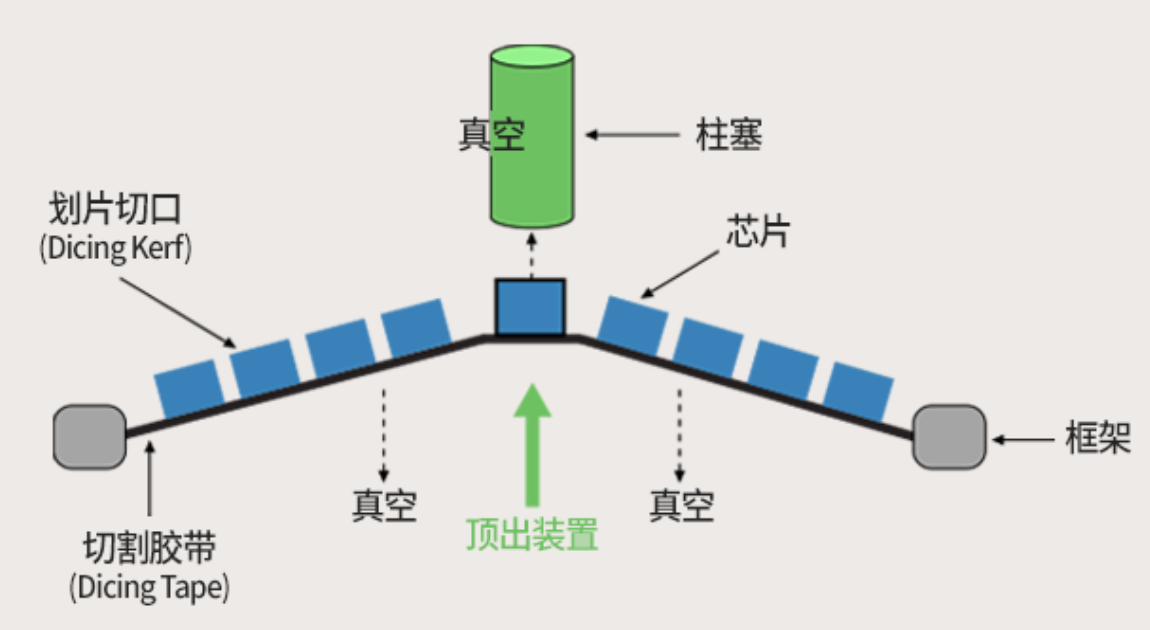

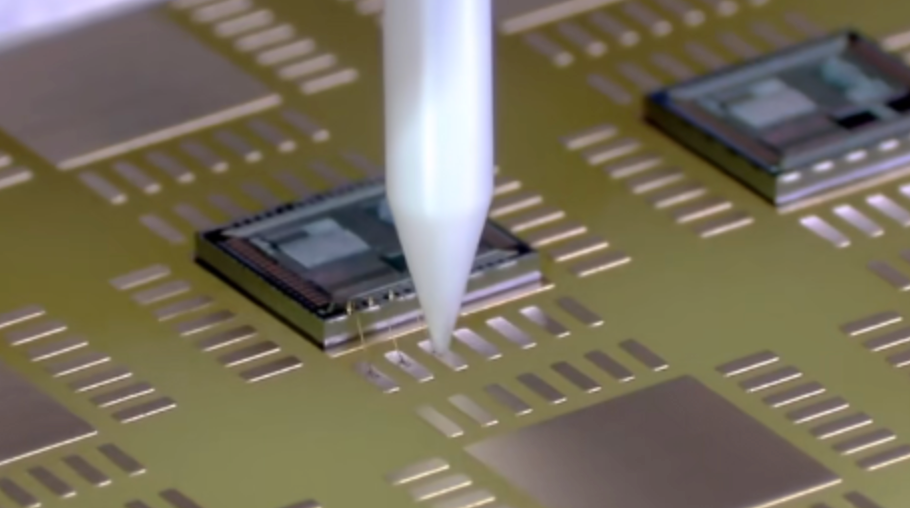

- 拾取与放置:逐个移除附着在切割胶带上数百个芯片的过程称为“拾取”。使用柱塞从晶圆上拾取合格芯片并将其放置在封装基板表面的过程称为“放置”。这两项任务合称为“拾取与放置”,均在固晶机(用于芯片键合的装置)上完成。

完成划片工艺之后,芯片将被分割成独立模块并轻轻附着在切割胶带(Dicing Tape)上。通过顶出装置(用于从切割胶带下方顶起芯片的顶针)对目标芯片施加物理力,使其与其他芯片形成轻微步差,从而轻松拾取芯片。顶出芯片底部之后,可使用带有柱塞的真空吸拾器从上方拉出芯片。

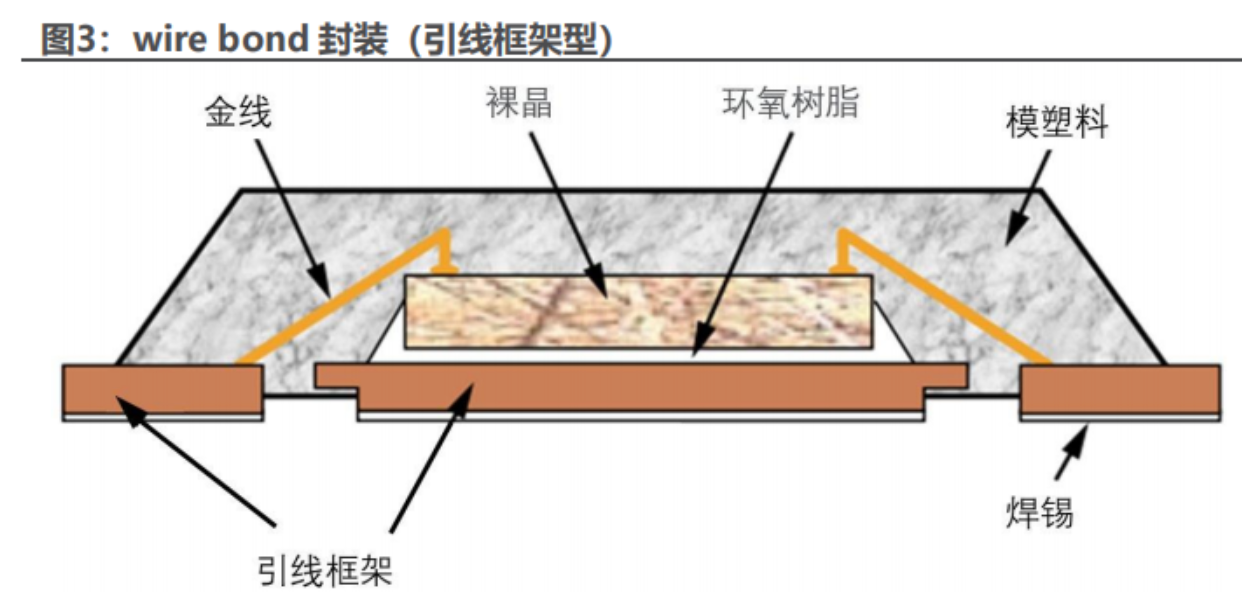

键合

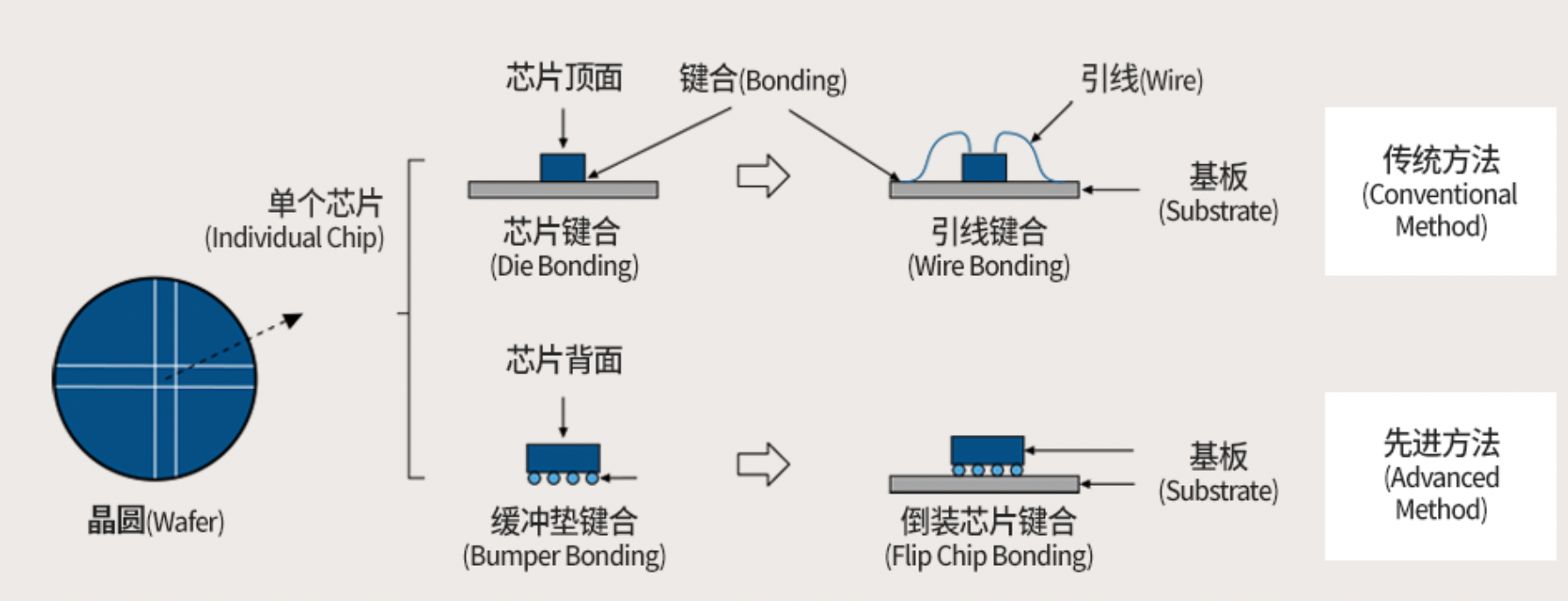

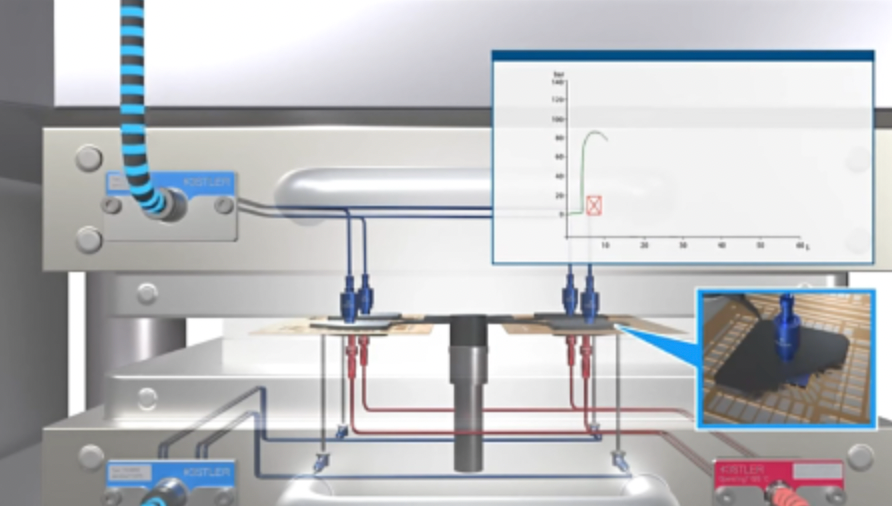

“键合”是指将晶圆芯片固定于基板上。就像发动机用于为汽车提供动力一样,芯片键合技术通过将半导体芯片附着到引线框架(Lead Frame)或印刷电路板(PCB, Printed Circuit Board)上,来实现芯片与外部之间的电连接。

-

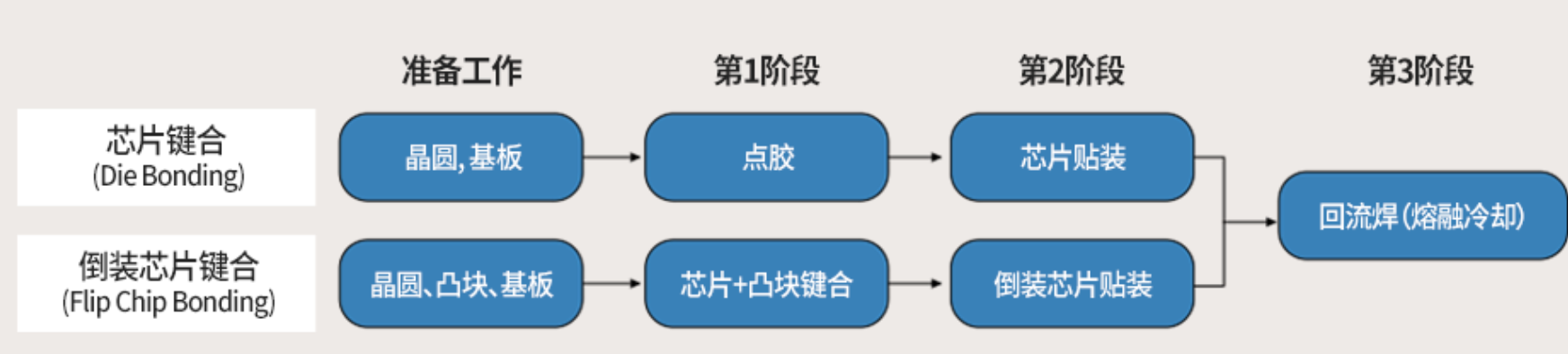

传统方法方法步骤

-

首先完成芯片键合(Die Bonding)或芯片贴装(Die Attach)

-

然后引线键合(Wire Bonding)

-

下图为引线框架示意图

下图为引线键合

- 先进方法

- 倒装芯片键合(Flip Chip Bonding)(IBM于60年代后期开发)倒装芯片键合技术将芯片键合与引线键合相结合,并通过在芯片焊盘上形成凸块(Bump)的方式将芯片和基板连接起来。

芯片键合步骤图:

塑封

将键合完成的引线框架放在模具中,通过环氧树脂等材料对芯片完成塑封。

5 发展路径的核心思路

从第一性原理出发,封装要解决的其实主要就是这两个问题:

- 怎么封:能保护芯片,又要满足如下条件

- 顺应设备小型化的趋势

- 兼顾散热、降低功耗

- 降低成本

- 怎么连接:提高芯片和外部电路之间的信息传输密度,提高传输速率。

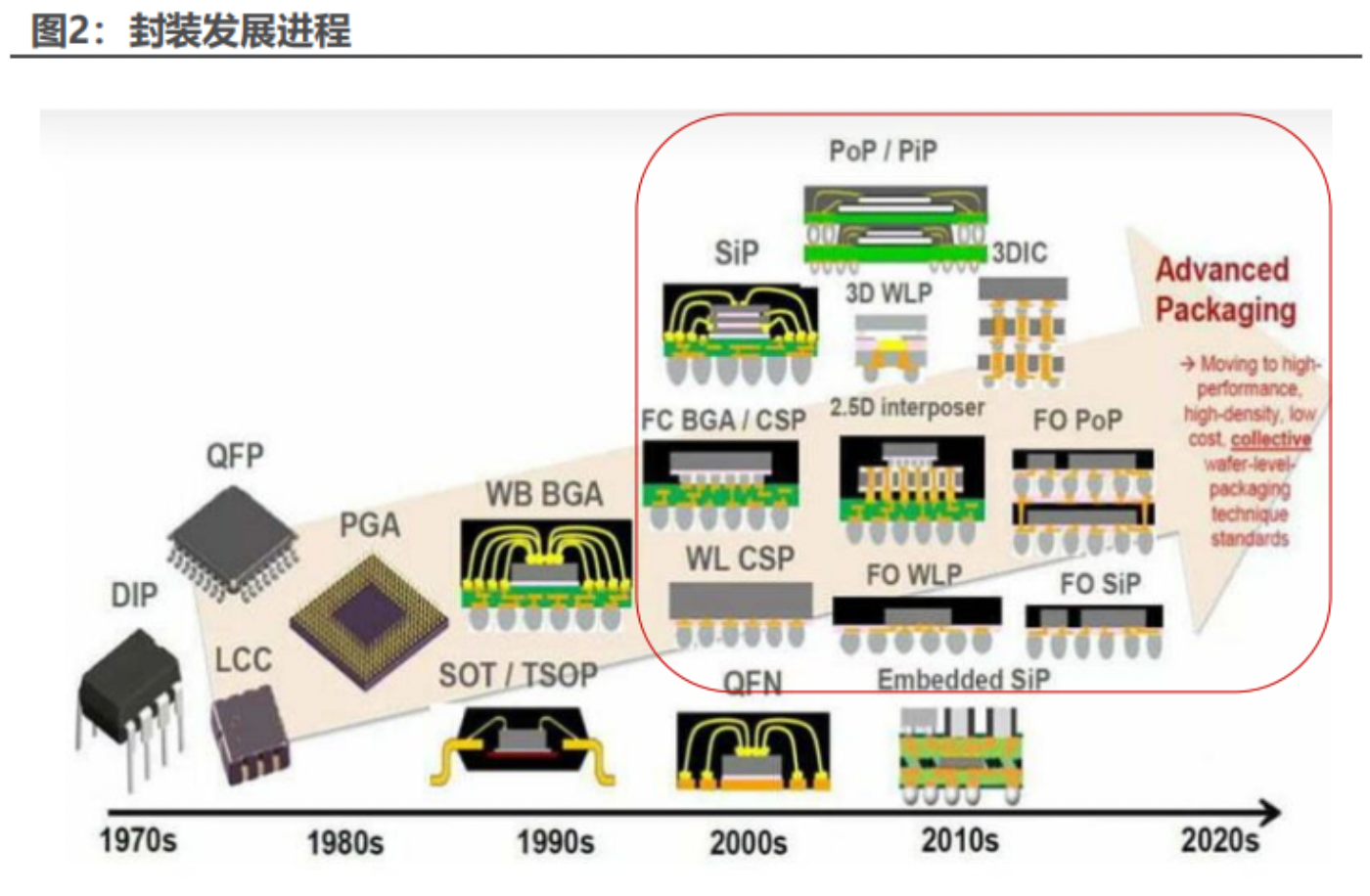

围绕着这两个核心目的,工程师们想出了五花八门的办法,并且技术不断升级,这也就形成了现在各种各样的封装技术:

- 从传统封装

- SOT(Small Outline Transistor小外形晶体管)

- QFN(Quad Flat No-leads Package方形扁平无引脚封装)

- BGA(Ball Grid Array封裝,即球栅陣列封裝)等)

- 向先进封装转变

- FC(Flip Chip倒晶封装”或“倒晶封装法”)

- FIWLP(Fan-inWafer-level packaging),也称WLCSP (Wafer level Chip Scale Package),扇入式晶圆级封装,也就是传统的晶晶圆级封裝

- FOWLP(Fan-out Wafer Level Packaging)无基板扇出型封装

- TSV(Through-Silicon Via)硅通孔

- SIP(System In a Package)系统级封装

封装技术的发展非常快速,新的封装方法和技术不断涌现,有时会出现重叠和交叉的情况。

因此,在实际应用中,封装技术的分类可能不是非常清晰和一致,而是根据具体的应用需求和技术发展进行灵活调整和组合。

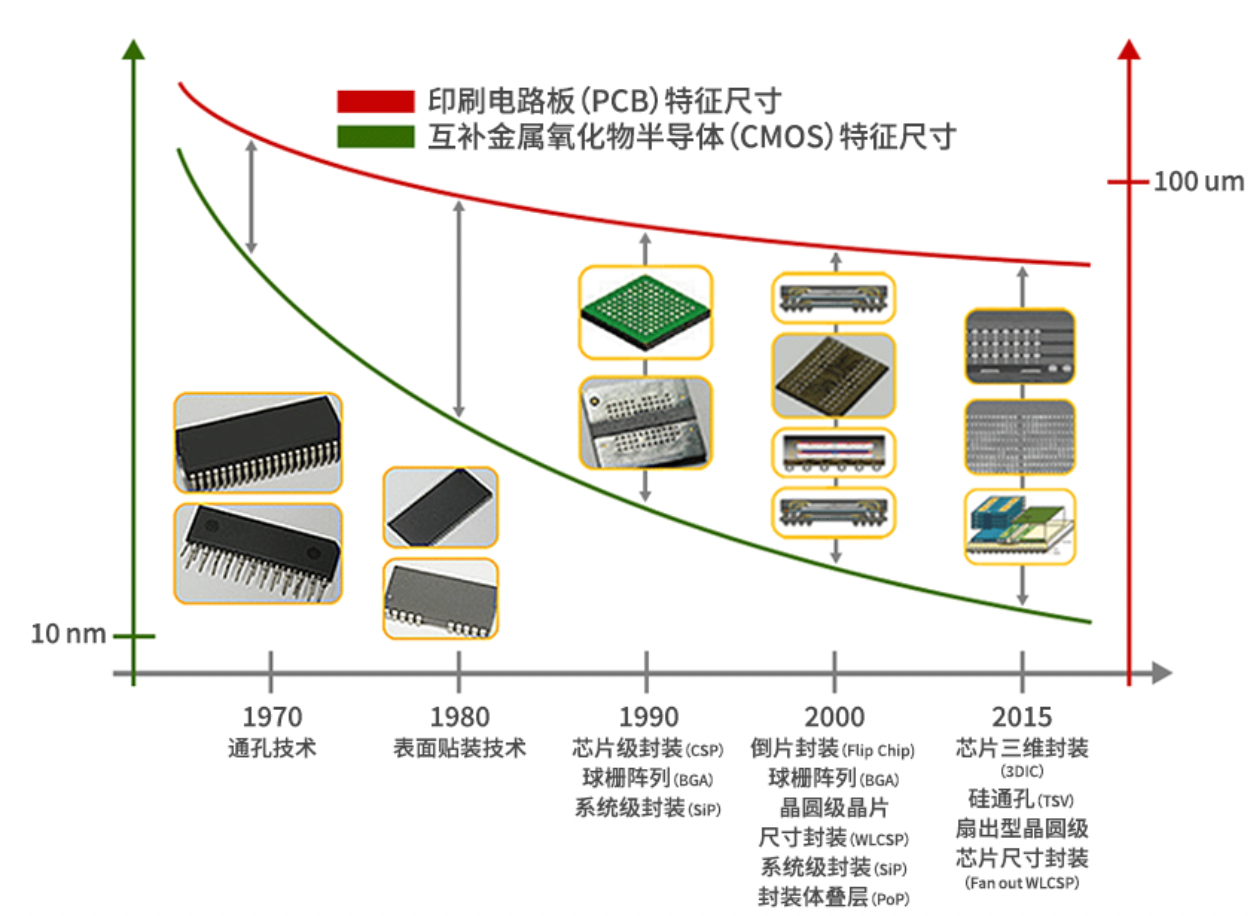

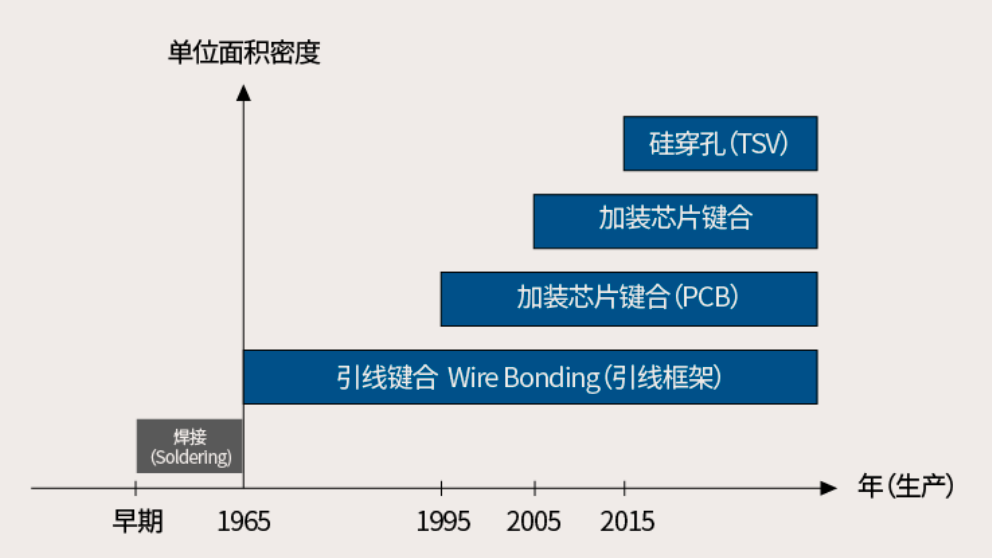

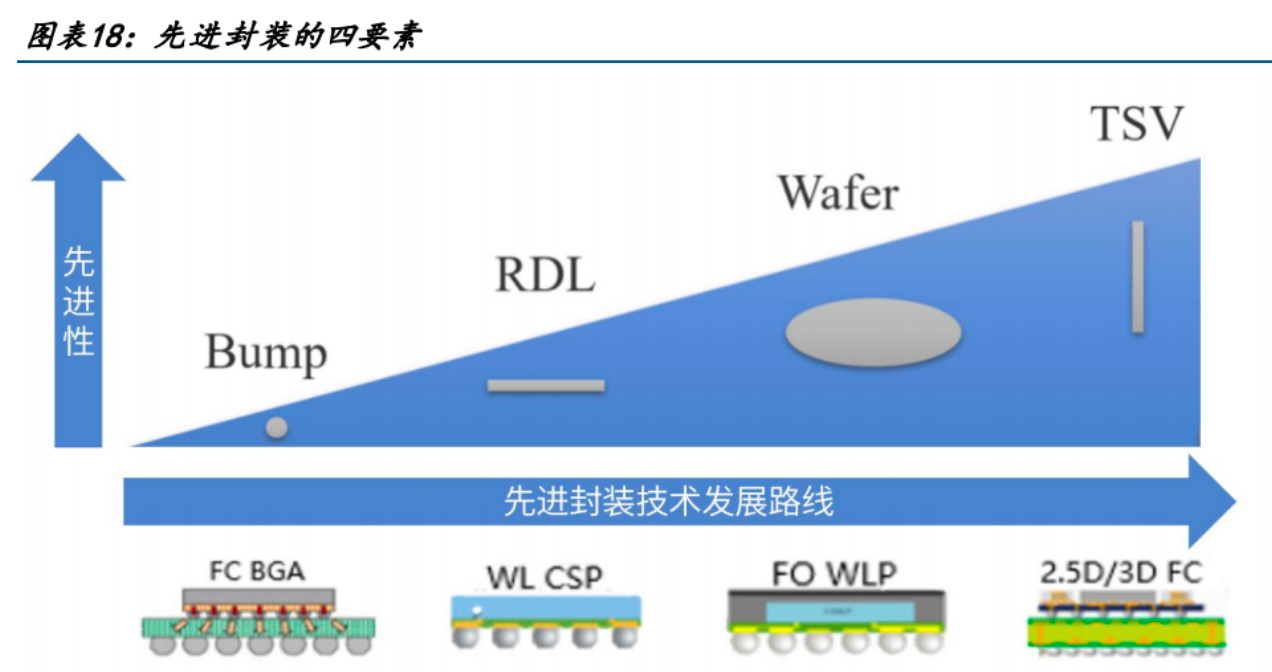

但是万变不离其宗,围绕这两个核心问题(怎么封、怎么链接),把封装的技术路径,大致分为四个阶段:

- (第一阶段)裸片贴装阶段,代表的连接方式是引线键合,也就是我们刚刚提到的传统封装

- (第二阶段)倒片封装阶段,代表的连接方式是焊球或者叫凸点(Bumping)

- (第三阶段)晶圆级封装阶段,代表的连接方式是RDL重布线层技术

- (第四阶段)2.5D/3D封装阶段,代表的连接方式是TSV硅通孔技术、chiplet封装技术

每一代技术之间的本质区别,就是芯片和电路的连接方式的区别。连接方式引发的技术迭代也可以看做为键合法发展史:

- 引线键合(Wire Bonding)

- 倒装芯片键合(Flip Chip Bonding)

- 硅穿孔(TSV)

正如背景第三条所述这就是我们现在看到的先进封装。

参考文献

[1] 华为,Application Defined On-chip Networks for Heterogeneous Chiplets: An Implementation Perspective

[2] 华为3D堆叠专利解读,CN201980099842

[3] 新思科技,3D Die-to-Die Interconnect Testing Challenges and the Need for an IEEE Standard

[4] 新思科技,OpenHBI:小芯片互联的理想接口标准

[5] 西安电子科技大学,田文超团队论文,Using Chiplet Encapsulation Technology to Achieve Processing-in-Memory Functions

[6] CADENCE PCB SOLUTIONS,An Introduction to Die-to-Die Interconnects

[7]《电子工程专辑》2022年7月刊,黄烨锋,这次不说chiplet的好,来谈谈chiplet的“坏”

[8]《电子工程专辑》2022年8月刊,黄烨锋,先进封装的现在和将来,价值链的未来重心

[9] 差评君,苹果的新芯片,真就是用两块芯片粘起来的

[10] 知乎Vampire,片内互联技术发展概述

[11] Intel,What Are PCIe 4.0 and 5.0?

[12] 半导体行业观察,OpenFive发布第八代Die to Die IP,采用Interlaken协议,性能高达1.2Tbps

[13] [并非无解!先进封装技术,能打破国产芯片的困局吗?14nm+14nm=7nm??光刻机被封锁,但是还能另辟蹊径!【深度报告】_哔哩哔哩_bilibili](

文章探讨了封装技术在保护和连接芯片中的关键作用,包括机械保护、电气连接和散热。介绍了封装分类如陶瓷封装、塑料封装、引线框架封装、基板封装等,以及晶圆级封装的四个类型。重点讲述了封装工艺步骤,如背面研磨、划片、键合(如DieBonding、WireBonding、FlipChipBonding)和塑封。文章还梳理了封装技术的发展路径,从传统封装到先进封装,如SOT、QFN、BGA、FC、FIWLP、FOWLP和TSV等,以及芯片连接方式的演变史。

文章探讨了封装技术在保护和连接芯片中的关键作用,包括机械保护、电气连接和散热。介绍了封装分类如陶瓷封装、塑料封装、引线框架封装、基板封装等,以及晶圆级封装的四个类型。重点讲述了封装工艺步骤,如背面研磨、划片、键合(如DieBonding、WireBonding、FlipChipBonding)和塑封。文章还梳理了封装技术的发展路径,从传统封装到先进封装,如SOT、QFN、BGA、FC、FIWLP、FOWLP和TSV等,以及芯片连接方式的演变史。

4786

4786

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?