目录

一、前言

以下为个人学习笔记,如有疏漏,请大家指正补充~~

二、Timer模块介绍

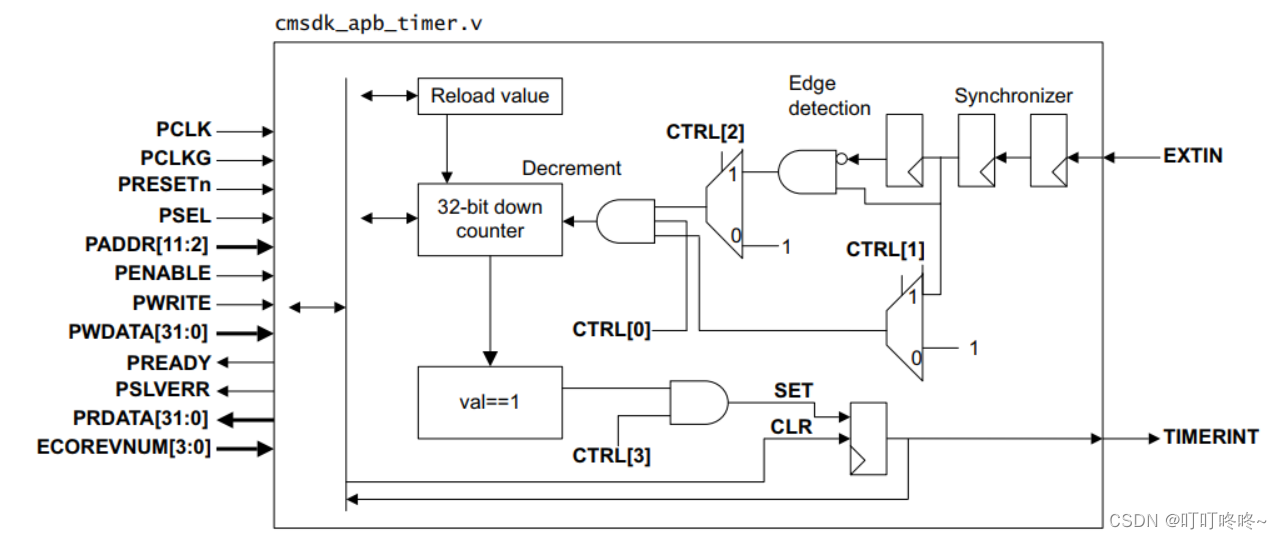

APB Timer是一个简单的下行计数器,包括一个32位计数器和一组比较器,可以实现多种计时功能。包括生成一次性中断或者定时中断。Timer包括控制寄存器、计数寄存器、比较寄存器和状态寄存器等,通过对这些寄存器的编程,可以实现不同的定时和计时功能。

1、在Timer工作时,当计数器的值达到比较器的值时,APB Timer会发出一个中断信号TIMERINT,这个信号会被保持,直到INTCLEAR寄存器写入时清除;

2、双触发器采样(两级同步),避免亚稳态的产生:因为EXTIN作为外部信号和PCLK大概率是两个时钟域,所以为了两个信号一起做逻辑,所以最好经过两级同步实现,同步为PCLK时钟;两级同步要求:外部时钟EXTIN必须比APB时钟PCLK的一半慢;详解请参考:

【 FPGA 】稳态与亚稳态小结_亚稳态和glitch的区别![]() https://blog.csdn.net/Reborn_Lee/article/details/84899344

https://blog.csdn.net/Reborn_Lee/article/details/84899344

3、寄存器:

CTRL: CTRL[3] 中断的ENABLE;CTRL[2] 选择EXTIN作为CLK;CTRL[1] 选择EXTIN作为ENABLE;CTRL[0] Timer的ENABLE; VALUE:当前的值;RELOAD:Timer重新加载的值;INTSTATUS、INTCLEAR:中断的信号线,read中断、writeclear;PIDx、CIDx:一些状态寄存器;

三、验证环境初步搭建(1)

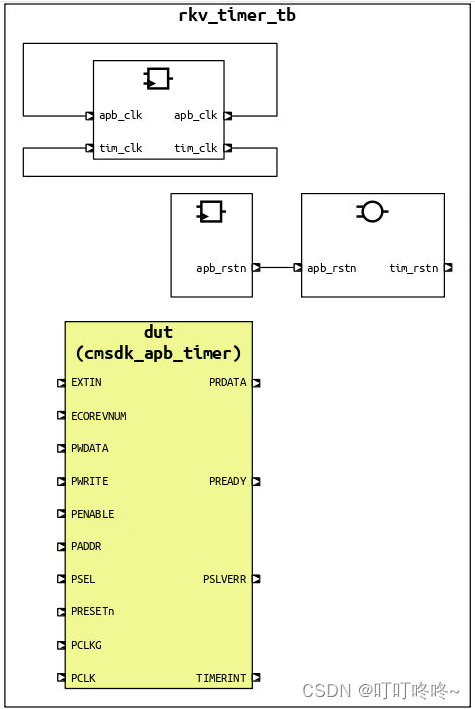

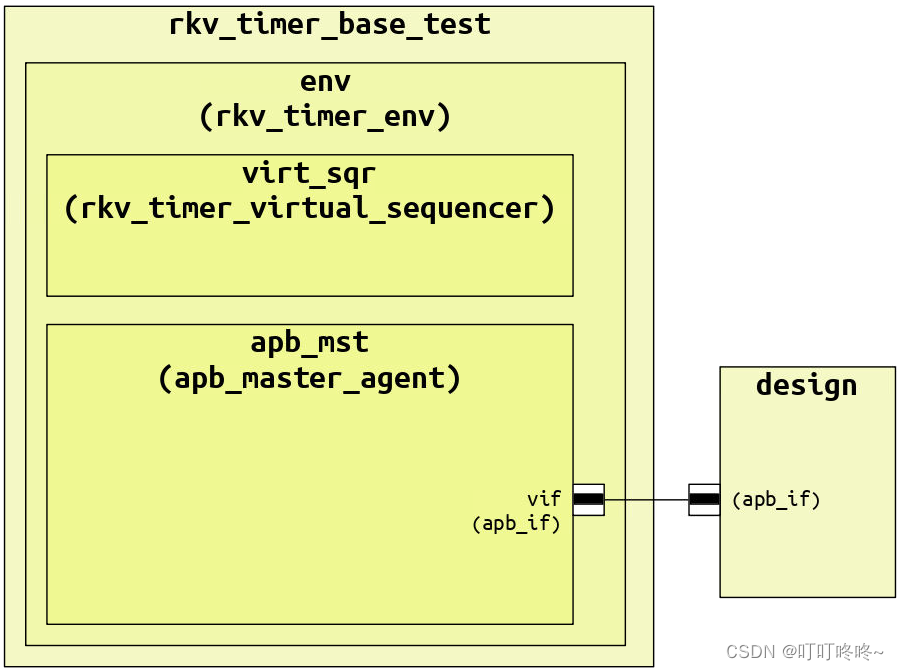

按照框架创建文件;TB下例化design、apb_if、timer_if,接口后面连接;注意Timer的clk可以由apb_clk提供,也可以由EXTIN提供;根据脚本Makefile,编译后跑起仿真;利用工具DVT查看验证基本的验证环境结构;

以上只是搭建了基本的结构,没有与DUT做交互,也没有产生和发送激励,相关的激励都将在接下来完成。

971

971

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?