数字ic设计流程

集成电路设计方法分类

- 全定制设计流程

- 基于门阵列的设计

- 基于现场可编程阵列FPGA的设计

- 基于标准单元的设计

全定制流程

工程师从晶体管开始设计,完成电路设计、仿真和版图设计的方式。

精度高,最大程度优化芯片性能,不会浪费芯片资源

花费更多的人力和时间成本

对性能、功耗要求极高的高端产品,适用于高性能微处理器,高精度模拟电路

基于门阵列的设计方法

门阵列芯片在生产时已经包含触发器、逻辑门等基本电路,只需要客户完成器件之间的布线。布线方式为物理布线,通过光刻等技术实现互联

适用于中等复杂程度的集成电路设计,快速生产和较低成本

现场可编程FPGA的设计

用户使用硬件描述语言来完成连线编程操作。适合小批量生成和开发

适用于原型(初步)设计、小批量生成、快速迭代快速测试

基于标准单元设计

设计师使用硬件描述语言完成设计,这个描述随后会转换为标准单元的实例,并且进行逻辑优化

适用于复杂度高的自定义集成电路设计

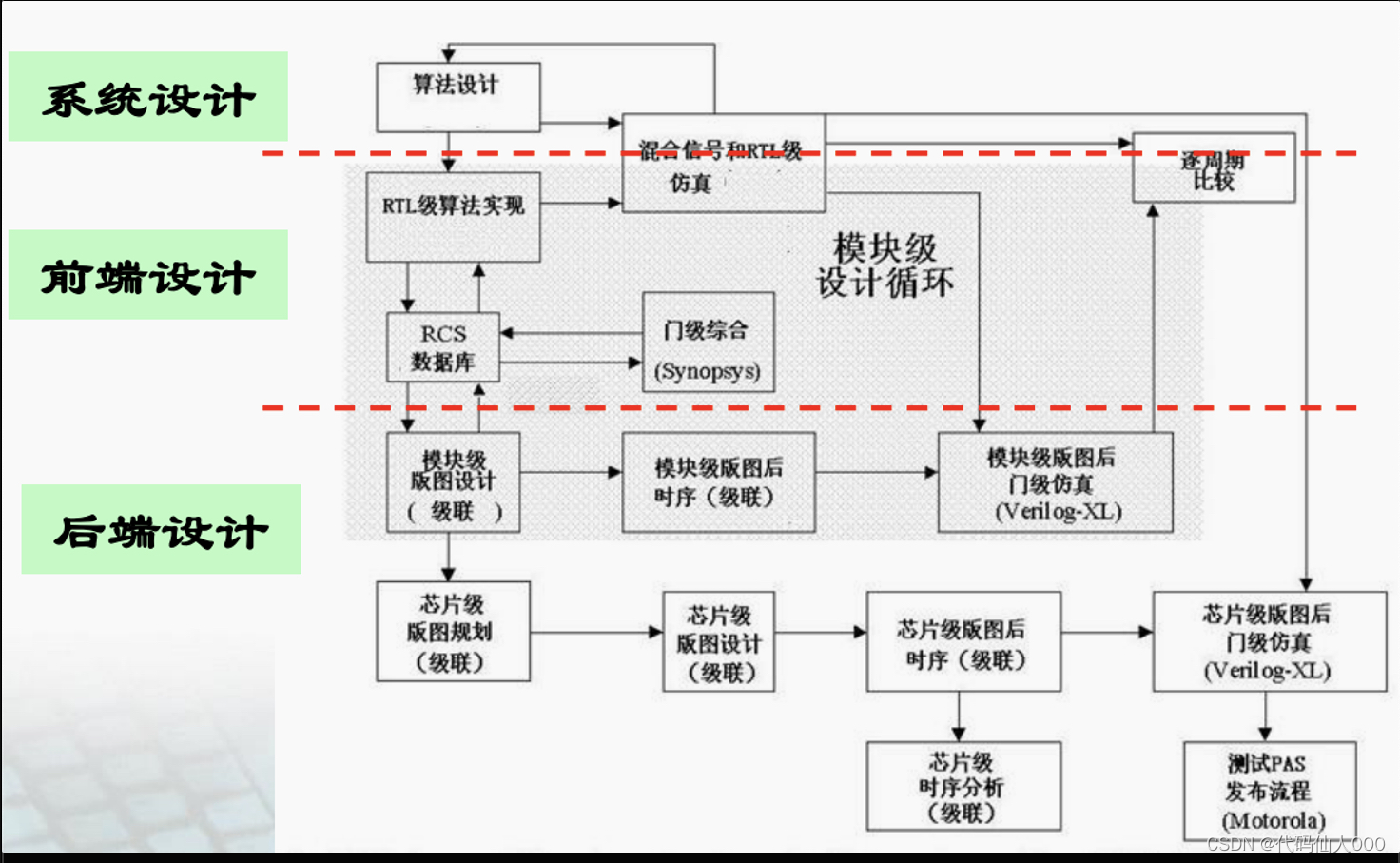

集成电路设计流程

前端:RTL级算法实现,门级综合

后端:版图设计、时序分析、版图级仿真

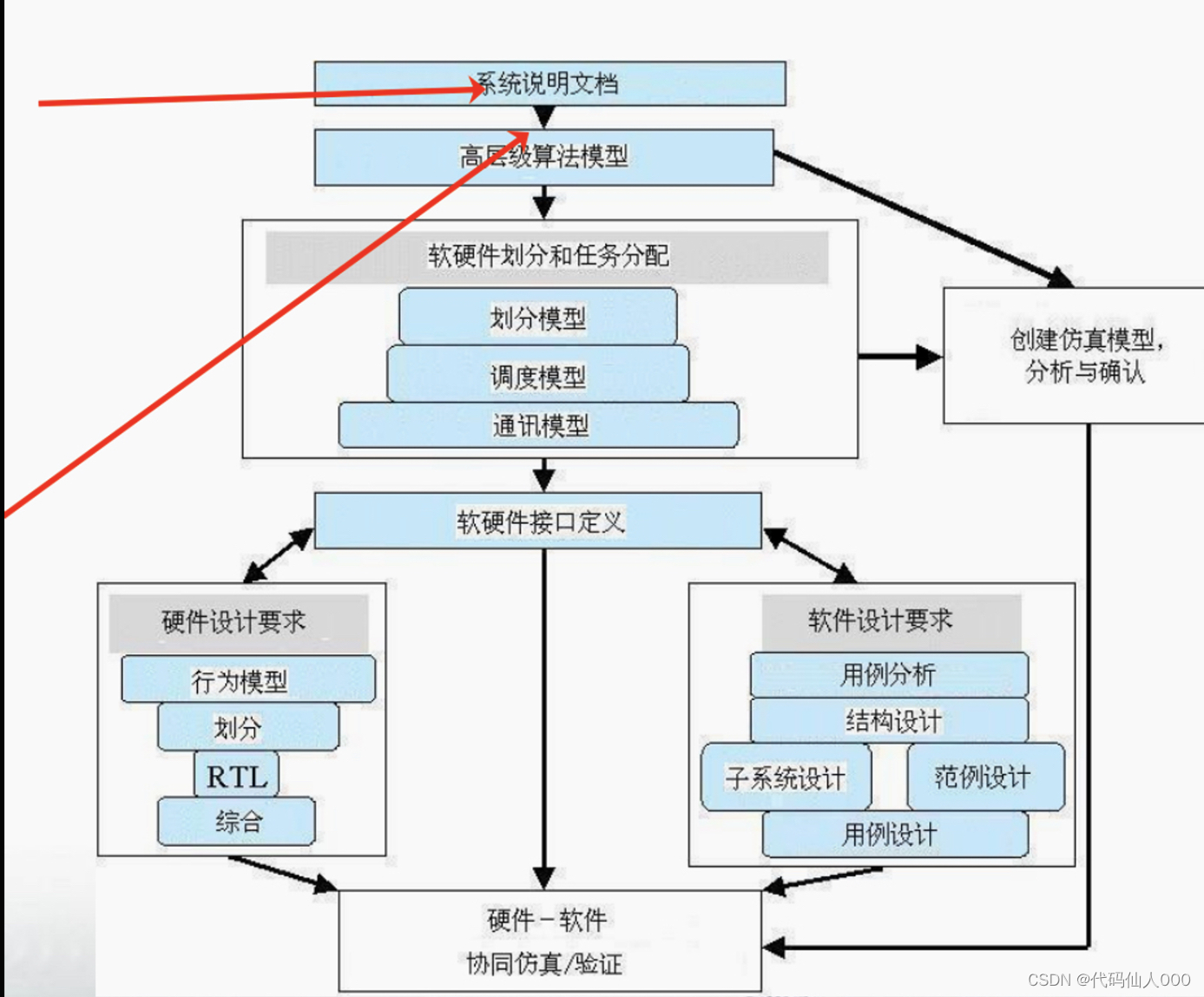

软/硬件协同设计

设计适用范围

适合复杂性高,要求硬件与软件紧密集成,PPA高度优化的芯片设计中

简化流程

- 出系统说明文档

- 使用高级建模语言创建系统的初步模型,并根据功能进行软硬件分类

- 确定好分工、接口设计后,软件和硬件部门同时开发

- 软硬件进行联合调试和测试,部署到FPGA或者完成ASIC设计

-

设计流程图

逻辑综合

综合 = 翻译+ 优化+布局

翻译:将RTL 转化为 门电路

优化:优化门电路结构

文件格式

SDF standard delay format 存储电路中的时序数据

GDSII Graphical Data System II 存储集成电路设计的图形布局信息

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?