操作系统小议

背景知识

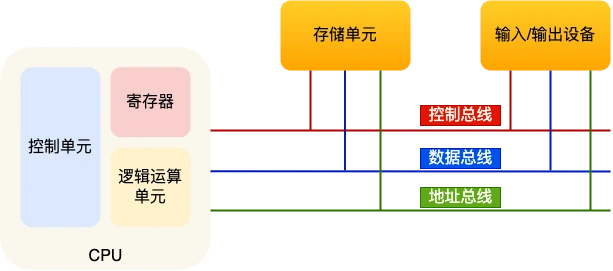

总线

总线是用于 CPU 和内存以及其他设备之间的通信,总线可分为 3 种:

当 CPU 要读写内存数据的时候,一般需要通过下面这三个总线:

首先要通过「地址总线」来指定内存的地址;

然后通过「控制总线」控制是读或写命令;

最后通过「数据总线」来传输数据;

一、线路位宽与 CPU 位宽

结论:

操作系统的位数,指的是线路位宽,也就是指地址总线的位数。

俗称大家说的32位和64位电脑

通常说的操作系统的位数,指的是地址总线的位宽,32位操作系统地址总线根数就是32。而线路位宽是与内存紧密相关的,因为内存是通过地址总线来进行寻址的。

CPU位宽与线路位宽没有直接的联系。

1.1 CPU位宽。

CPU位宽是指一次可以计算数据的bit数。有CPU在计算时,数据需要先保存在寄存器中,因此CPU位宽一般就是指寄存器的位数。如32CPU一次可以计算32bit的数据,64位CPU一次可以计算64bit的数据。

要 CPU 操作 4G 大的内存,那么就需要 32 条地址总线,因为 2 ^ 32 = 4G。

1.2 线路位宽

操作系统位宽一般就是指线路位宽。程序在执行时,需要通过地址总线去内存中找到对应数据或指令的地址。线路位宽就是指地址总线有多少根。

二、解释

首先,要明白内存是储存单元的集合,每个储存单元对应一个物理地址 ,目前大多数计算机都是按照字节(Byte)编址的,8bit占用一个物理地址,也就是说一个物理地址对应1Byte的内存。

每根地址总线可以高电平(对应1)或低电平(对应0),相当于一根地址总线对应一个bit,因此,若是32根地址总线,那么就可以得到一个32bit的地址,地址的范围为0 ~ 2^32,由于每个地址对应1Byte的数据,因此内存的大小为 2^32 Byte,也就是4GB。

这就是为什么32位操作系统,一般内存最大就是4GB,因为内存大于4GB,操作系统也没法一次寻址,内存就显得有些浪费。

顺便再说一下,为什么不同的操作系统,C/C++ 指针变量的大小不一样?比如32位操作系统中,指针变量大小为4 Byte,64位系统为8 Byte。

这是因为指针的值的含义就是内存地址,在32位系统中,寻址的最大值为2^32,地址编码为0 ~ 2^32,刚好可以用一个32bit的数据来表示,也就是4 Byte。同样对于64位操作系统,寻址的最大值为2^64,需要用一个64 bit的数表示,也就是8 Byte。

线路位宽与内存的联系

程序在运行的时候,需要先加载到内存中,然后CPU根据地址总线去读取内存中的指令或数据。内存中的地址已byte进行编号,比如第一个byte编号为0x01,第二个地址编号为0x02 。。。如果是32为地址总线,那么可以得到一个32位的二进制数据,范围为 0 ~ 2^32, 因此32位操作操作系统(32位线宽)可以寻址的地址范围为4GB (每个地址都对应1Byte的内存)。所以说32位的操作系统最大寻址的内存是4GB。

3309

3309

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?