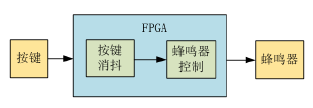

一、基础知识

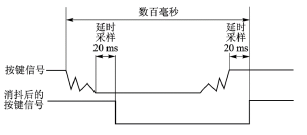

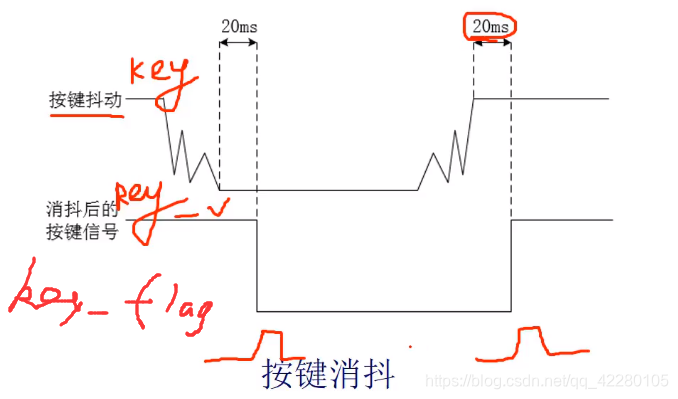

- 按键消抖此程序采用20ms延时,当按键信号平稳20ms时开始。

- 消抖20ms在程序中采用倒计时的方式。

- 50MHz——时钟,20ns——周期 ,计算20ms 要计算到10的6次方。

二、程序

top_key_beep

module top_key_beep(

input clk,

input rst_n,

input key,

output beep

);

wire key_value ;

wire key_flag;

// 程序例化

key_deounce u_key_deounce(

.clk (clk),

.rst_n (rst_n),

.key (key),

.key_value (key_value),

.key_flag (key_flag)

);

beep_control u_beep_control(

.clk (clk),

.rst_n (rst_n),

.key_value (key_value),

.key_flag (key_flag),

.beep (beep)

);

endmodule

key_deounce

module key_deounce(

input clk,

input rst_n,

input key,

output reg key_value,

output reg key_flag

);

reg [19:0] cnt; // 50MHz 时钟 20ns 周期 ;计算20ms 要计算到10的6次方

reg key_reg;

// 主代码

always @ (posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt <= 20'd0;

key_reg <= 1'b1;

end

else begin

key_reg <=key;

if(key_reg != key)begin

cnt <= 20'd100_0000;

end

else begin

if(cnt > 20'd0)

cnt <= cnt - 1'b1;

else

cnt <= 20'd0;

end

end

end

always @ (posedge clk or negedge rst_n)begin

if(!rst_n)begin

key_value <= 1'b1;

key_flag <= 1'b0;

end

else if(cnt == 20'd1)begin

key_value <= key;

key_flag <= 1'b1;

end

else begin

key_value <= key_value;

key_flag <= 1'b0;

end

end

endmodule

beep_control

module beep_control(

input clk,

input rst_n,

input key_value,

input key_flag,

output reg beep

);

always @ (posedge clk or negedge rst_n)begin

if(!rst_n)

beep <= 1'b1;

else if(key_flag && (key_value == 1'b0))

beep <=~beep;

end

endmodule

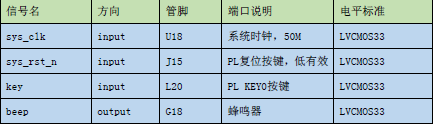

约束文件

set_property -dict {PACKAGE_PIN G18 IOSTANDARD LVCMOS33} [get_ports {beep}]

set_property -dict {PACKAGE_PIN L20 IOSTANDARD LVCMOS33} [get_ports {key}]

set_property -dict {PACKAGE_PIN U18 IOSTANDARD LVCMOS33} [get_ports clk]

set_property -dict {PACKAGE_PIN J15 IOSTANDARD LVCMOS33} [get_ports rst_n]

三、总结

- 程序完整但是有警告

401

401

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?