ZYNQ AX7021基础开发梳理—(1)PL工程创建调试流程梳理

一、概述

此系列文章记录ZYNQ AX7021开发流程梳理,包含vivado、sdk软件使用,PL工程创建及开发流程、PS SDK工程创建及开发流程,涉及三个demo,

从vivado启动、创建工程,到PL独立点灯、PS串口打印(SDK初探)、最后PS控制PL点灯。

二、VIVADO启动

Vivado ubuntu下启动:

source /opt/Xilinx/Vivado/2017.4/settings64.sh

vivado &

三、PL Demo

此demo实现vivado软件创建工程,PL点亮LED灯,描述vivado软件工程创建、编码、添加管脚约束、添加时钟约束、编译工程、烧录器连接,下载等基础操作。

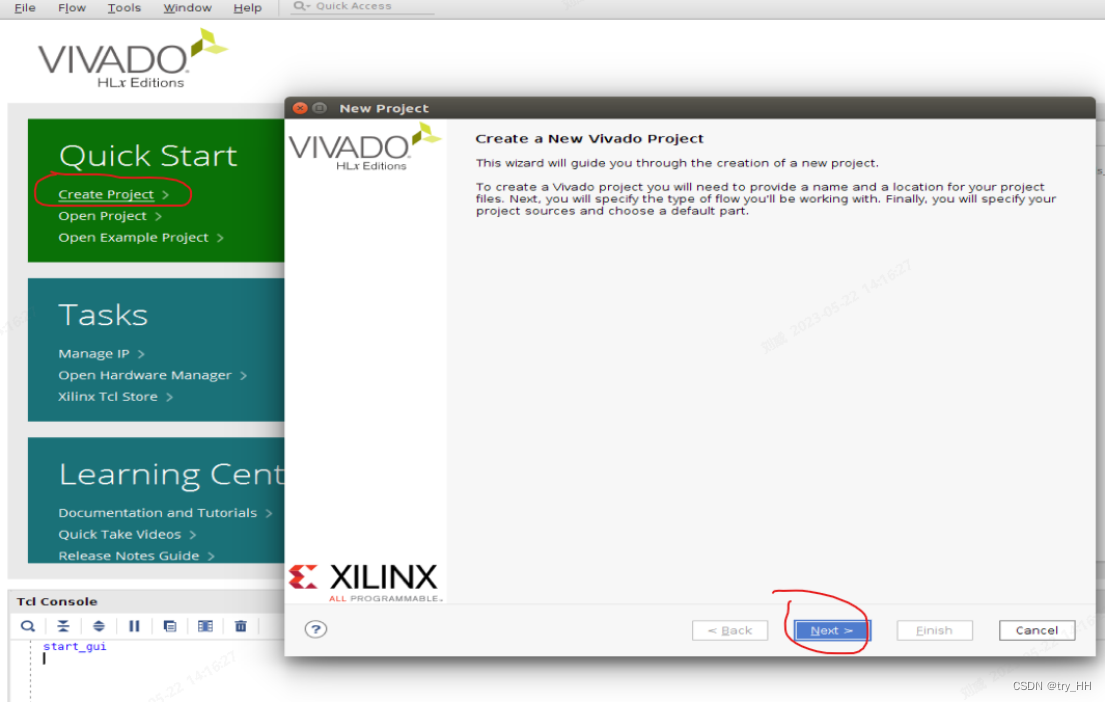

3.1 新建工程

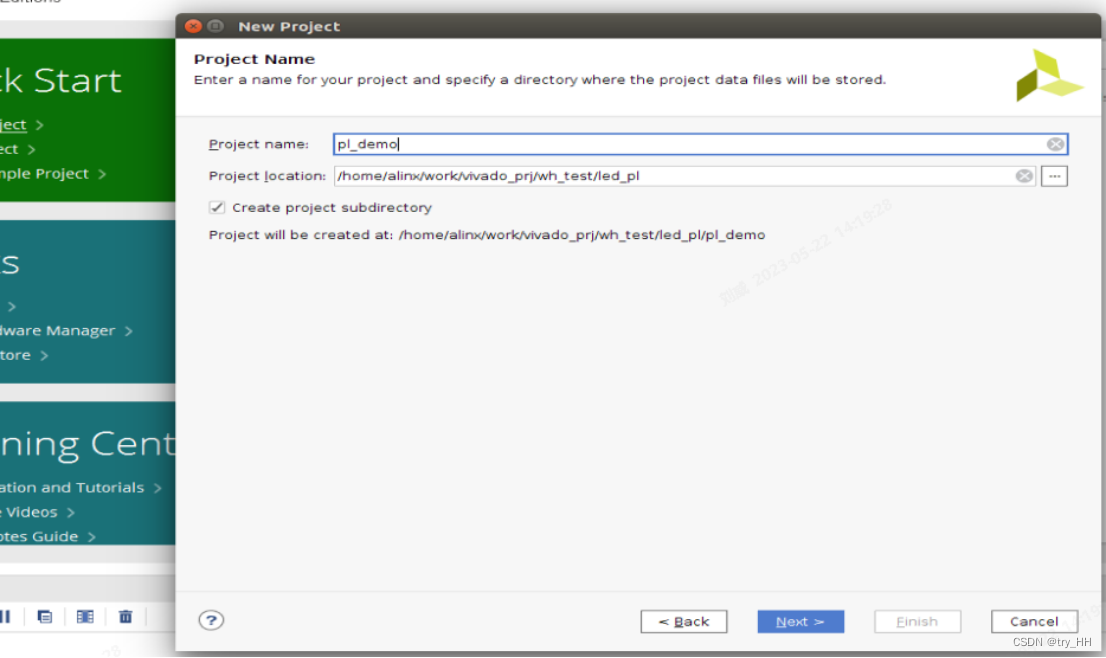

设置工程名,选择工程存放的位置

选择工程类型为RTL Project

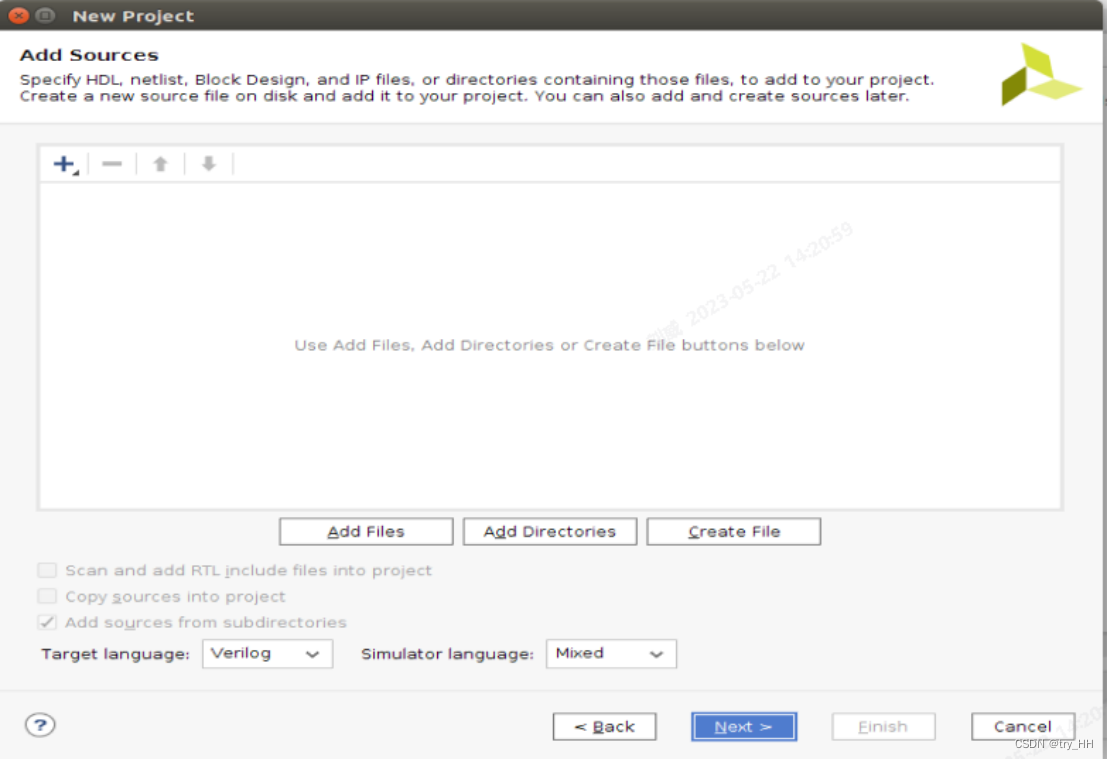

下一步,不用添加文件(后续在工程中再去添加)

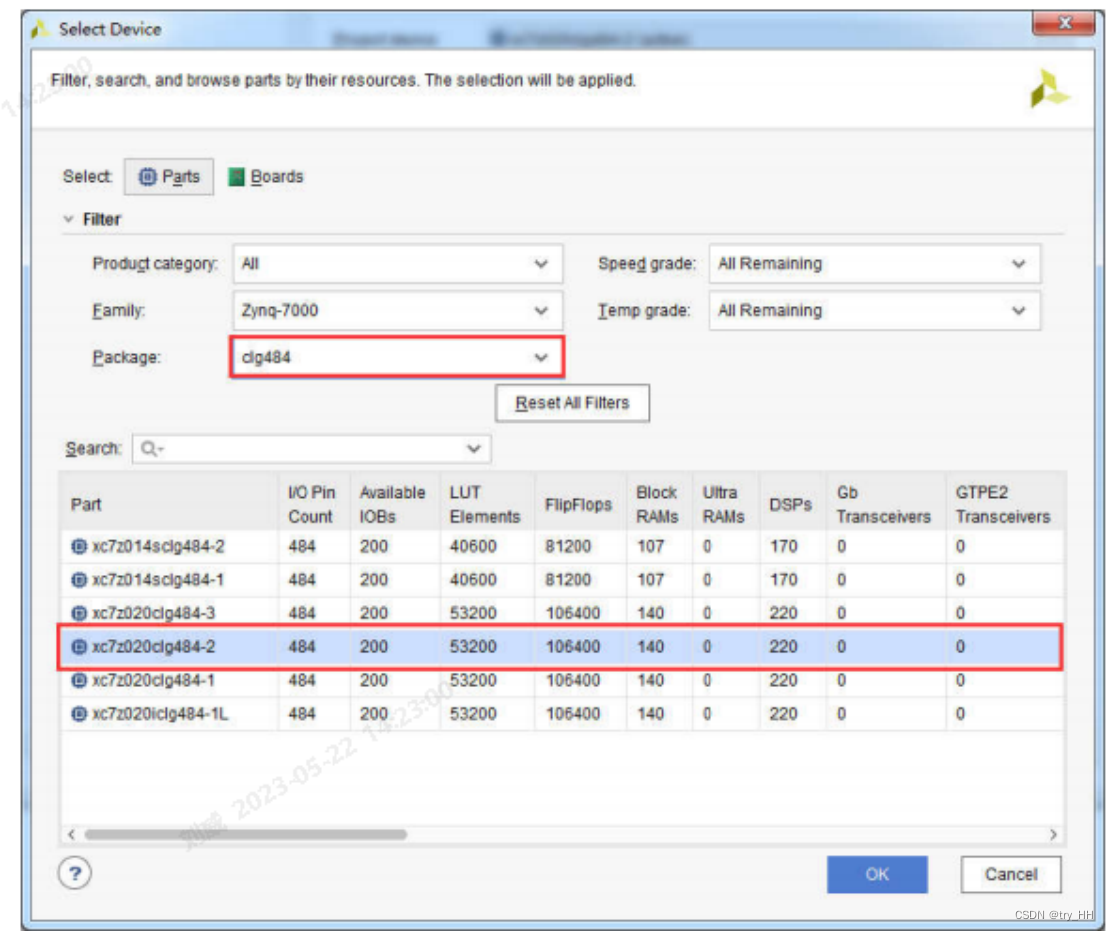

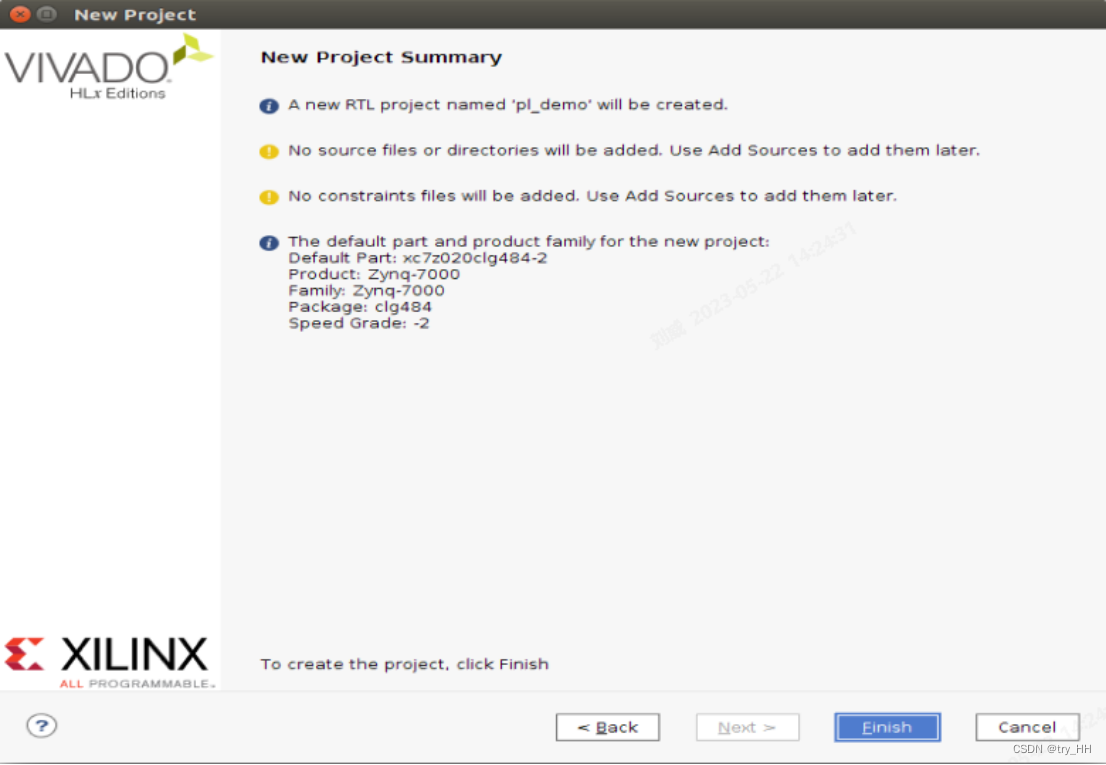

选择设备类型 -2 代表速率等级,数值越大,代表性能越好

点击Finish完成工程创建

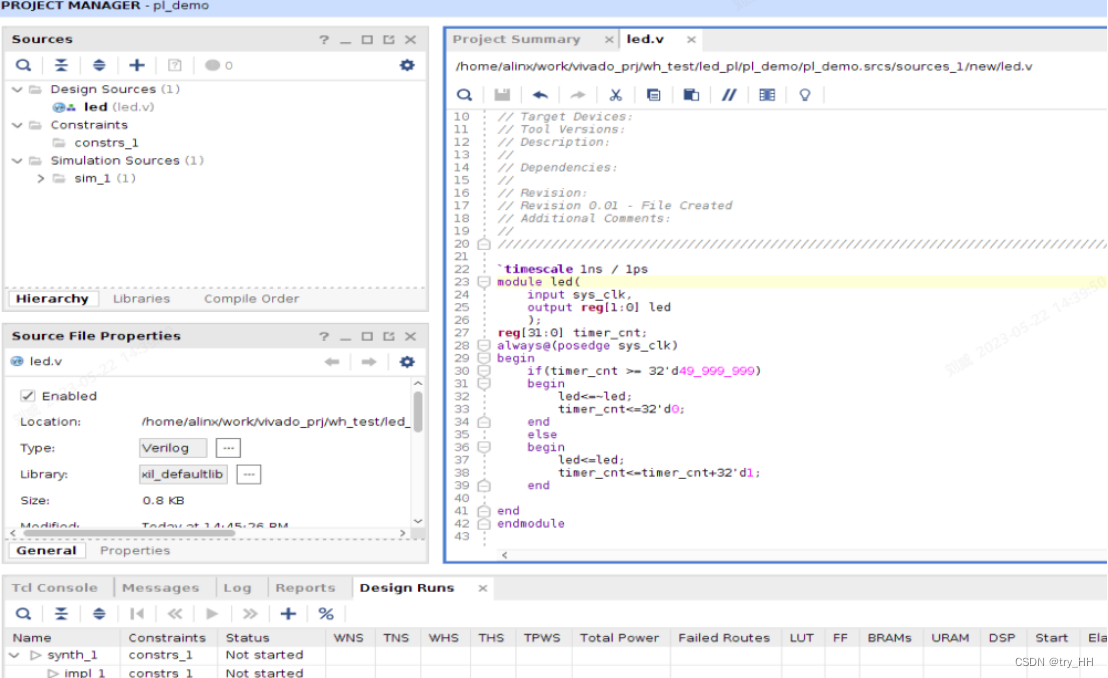

3.2 新建源文件

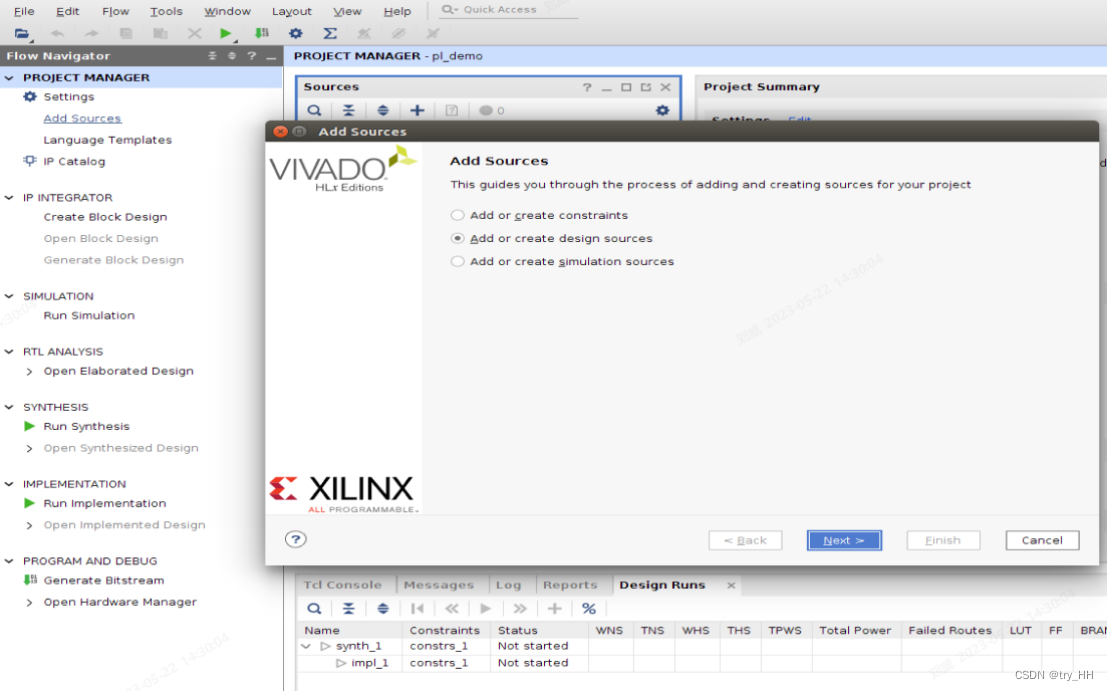

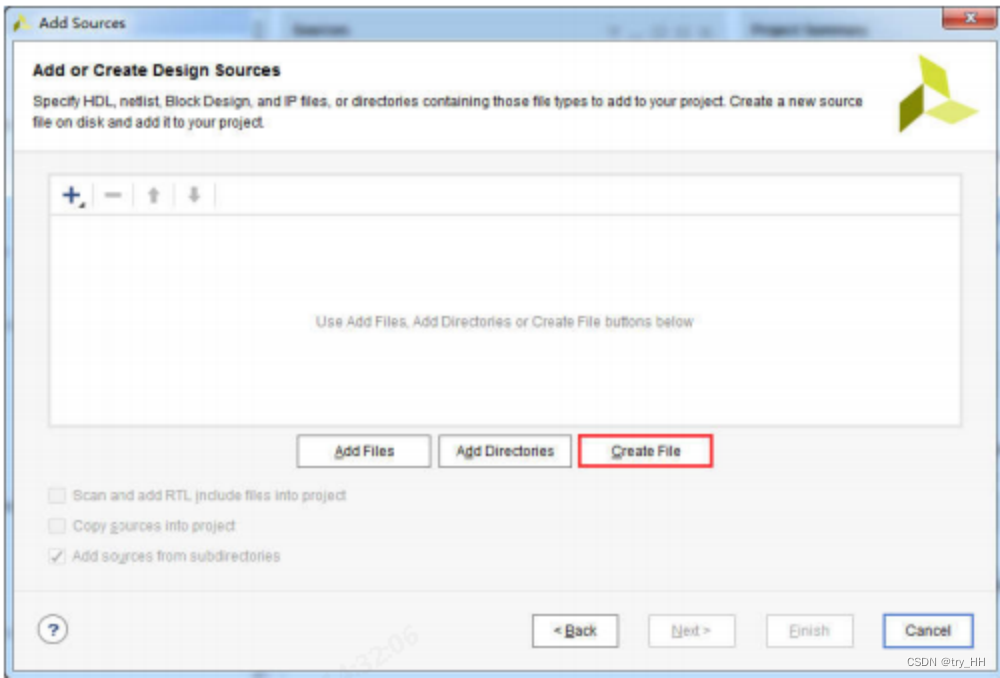

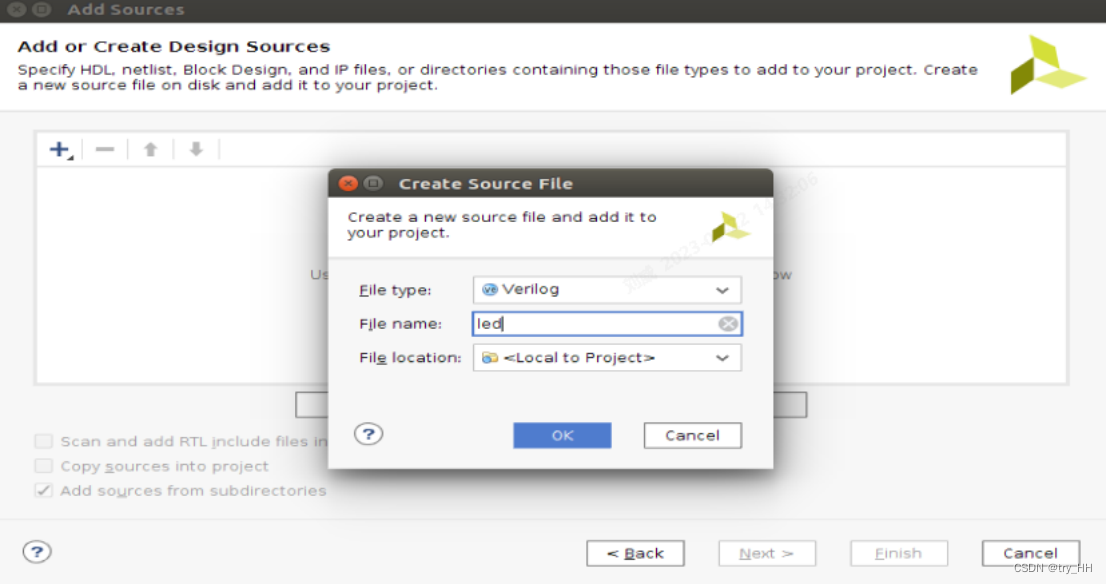

ALT+A 新建Velog源文件

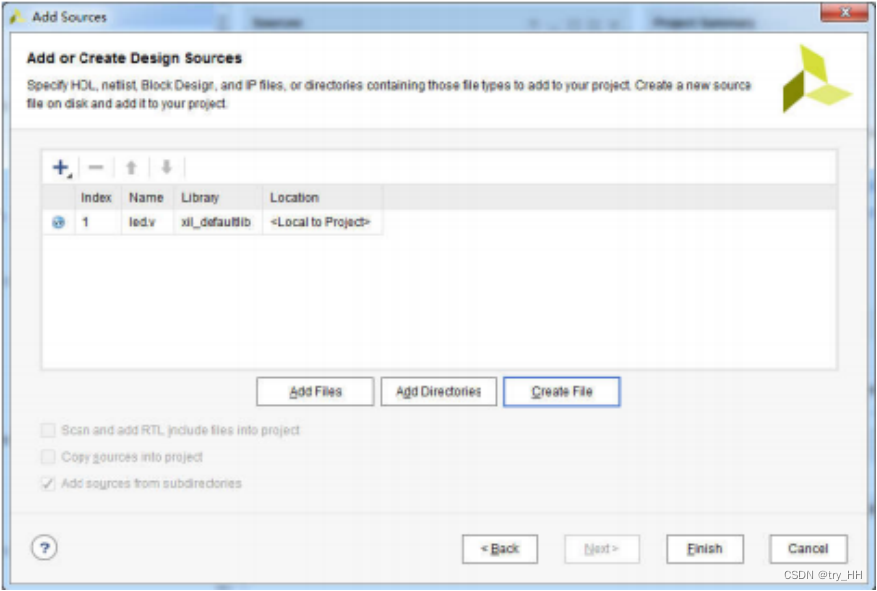

点击Finish完成led.v源文件创建

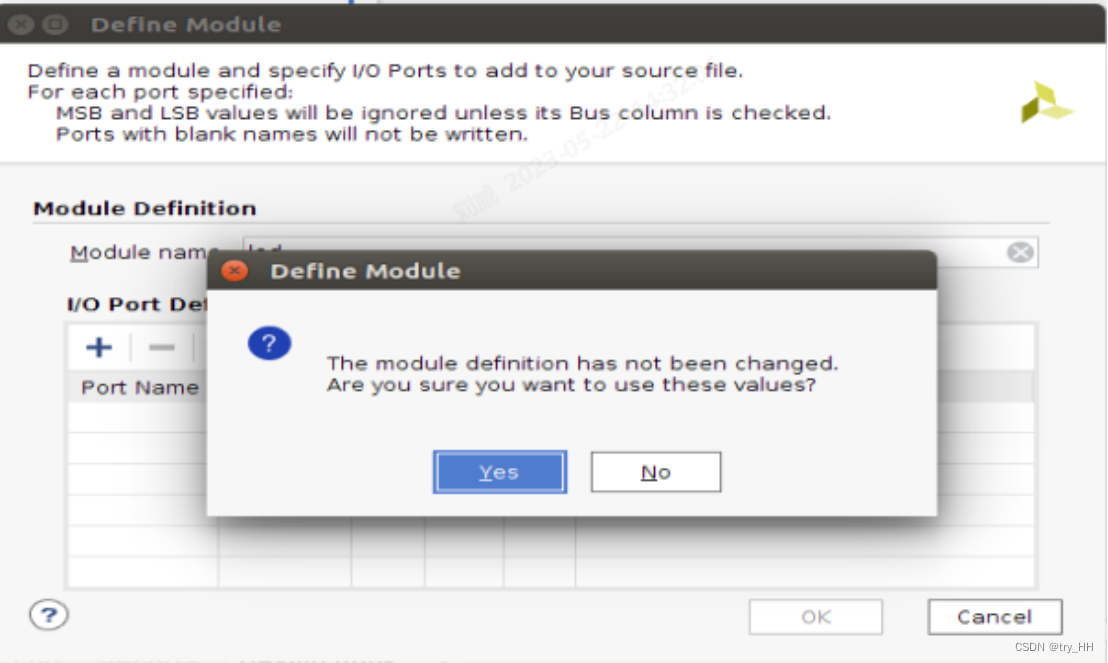

选择模块默认名配置

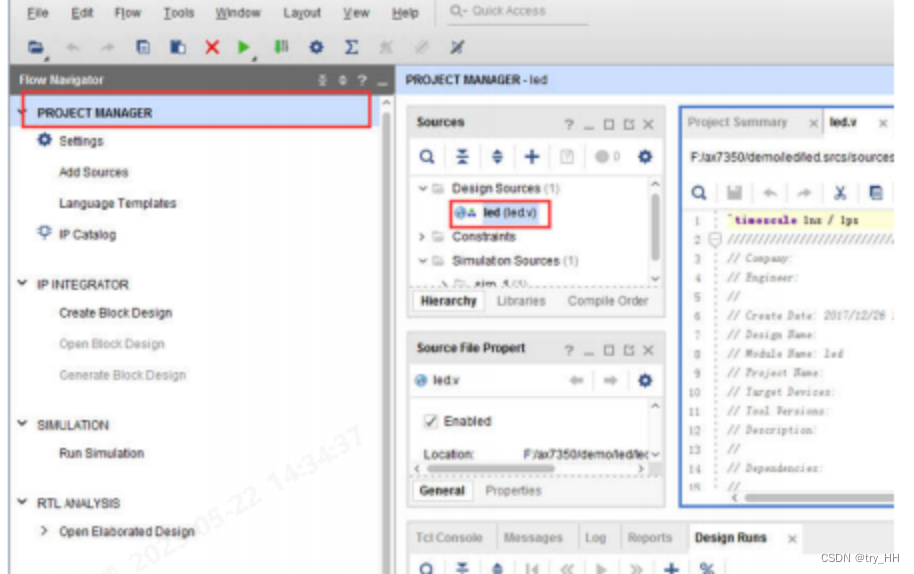

双击打开led.v文件

编辑源文件

`timescale 1ns / 1ps

module led(

input sys_clk,

output reg[1:0] led

);

reg[31:0] timer_cnt;

always@(posedge sys_clk)

begin

if(timer_cnt >= 32’d49_999_999)

begin

led<=~led;

timer_cnt<=32’d0;

end

else

begin

led<=led;

timer_cnt<=timer_cnt+32’d1;

end

end

endmodule

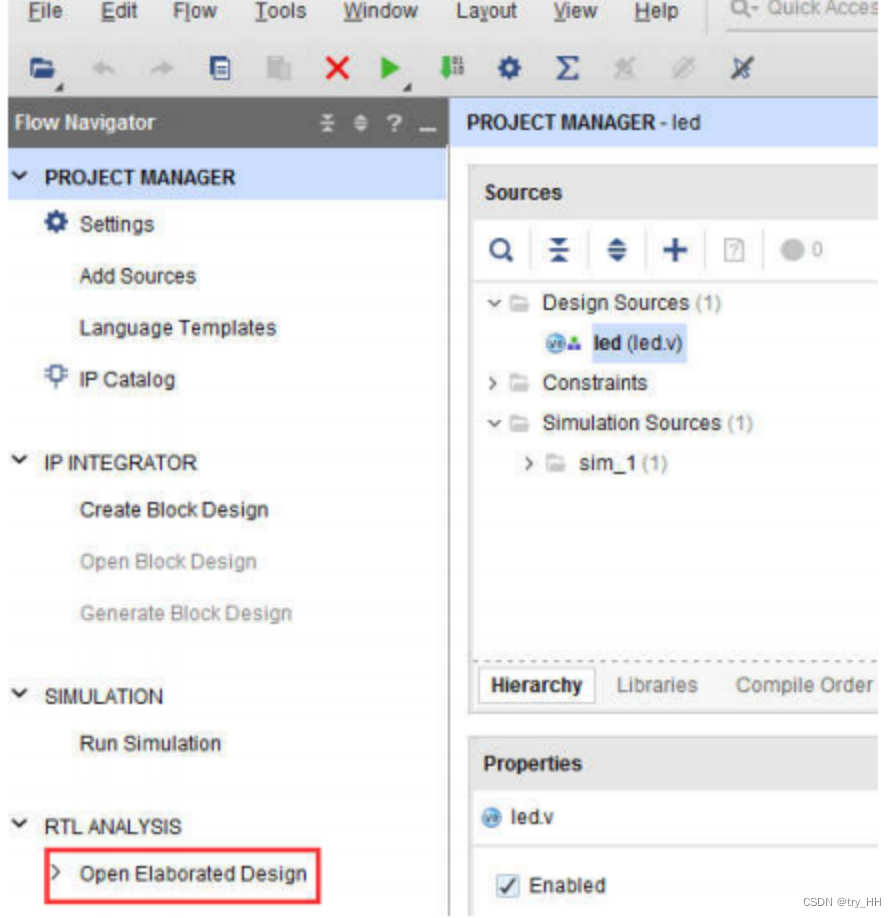

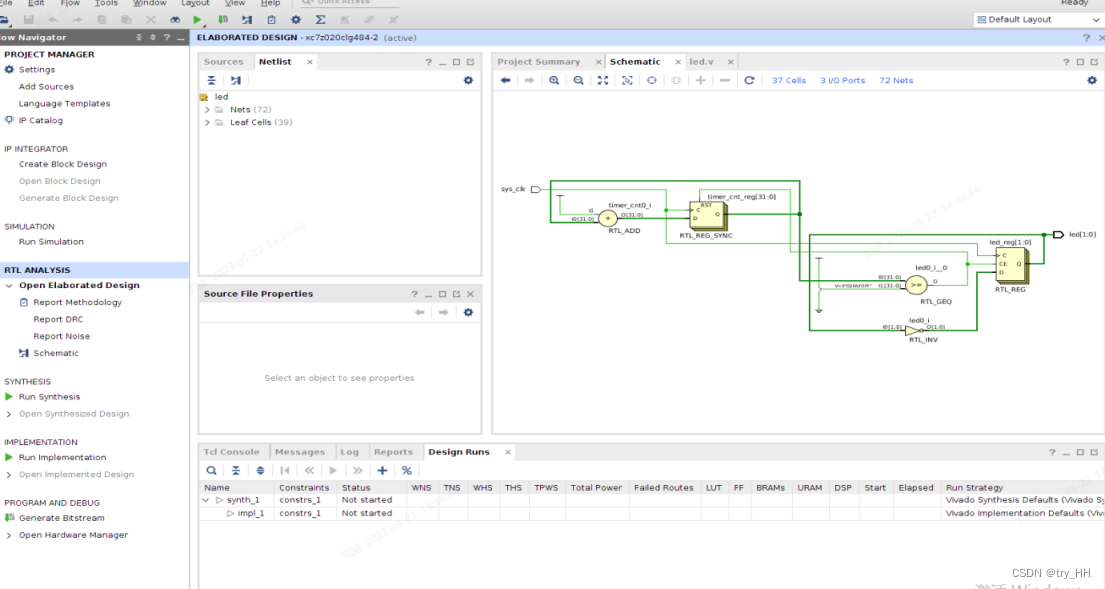

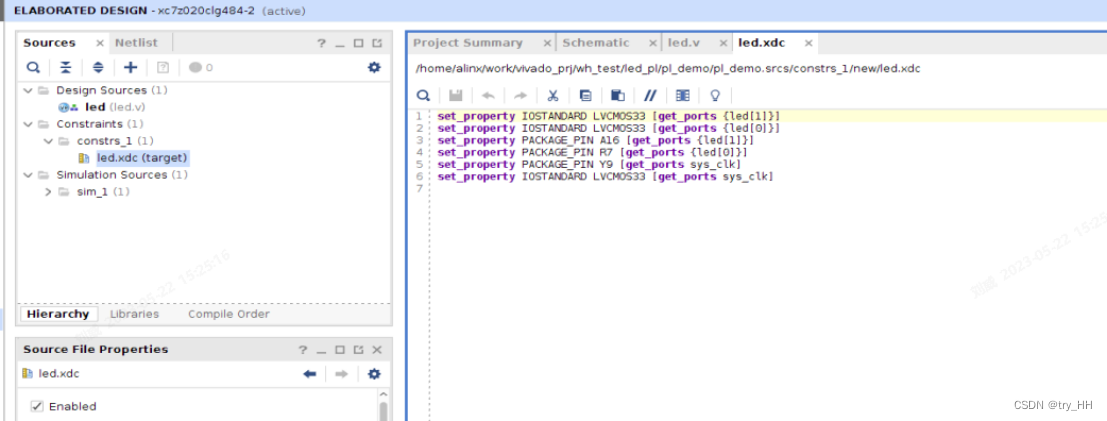

3.3 添加管脚约束

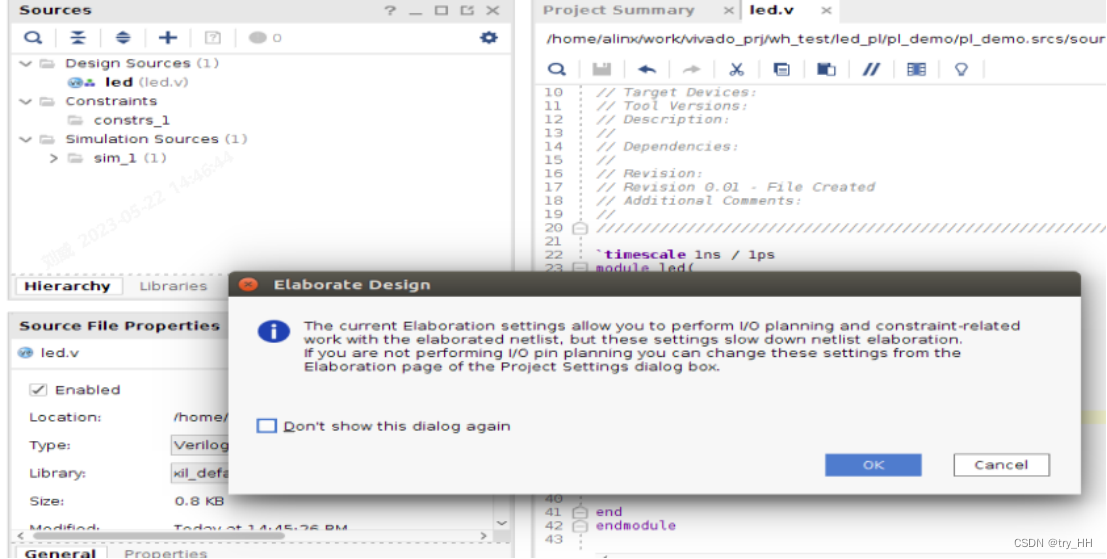

等待完成

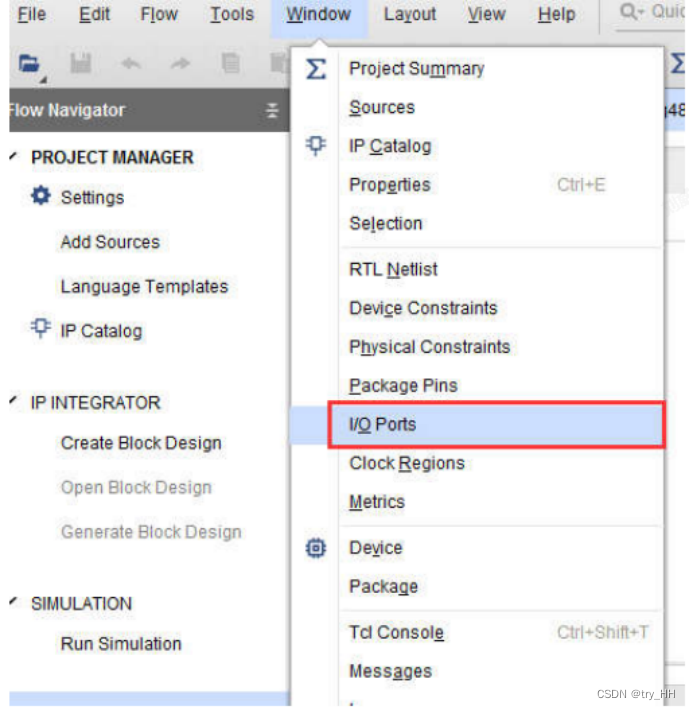

然后点击WIndow --> I/O Port

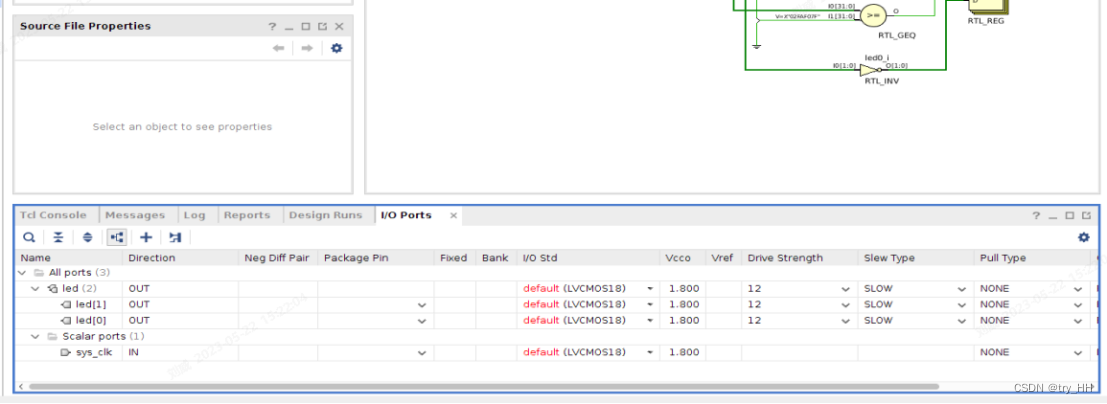

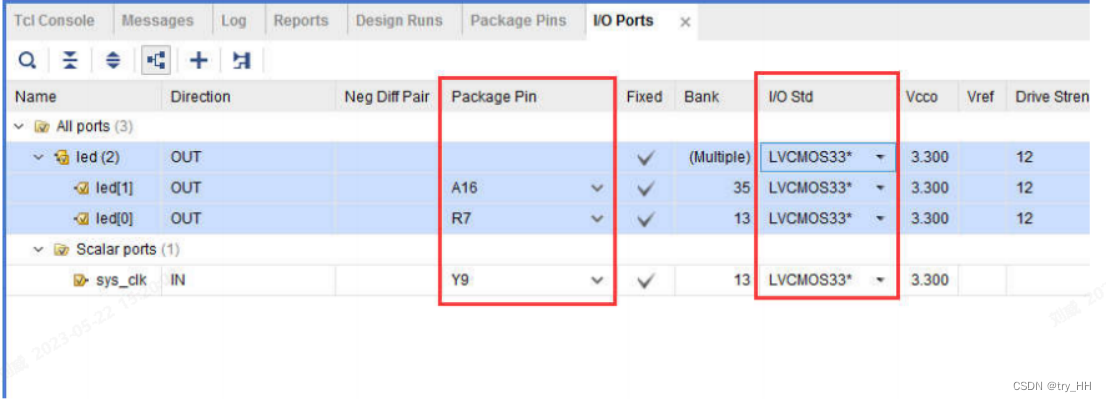

进行管脚分配(引脚、电平)

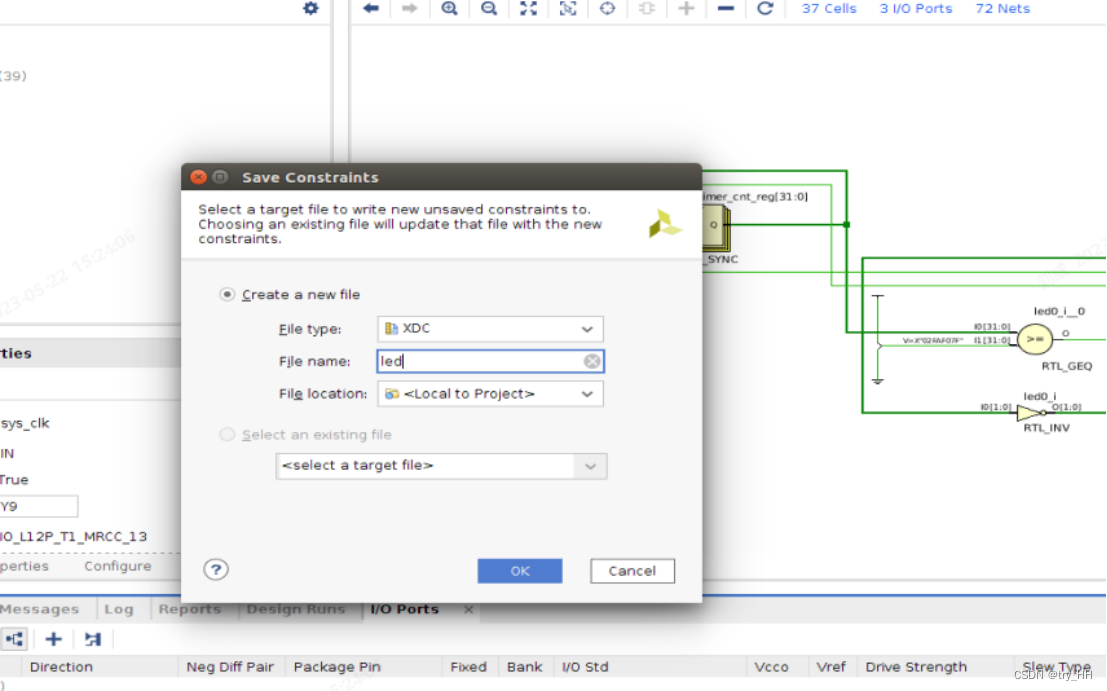

保存后,会出现下面对话框,设置约束文件名为led

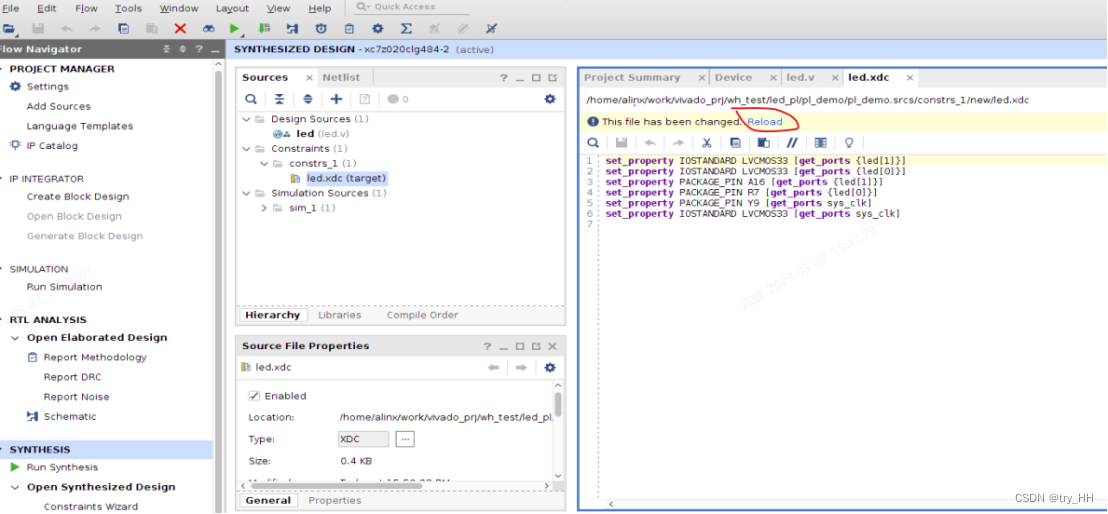

管脚约束文件如下:

XDC编写约束语法说明,普通IO口只需要约束引脚号和电压

引脚约束如下:

set_property PACKAGE_PIN “引脚编号” [get_ports “端口名称”]

电平信号约束如下:

set_property IOSTANDARD “电平标准” [get_ports “端口名称”]

需要注意字母大小写,端口名称是数组的话就用{}括起来,端口名称必须和源代码中的一致,端口名不能和关键字一样。

电平标准中“LVCMOS33”后面的数字指FPGA的BANK电压,所在BANK电压为3.3V

3.4 添加时序约束

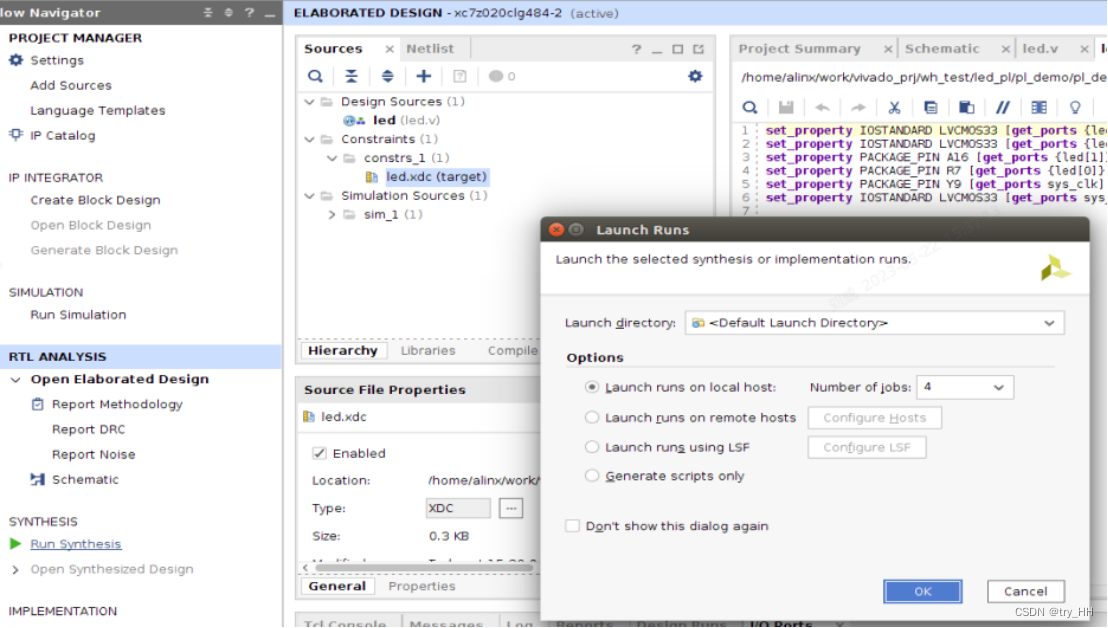

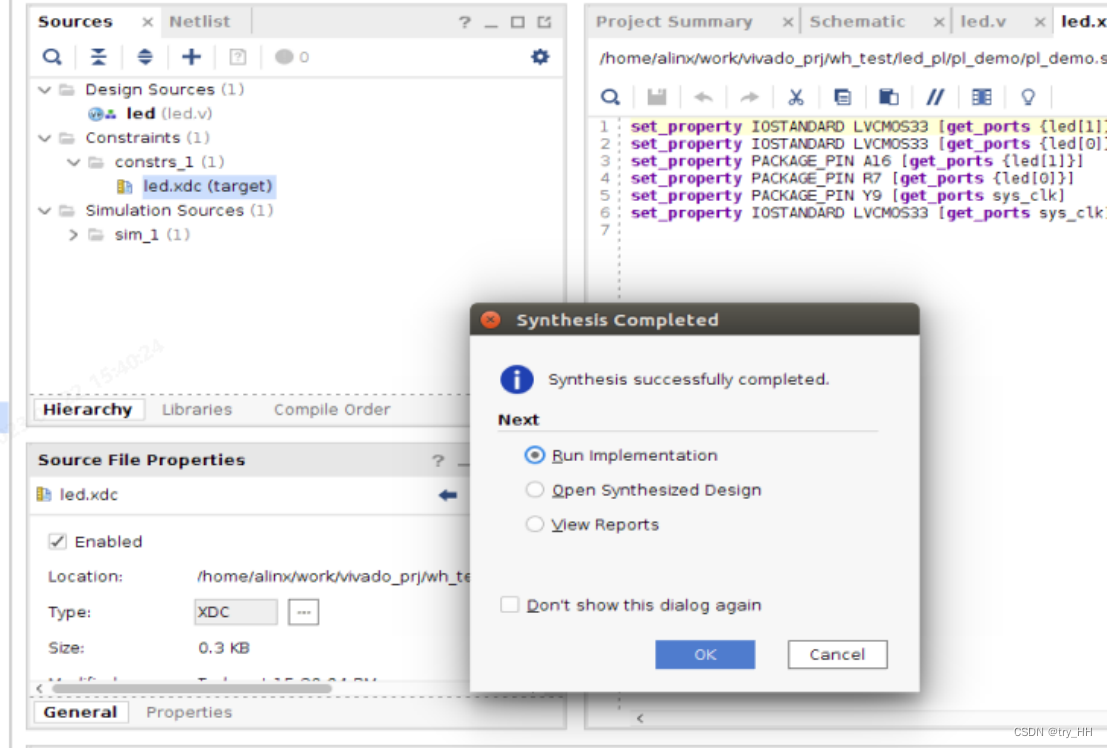

开始向导综合

选择综合配置

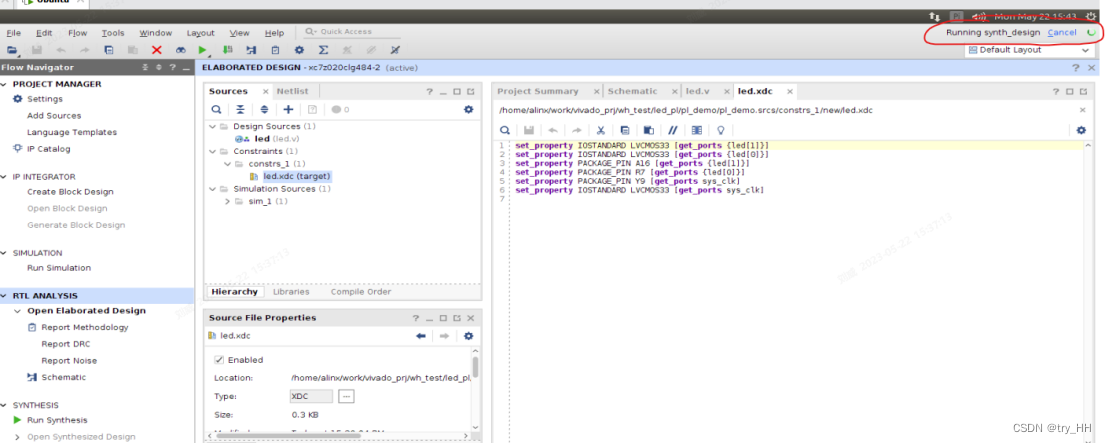

等待综合完成

综合完成后点击Cancel

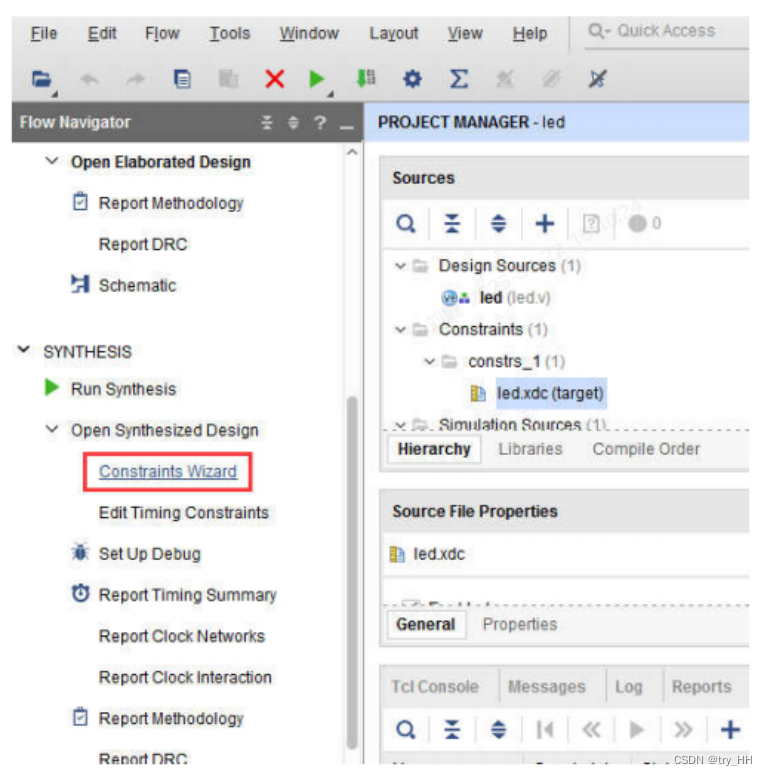

点击Constraints Wizard

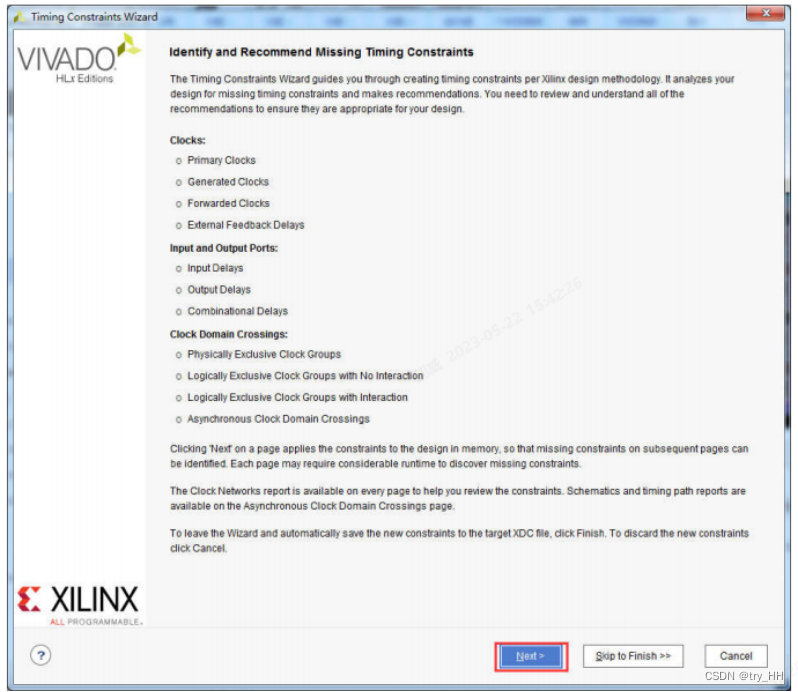

点击下一步

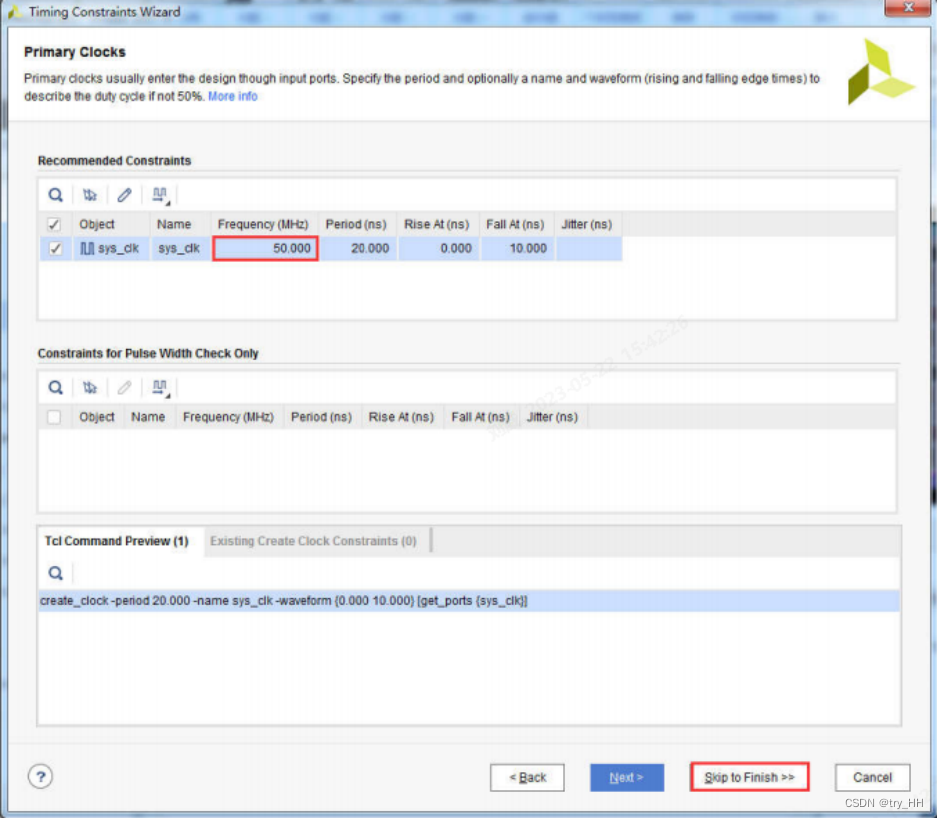

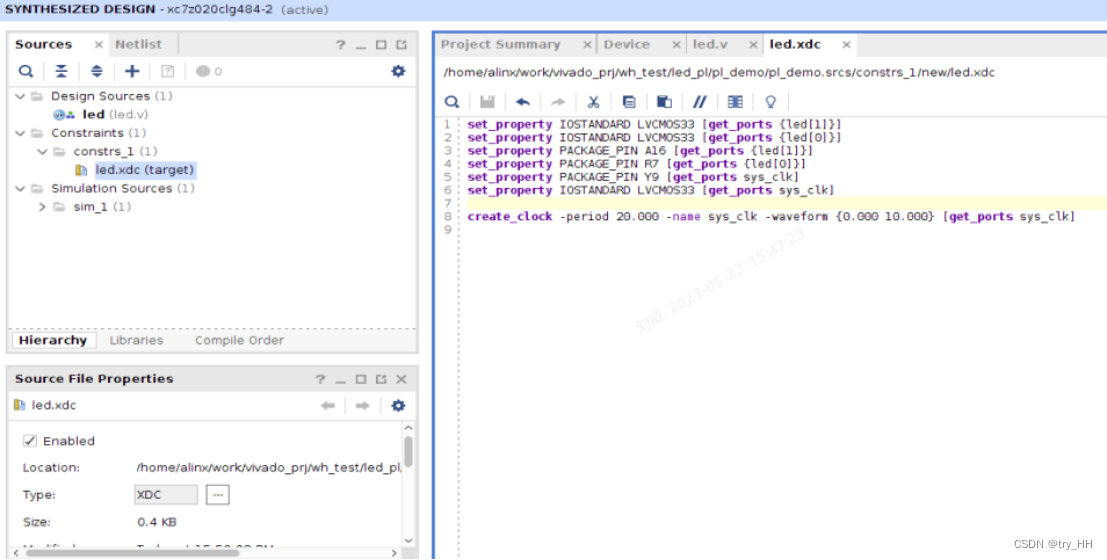

时序约束想到分析出设计中的时钟,将sys_clk频率设置为50MHz,点击Skip to finish结束时序约束向导

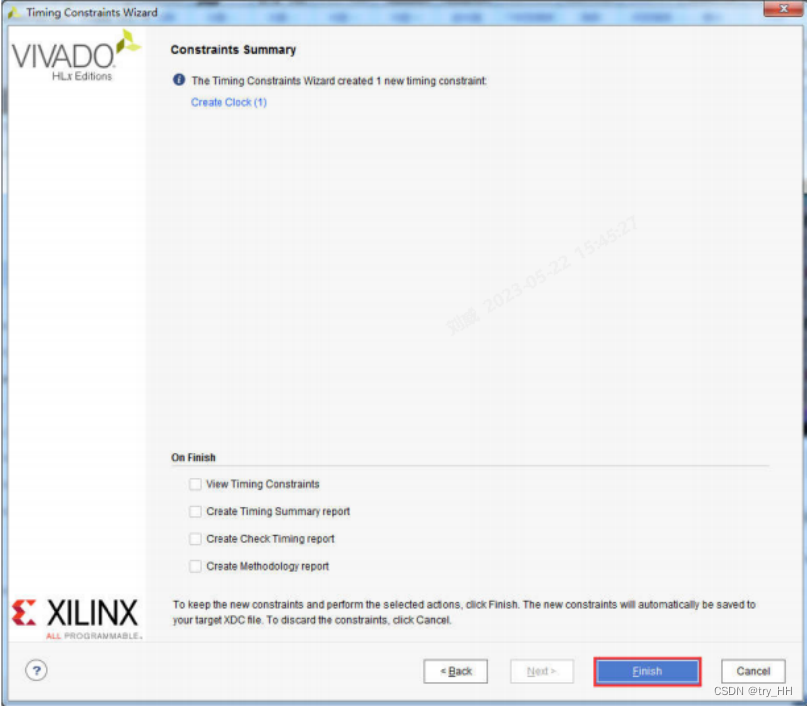

点击Finish

约束完成后重新加载xdc文件

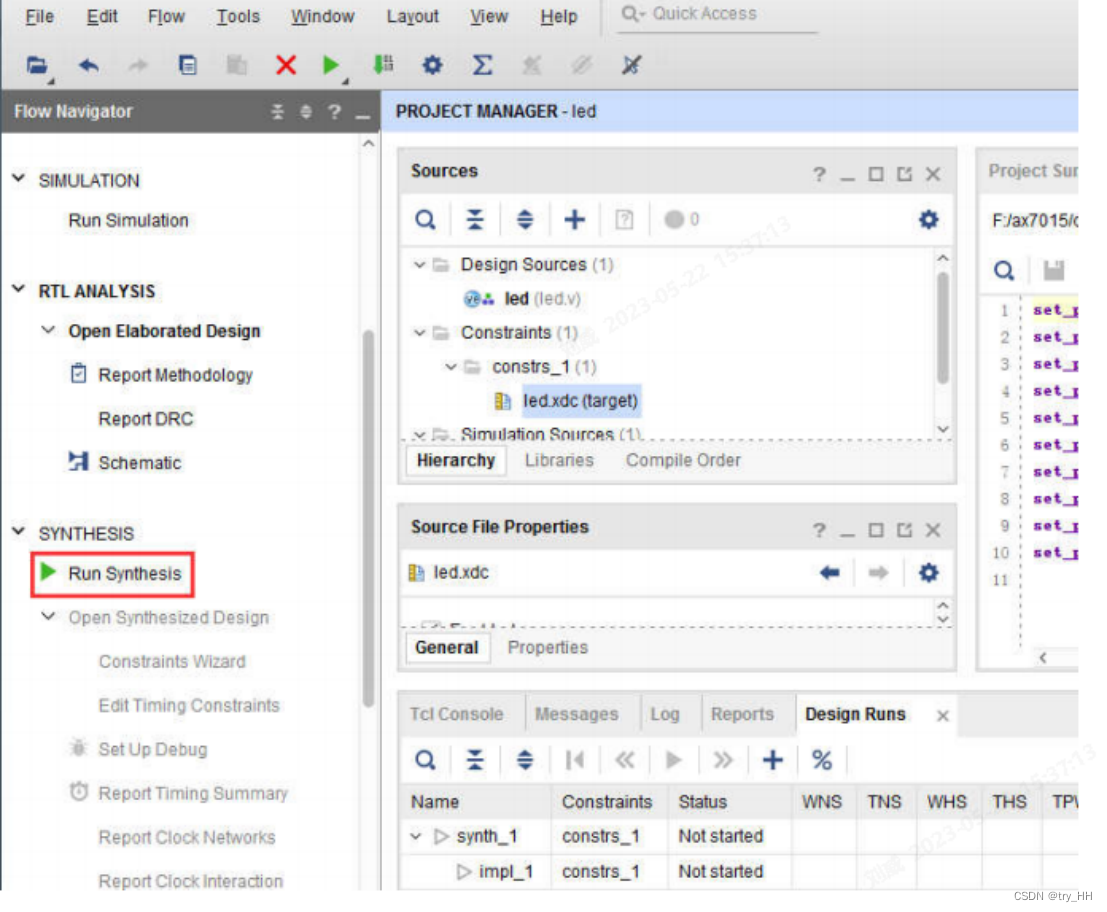

3.5 编译下载

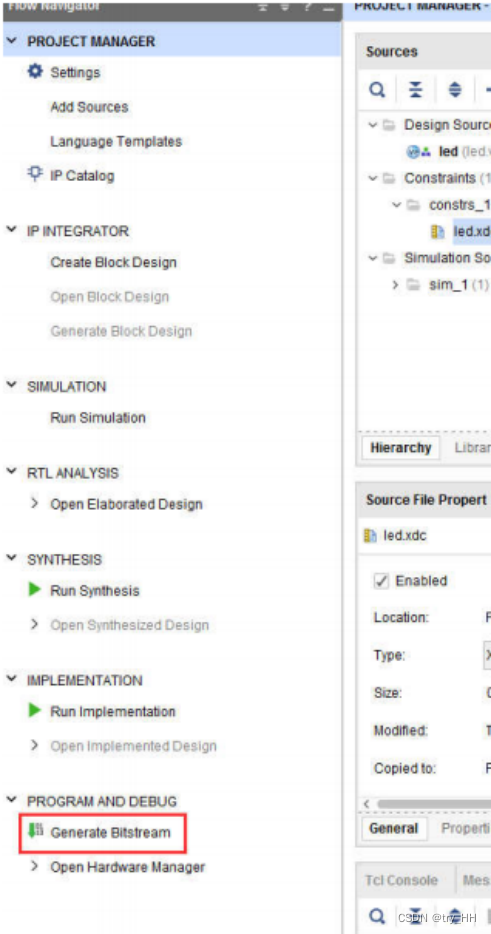

编译的过程分可细分为综合、布局布线、生成bit文件,此处直接描述生成bit文件过程

点击Generate Bitstream

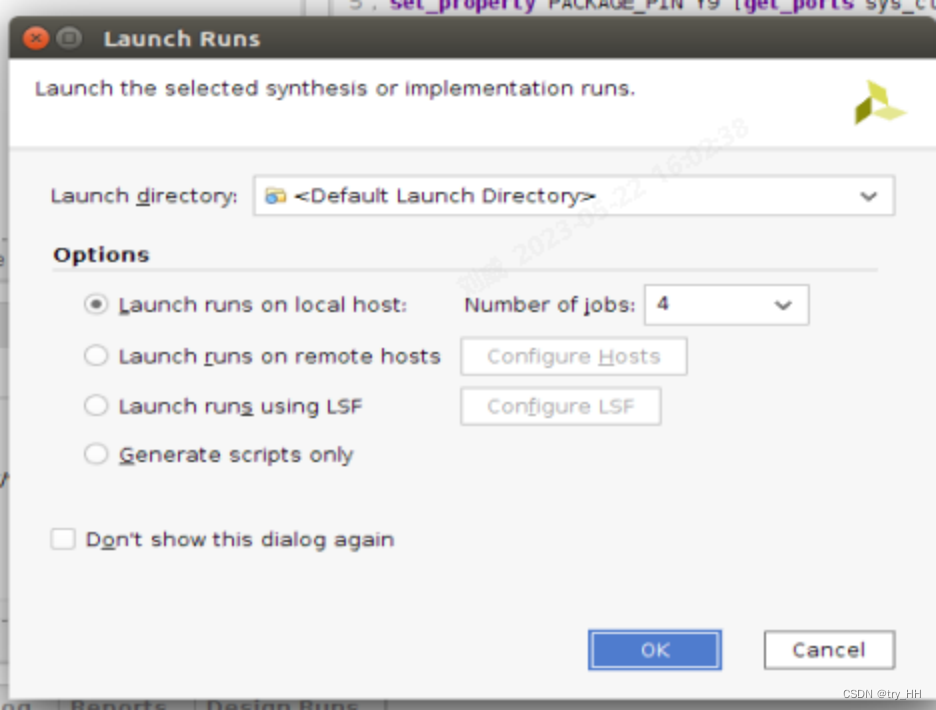

选择任务数量,CPU核心越多编译越快

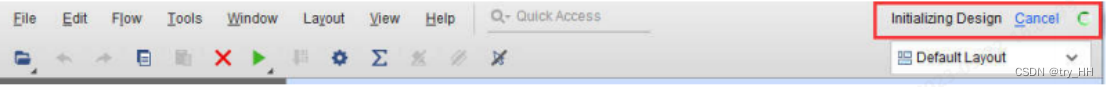

等待编译完成

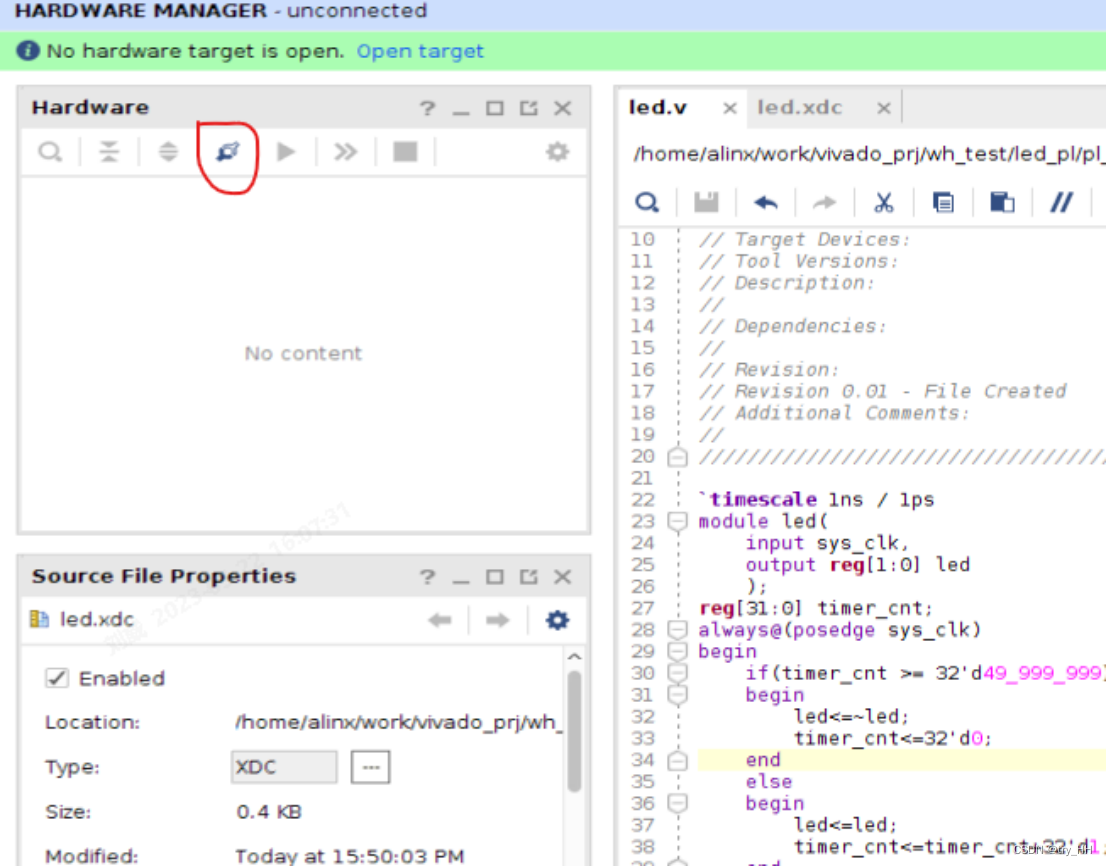

自动连接jtag

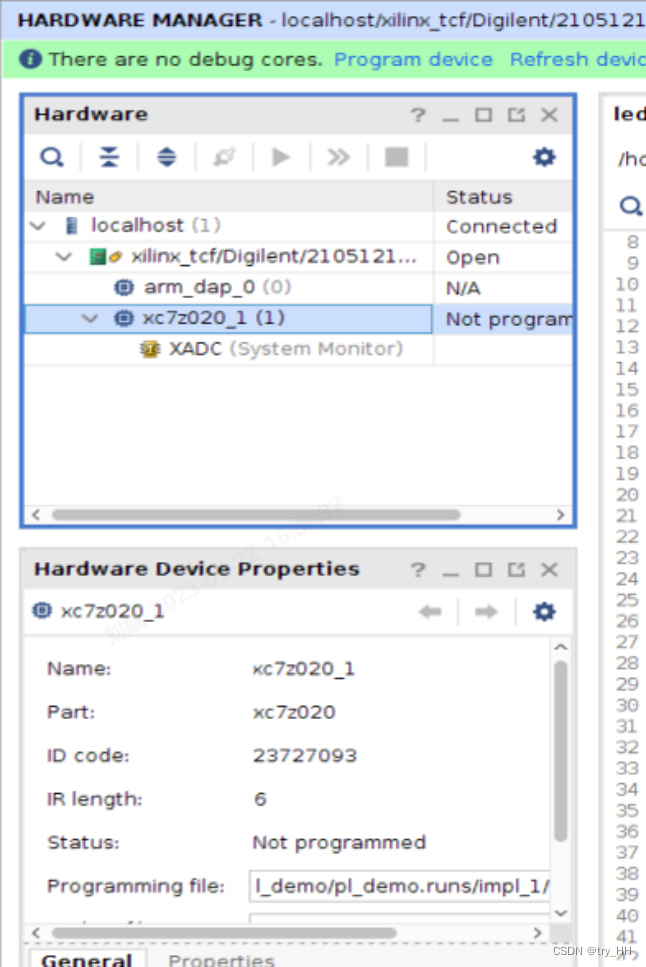

连接成功,显示 下载器以及下面的 arm内核 和fpga内核

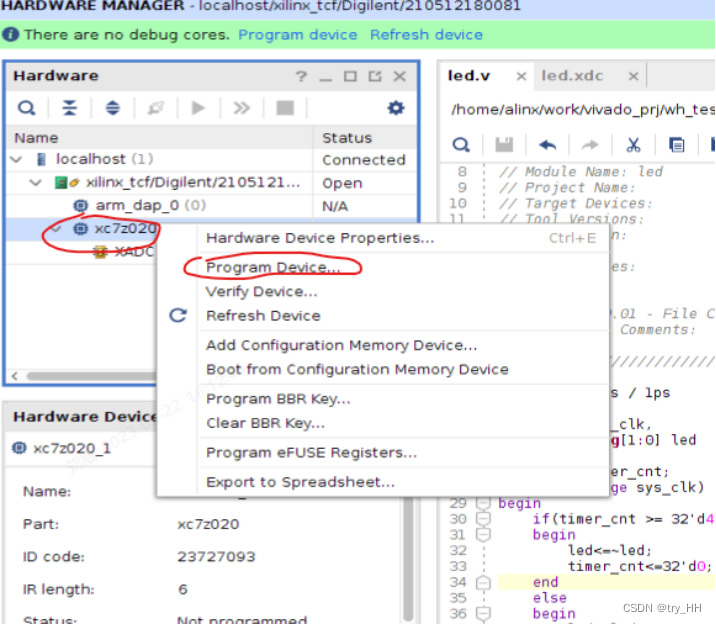

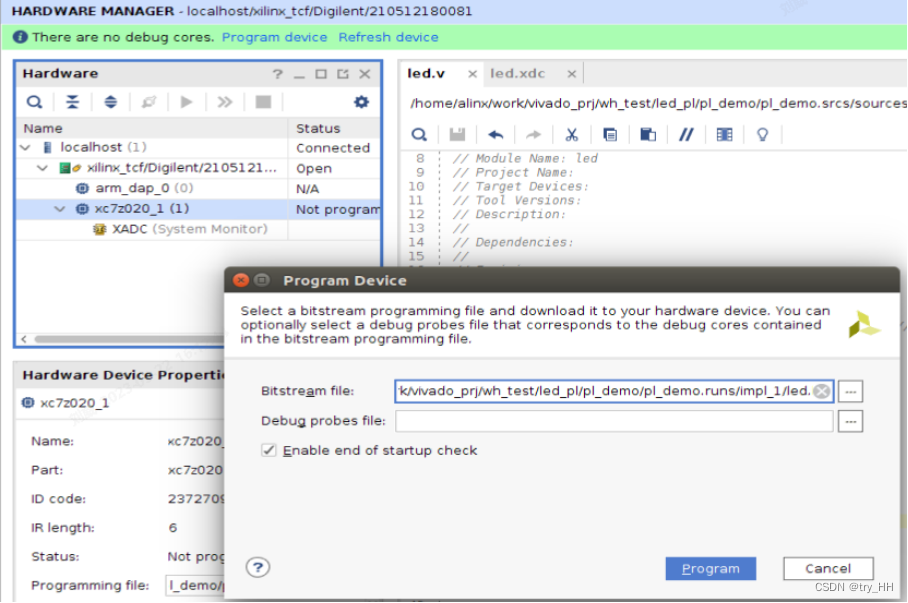

选中FPGA内核,右键点击Program Device…

Program完成下载运行

四、总结

经过上述步骤可实现PL端LED闪烁,熟悉PL基本的开发流程,总结如下:

①新建工程,一般为RTL工程,zynq黑金开发板核心信号为XC7z020clg484-2

②设计输入,verilog编写

③分析Open Elaborated (引脚布点)

④综合 Run Synthesis(对所写的逻辑描述内容进行分析,并得到逻辑门级别的电路内容)

⑤约束输入 ,分为管脚约束和时序约束,依次点击 Source—>“+”—>“add or create constraints” 进行约束文件创建

set_property -dict {PACKAGE_PIN R7 IOSTANDARD LVCMOS33} [get_port {led[0]}]

set_property -dict {PACKAGE_PIN Y9 IOSTANDARD LVCMOS33} [get_ports sys_clk]

//set_property为命令字 PACKAGE_PIN 用于指定管脚 IOSTANDARD用于指定管脚电平 为LVCMOSS33 , get_ports 用于指定源文件中的命名标签

⑥设计实现 Run Implementation

⑦生成bit流 Generate Bitstream

⑧板端下载验证 Open Hardware Manager—>连接—>右键芯片xc7z020_1—>program device

2506

2506

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?