第五章 虚拟存储器管理作业

-

什么是程序运行时的时间局限性和空间局限性?

- 时间局限性:

程序中的某条指令一旦执行, 则补救的将来该指令可能再次被执行; 对于储存单元同样使用

时间局限性主要原因是程序中大量的循环操作 - 空间局限性:

程序在一段时间内所访问的地址, 可能集中在一定的范围, 并不是所有的地址空间等概率的访问

空阿金局限性的原因是程序的顺序执行

- 时间局限性:

-

虚拟存储器有哪些特征? 其中最本质的特征是什么?

虚拟存储器的特征:

- 多次性

- 对换性

- 虚拟性

最本质的特征是虚拟性

-

实现虚拟存储器需要哪几个关键技术?

虚拟内存的实现主要建立在离散分配的内存管理方式上, 所需的具体技术有:

- 页表(段表)机制, 作为主要的数据结构

- 中断机构, 用于产生缺页中断等

- 地址变换机构, 用于将逻辑地址映射到物理地址

-

在请求分页系统中,页表应包括哪些数据项? 每项的作用是什么?

页表的内容: 页号, 物理块号, 状态位P, 访问字段A, 修改位M, 外存地址

- 状态位P: 用于只是该页是否已调入内存

- 访问字段A: 用于记录本页在一段时间内被访问的次数, 或记录多长时间未访问

- 修改位M: 标记该页在调入内存后是否被修改

- 外存地址: 用于指出该页在外存上的地址

-

在请求分页系统中,常采用哪几种页面置换算法?

常用的页面置换算法:

- 最佳置换算法OPT

- 先进先出置换算法FIFO

- 最近最久未使用置换算法LRU

- 时钟置换算法CLOCK

-

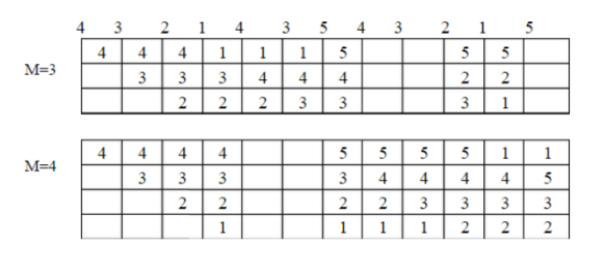

在一个请求分页系统中,采用FIFO页面置换算法时,假如一个作业的页面走向为4、3、2、1、4、3、5、4、3、2、1、5,当分配给该作业的物理块数M分别为3和4时,试计算在访问过程中所发生的缺页次数和缺页率,并比较所得结果。

- M=3时,采用FIFO页面置换算法的缺页次数为9次,缺页率为75%

- M=4时,采用FIFO页面置换算法的缺页次数为10次,缺页率为83%。

由此可见,增加分配给作业的内存块数,反而增加了缺页次数,提高了缺页率,这种现象被称为是Belady现象。

-

影响页面换进换出效率的若干因素是什么?

- 页面置换算法

此为最主要的因素, 直接影响页面置换的效率 - 磁盘写回频率:

添加磁盘缓冲, 将多次写回请求集中到一次执行, 减少磁盘写回的频率, 能够提升页面置换效率 - 内存读取频率:

减少将页面从外存上调入的频率, 能够提升页面置换效率

- 页面置换算法

-

页面缓冲算法的主要特点是什么? 它是如何降低页面换进、换出的频率的?

主要特点:

- 显著降低页面进出频率, 大幅减少磁盘IO, 进而减少开销

- 实现起来非常简单, 因为页面进出开销大幅减小, 才能使用一种较为简单的置换策略(FIFO)以避免特殊的硬件支持

实现方法:

-

使用可变分配和局部置换的内存分配策略

-

在内存中设置两个链表来降低页面换进换出频率:

- 空闲页面链表:

当未被修改的页面换出时, 直接将其所在的物理块挂到此链表尾, 而不将其换到外存, 用于分配给频繁缺页的进程, 以降低缺页率 - 修改页面链表:

将修改的页面挂到此链表尾, 减少换到内存中的频率, 同时降低磁盘写回的频率

- 空闲页面链表:

-

在请求分页系统中,产生“抖动”的原因是什么?利用哪几种方法来防止“抖动”?

产生抖动的直接原因是某个进程频繁访问的页面数量高于可用的物理页帧数量, 通常是由于多道程序度过高导致的

解决的方法:

- 采用局部置换策略

- 把工作集算法结合进处理机调度算法中

- 利用“L=S”准则调节缺页率

- 暂停部分进程并调出页面

-

何谓工作集? 它是基于什么原理确定的?

工作集指的是在某段时间间隔之内, 进程要访问的页面的集合

工作集的原理:

让操作系统跟踪每个进程的工作集,并为进程分配大于其工作集的物理块。工作集内的页面需要调入到驻留集中, 而工作集外的页面可从驻留集中换出, 如果还有空闲物理块,则可以再调一个进程到内存以增加多道程序数。如果所有工作集之和增加以至于超过了可用物理块的总数,那么操作系统会暂停一个进程,将其页面调出并且将其物理块分配给其他进程,防止出现抖动现象。

2953

2953

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?