Microarchitecture Pipeline

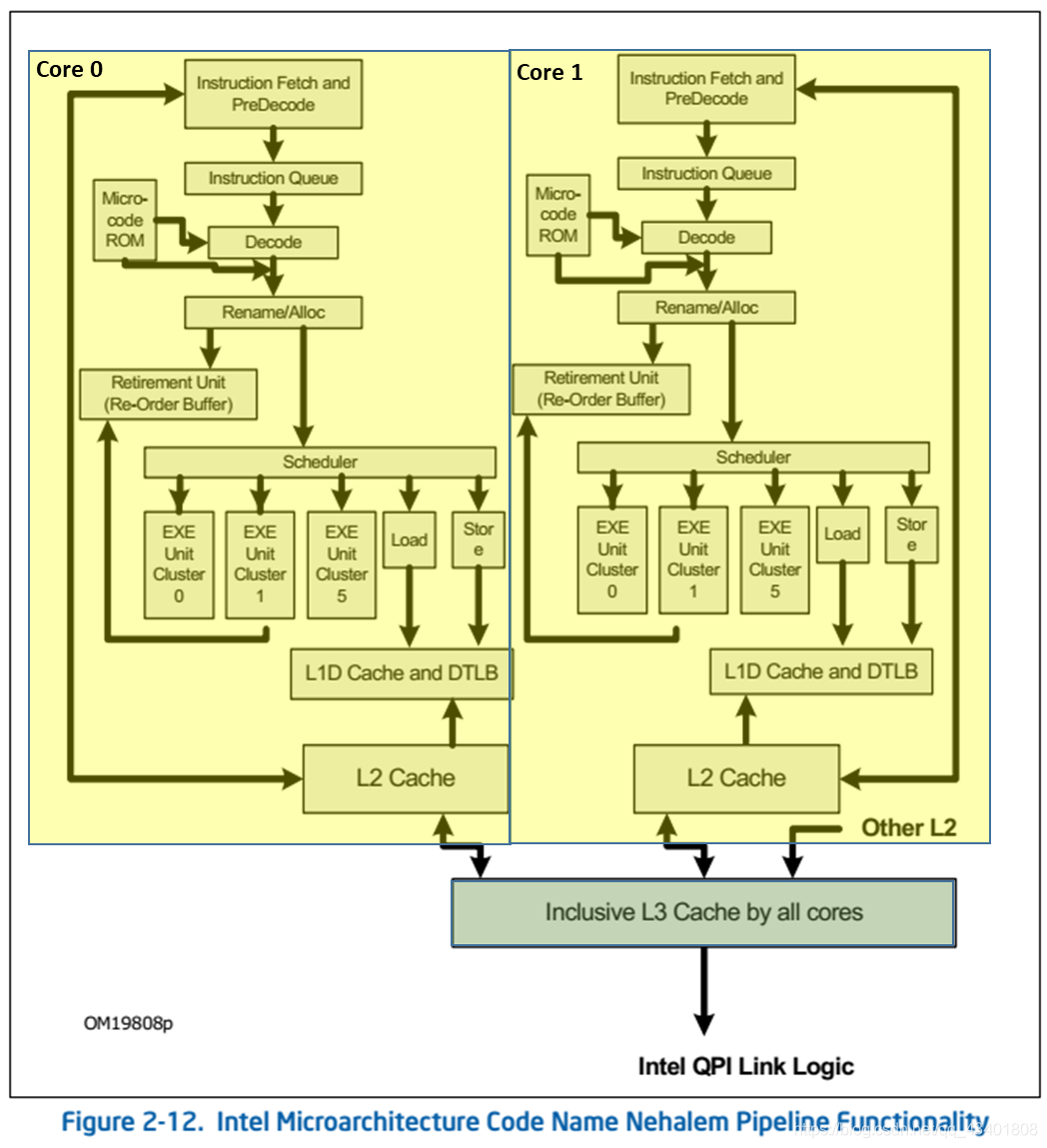

Intel Nehalem微架构延续了65nm制程的Intel Core微架构上的4宽度流水线。下图是在Intel Core i7处理器上采用的Nehalem微架构的功能框图,注意图中只显示了4个处理器核中的两个(黄色部分)。被所有处理器核共享的三级缓存用绿色框标出。

如果用分支预测失败后的延迟来度量,Intel Nehalem微架构的流水线长度比它的前代45纳米的Intel Core 2处理器要多2个周期。前端可以每个周期译码4条x86指令,也支持两个硬件线程,在交替的周期中为两个逻辑处理器分别译码指令流,即一个周期为逻辑处理器0译码,下一个周期为逻辑处理器1译码,再下一个周期切换回为逻辑处理器0译码,如此循环往复。Nehalem微架构前端包括了对分支处理,循环侦测,MSROM吞吐量等的系列增强。后续子章节中会详细介绍。

调度器(即预约站RS)可以每周期透过6个发射口分发6条微指令(上图中显示了5个发射口;Store操作实际上涉及到两个独立的发射口:存储地址口和存储数据口,图中合并成为一个)。

乱序引擎包括多个执行单元;这些执行单元被三个执行单元簇中显示在图中(即图中EXE Unit Cluster 0/1/5 )。正如Intel Core微架构,Nehalem也可以每周期退役4条微指令。

本文深入探讨了Intel Nehalem微架构,详细介绍了其在Intel Core i7处理器上的应用,包括4宽度流水线、前端译码能力、乱序执行引擎及多线程支持等关键特性。

本文深入探讨了Intel Nehalem微架构,详细介绍了其在Intel Core i7处理器上的应用,包括4宽度流水线、前端译码能力、乱序执行引擎及多线程支持等关键特性。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?