SSD使用的典型存储介质是闪存(NAND Flash)。

1.闪存基本原理

1.1存储单元及相关操作

闪存是一种非易失性存储器。

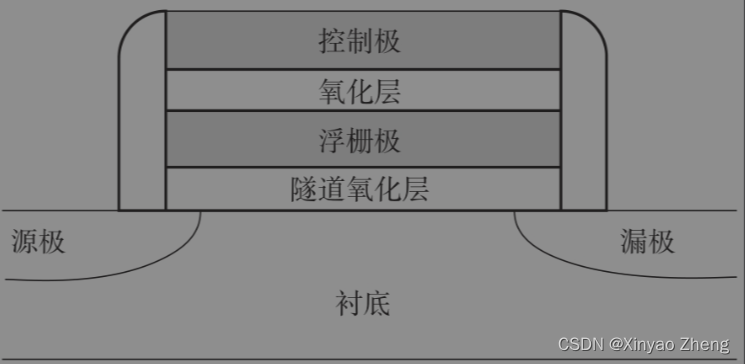

传统2D闪存的基本存储单元(Cell)是一种类NMOS的浮栅(FloatingGate)晶体管。

传统2D闪存的浮栅晶体管,在源极(Source)和漏极(Drain)之间电流单向传导的半导体上形成存储电子的浮栅,它使用导体材料,上下被绝缘层包围,存储在浮栅极的电子不会因为掉电而消失。

如果我们把浮栅极里面没有电子的状态用“1”来表示,存储一定量电子的状态用“0”表示,就能用浮栅晶体管来存储数据了:初始清空浮栅极里面的电子(通过擦除操作),当需要写“1”的时候,无须进行任何操作;当需要写“0”的时候,则往浮栅极里面注入一定量的电子(也就是进行写操作)。

在擦写过程中,需要在控制极和衬底之间建立强电场。随着擦写次数的增多,用来隔离浮栅极电子的隧道氧化层隔绝效果会变得越来越差,后果是电子进出浮栅极变得容易了,最后可能导致浮栅极里面存储的电子数目发生非预期变化,从而使数据由“0”变成“1”,或者由“1”变成“0”。所以闪存都是有擦写次数限制的。我们常用擦写次数(Program & Erase Cycle,PEC)来衡量闪存寿命,当擦写次数超过某个阈值时,闪存可能就不可用了。

- 1)为什么闪存可以存储数据?首先,闪存是非易失性存储介质。存储在浮栅极里面的电子上下层都被绝缘层包围,即使掉电,里面的电子也很难跑掉。其次,闪存可以通过浮栅极里面有无电子或者电子的多少来表示“0”和“1”,能表示“0”和“1”,就具备了存储数据的基础。

- 2)为什么闪存有寿命?擦写操作需要在存储单元的控制极和衬底建立强电场以从浮栅极中清空或者注入电子,这会对隧道氧化层造成物理损伤,日积月累,当擦写次数过多时,隧道氧化层这道“屏障”就失去隔离电子的作用,闪存就存储不了数据了。

- 3)闪存为什么要写前擦除?假设某存储单元之前写入的是“0”,即浮栅极里面有电子,现在我们要把该位从“0”改成“1”,是不能通过往里面注入更多电子达到这个目的的,只能通过擦除操作完成从“0”到“1”的更改。这就好比一块白板,如果上面之前写了很多字,你不能在上面直接写新的字,否则很难分辨,只有擦了重写才能看清楚。

- 4)为什么闪存有数据保持性问题?存储在浮栅极里面的电子,随着时间的流逝,会慢慢通过隧道氧化层溜出(正所谓“天下没有不透风的墙”),今天溜走一个电子,明天再溜走一个,日积月累,量变引起质变,就会导致里面存储“0”的数据变成“1”。这就产生了闪存数据保持问题(Data Retention)。隧道氧化层经历擦写次数越多,这道“墙”透风越厉害,数据保持能力也就越差。

1.2 闪存类型

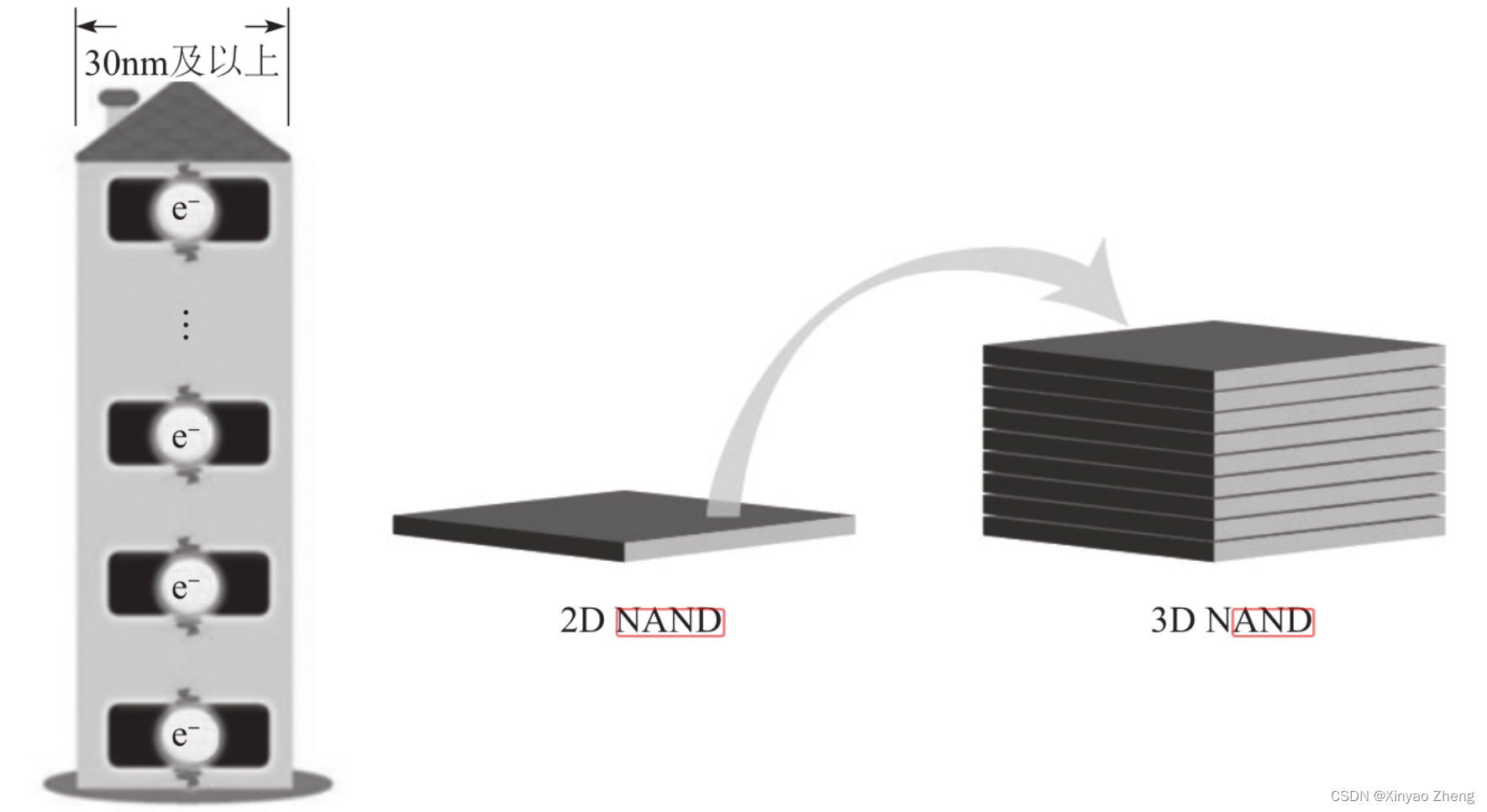

提升闪存存储密度有两种方式:一是物理方式,比如采用3D堆叠方式和使用更先进的制程;二是逻辑方式,即让一个存储单元存储更多位的数据。

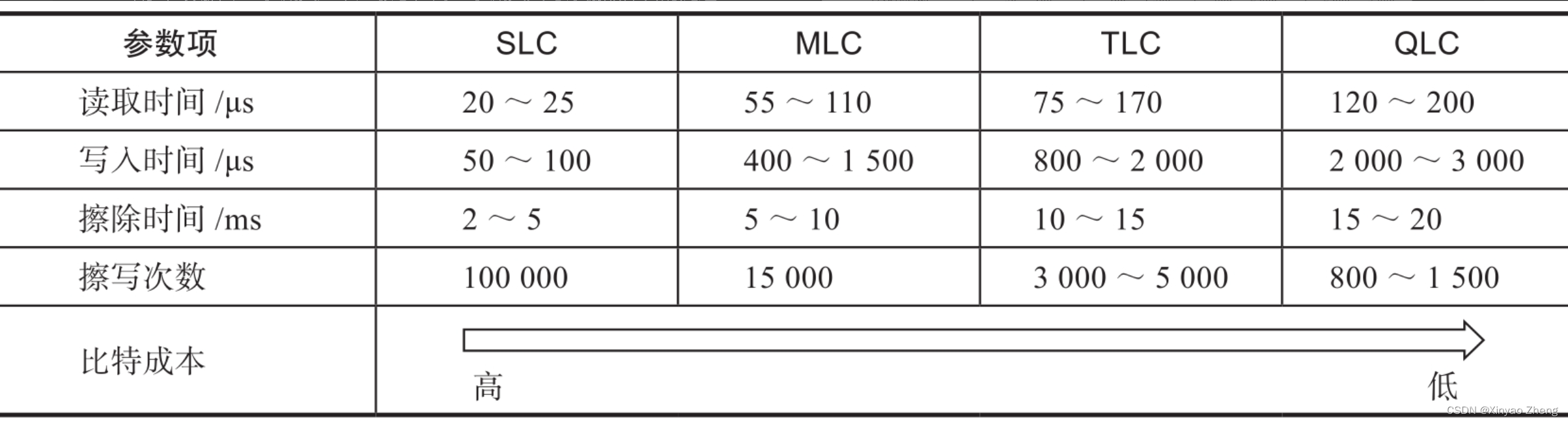

在使用逻辑方式提升存储密度这条路上,先后出现了SLC、MLC、TLC、QLC等类型的闪存。具体来说,一个存储单元存储1位数据的闪存叫SLC,存储2位数据的闪存叫MLC(Multiple Level Cell),存储3位数据的闪存叫TLC(Triple Level Cell),存储4位数据的闪存叫QLC(QuadLevel Cell)。

MLC存储了2位数据,在闪存组织上,其低位数据和高位数据存储在不同的物理页(Page)上,我们把低位数据所在的物理页称为Lower Page(LP),高位数据所在的物理页称为Upper Page(UP)。闪存读取操作的基本单元是物理页,一个时刻只能读取一个物理页,所以不用担心同时读取LP和UP。

提升闪存密度付出的另一个代价就是写的性能会变差。每个存储单元存储的位越多,需要编程的状态就越多;状态越多,每个状态就越精细,也就是往浮栅极注入电子的控制就要越精细,而一旦控制不好,就可能发生从一种状态跳到另一种状态的情况。这是提升闪存密度带来的性能影响。其实不仅如此,它还影响了闪存的寿命和可靠性。

提升闪存的存储密度,在逻辑上就是让存储单元存储更多位数据,但这同时会带来性能下降、可靠性降低和寿命缩短等负面影响。由于存储更多位数据意味着错误率的升高,所以在控制器纠错上需要进行增强。

1.3 闪存组织结构

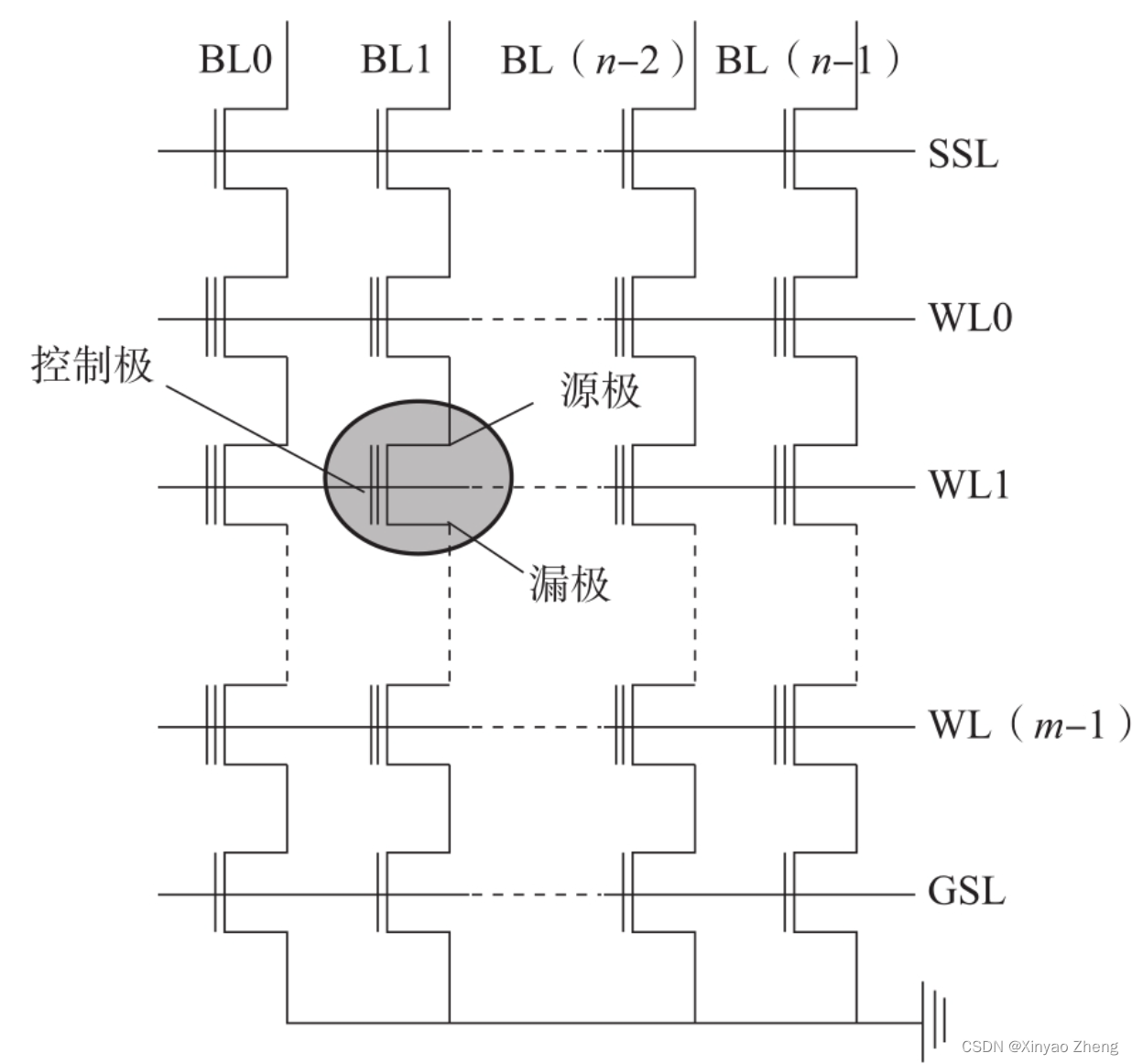

宏观上,一个闪存Die由若干个闪存块(Block)组成,而一个闪存块又由若干个闪存页(Page)组成。闪存块是擦除操作的最小单元,闪存页是读写操作的最小单元。现在主流闪存页的大小为16KB。(注意:实际大小比16KB大,额外的页空间用于存储数据校验信息)。

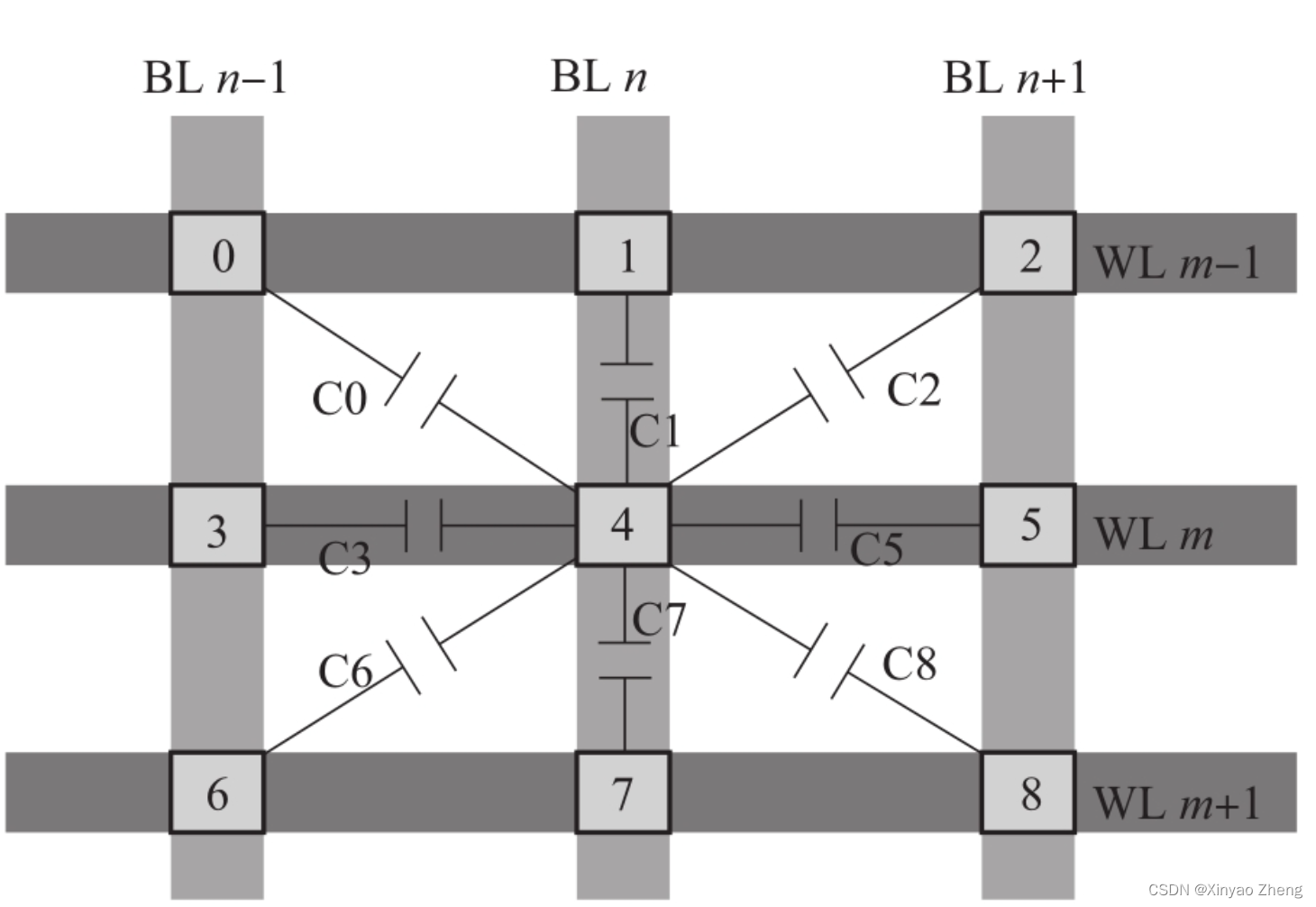

下图是一个闪存块的组织结构示意图。其中,横向是m条字线(WordLine,WL),纵向是n条位线(Bit Line,BL)。1个字线包含若干个闪存页:对SLC来说,1个字线包含1个闪存页;对于MLC来说,1个字线包含2个闪存页,这2个闪存页是1对——LP和UP;对于TLC来说,1个字线包含3个闪存页——LP、MP和UP(不同闪存厂商叫法可能不一样)。假设一个SLC闪存块由1024个闪存页组成,则图中m=1024,即有1024条字线。一个闪存页有多少位,那么就有多少条位线,比如对16KB的闪存页来说,n=16×1024×8。一个闪存块中的所有存储单元都是共用一个衬底的,当往衬底加高电压进行擦除操作时,该闪存块中的所有存储单元电子都会被“吸”出来,因此擦除操作的基本单元是闪存块。

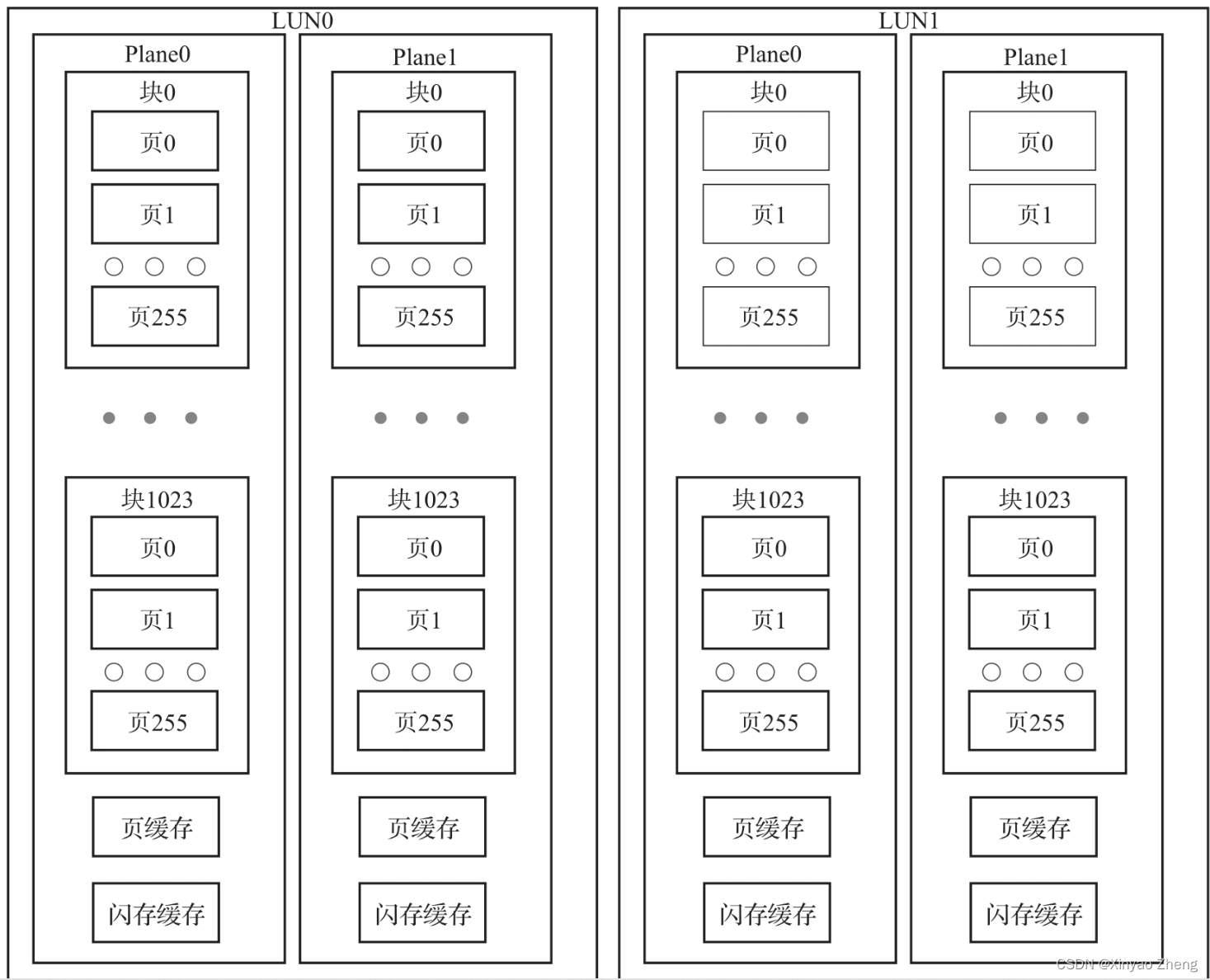

再回到闪存的宏观组成。一个闪存芯片有若干个Die(或者叫LUN),每个Die有若干个Plane,每个Plane有若干个块,每个块有若干个页,每个页对应着一条字线且由成千上万个存储单元构成。闪存Die/LUN是接收和执行命令的基本单元。LUN0和LUN1可以同时接收和执行不同的命令(有一定的限制,不同厂家的多Die操作的限制可能不同)。但在一个LUN中,一次只能独立执行一个命令,即你不能在对其中某个闪存页进行写的同时,对其他闪存页进行读。一个Die又分为若干个Plane。

每个Plane都有自己独立的缓存(Cache Register和PageRegister即闪存缓存和页缓存),每个页缓存的大小等于一个闪存页的大小,它们是闪存内部的RAM,用于缓存要写入闪存阵列(Array)或者从闪存阵列中读取的数据。在写某个闪存页的时候,主控先把数据从主控端传输到与该闪存页所对应的Plane的闪存缓存当中,然后把闪存缓存中的数据写到闪存介质;读的时候与之相反,闪存先把用户所需的闪存页数据从闪存阵列读取到闪存缓存,然后再按需传到主控端。

“一次性编程”,是指一次性把一个存储单元的状态编程到目标状态。例如TLC,一个存储单元涉及LP、MP和UP的数据,一次性编程需要把3个闪存页的数据都准备好,然后一起编程到闪存存储单元阵列。这就需要至少3个页缓存,分别缓存主机写入的3个闪存页的数据,等3个闪存页的数据都凑齐后,闪存根据3个页的数据把每个存储单元编程到期望的状态。

2 闪存可靠性问题

2.1 磨损

随着闪存块擦写次数的增多,闪存原始比特错误率(RBER)逐渐升高。每款闪存,在其规格书里都有厂家标称的擦写次数,比如3D TLC典型的3000次擦写次数,这个数字其实是原厂基于某种纠错算法能力给出的。如果用户使用更强的纠错算法,是能在原厂标称的擦写次数基础上延长闪存使用寿命的;相反,如果用户使用的纠错算法的纠错能力小于原厂假设的纠错能力,则闪存的实际使用寿命会缩短。另外,闪存实际使用寿命还跟数据保持期相关。**如果用户实际使用闪存的时候,不需要数据有这么长的数据保持期,比如若只是临时保存一些数据,则闪存能达到更高的擦写次数。**在这种场景下,标称擦写次数3000次的闪存,可能可以达到10000次(还只是个例子)。相反,如果用户需要更长的数据保持期,标称擦写次数3000次的闪存,可能只能达到2000次。

由于闪存块存在磨损问题,因此在SSD固件算法设计上,我们通常使用磨损均衡算法,这种算法的基本思想是让所有闪存块均摊用户的写入,而不是抓着几个闪存块拼命写,否则整个SSD将因为过早出现过多坏块而不能使用。

2.2 读干扰

读干扰,其原理是在读闪存页的时候,为确保其他浮栅晶体管导通,需要在其他字线上施加VPASS电压,这会导致这些晶体管遭受轻微“编程”,随着闪存块读的次数越来越多,越来越多电子进入浮栅晶体管,最终可能导致位翻转(由1翻转成0)。如果不采取措施,当翻转的位数超出纠错引擎的纠错能力时,就会出现用户数据丢失的情况。

读干扰本身不会影响闪存寿命,只会影响存储在闪存上的数据的可靠性。然而SSD固件算法为解决读干扰问题采用的刷新操作会带来额外的数据写入,造成写放大,因此对闪存寿命会有影响。目前的研究表明,在读密集型场景下,低可靠性的高密度闪存,例如TLC和QLC闪存,会因为读干扰问题产生大量的刷新操作,从而使得即使在少量的主机写操作的场景下,也会导致闪存寿命下降。

2.3 写干扰和抑制编程干扰

写干扰是对编程所在字线上无须编程的存储单元的干扰。所谓“干扰”,就是不希望注入电子的存储单元被意外注入电子。如果说读干扰是“损人”——只影响非读取闪存页,那么写干扰则是“不利己”:它会让编程页上那些不希望编程的存储单元意外地注入电子,导致目标编程页写入错误数据。

编程过程中,除了写干扰,还有抑制编程干扰。抑制编程干扰是对需要编程的存储单元所在位线上单元的干扰。抑制编程干扰纯粹是“损人”,它会导致其他闪存页注入额外的电子,这可能导致已经编程好的闪存页发生位翻转,也可能导致尚未编程的闪存页处于非干净的擦除状态,不管怎样,最终都会影响数据的可靠性。

2.4 数据保持

随着隧道氧化层绝缘效果逐渐变差(擦写次数增多),电子“逃逸”变得越来越容易。电子“逃逸”数目达到一定量时,会导致位“0”翻转成位“1”,当发生位翻转的数目超出控制器的纠错能力时,就会出现用户数据丢失的情况。

虽然数据保持问题和读干扰问题都会导致存储在闪存中的数据发生位翻转,但两者导致的位翻转的方向是相反的:读干扰注入了额外的电子,导致位从“1”翻转成“0”;而数据保持是电子的流失,导致位从“0”翻转成“1”。

从数据写入到电子慢慢泄漏,直到数据出错,这个期限称为数据保存期。如果你的电脑经常处于开机状态,SSD固件会定期对闪存数据块进行扫描,一旦发现闪存比特出错率高于一定阈值,就会对该闪存块进行刷新(把数据从一个闪存块搬到另一个闪存块),并把数据恢复到原来的样子。如果你的电脑时间不开机,SSD固件会因为断电而没有机会刷新,只能任由电子流失。

数据保持期的长短,除了跟闪存擦写的次数有关(擦写越多,数据保持期越短),还跟闪存温度有关:温度越高,数据流失越快。

2.5 存储单元之间的干扰

浮栅晶体管的浮栅极材料是导体。任何两个彼此绝缘且相隔很近的导体间都会构成一个电容器。因此,任何两个存储单元的浮栅极就构成一个电容器:某一个浮栅极里的电荷发生变化,都会引起其他存储单元浮栅极里的电荷发生变化,尤其是与之相邻的存储单元。

一个浮栅极与其附近的浮栅极之间都存在寄生电容,电容大小与两个浮栅极之间的距离成反比:距离越短,电容越大,表示彼此影响越大随着闪存制程的减小,存储单元之间的影响越来越大。这也是2D闪存发展不下去的一个原因:存储单元靠得太近,彼此影响太大。

**按闪存页顺序编程能尽量减少存储单元之间的干扰,保证数据的可靠性。**如果按顺序编程:WL m-1,WL m,WL m+1,在写当前WL的时候,它影响最大的是前一个已经写好的WL,因为它们离得最近。那如果采用乱序写,比如先写WL m-1和WL m+1,回头再来编程WL m,那么在编程WL m的时候,它会同时影响离它最近的WL m-1和WL m+1。如果继续编程WL m+2,那么它又会再次影响离它最近的WL m+1,即WL m+1遭受了两次无妄之灾。

3 数据可靠性问题的解决方案

闪存允许发生比特错误(不得不如此),但SSD却不允许用户数据丢失。因此,在系统层面的SSD软硬件上需要采取一些手段来解决闪存不可靠问题,以确保用户数据的可靠性。

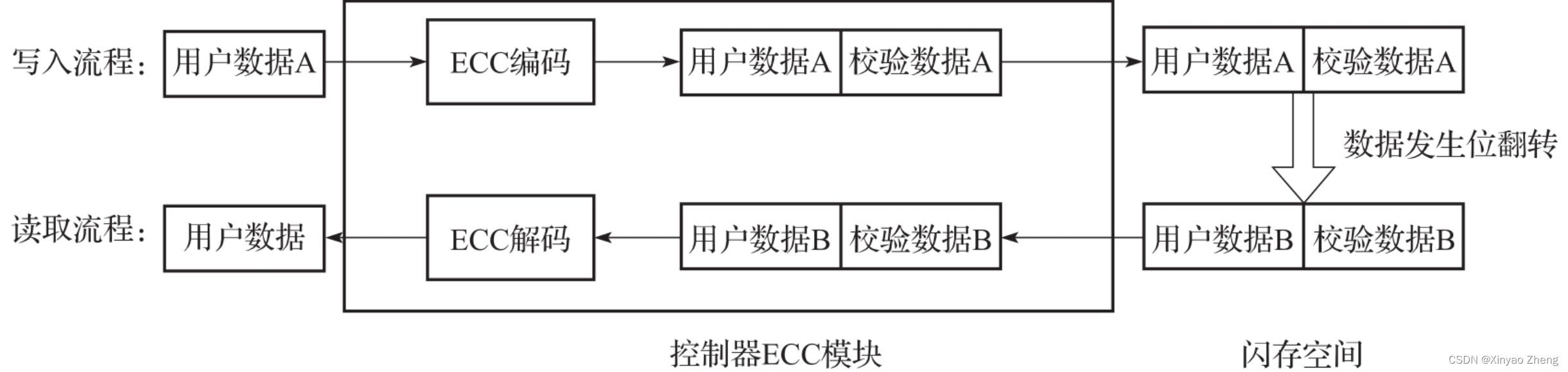

3.1 ECC纠错

SSD控制器的一个核心技术就是纠错算法。纠错模块不仅要纠错能力强、功耗低、性能好,还要面积小。

早期闪存(SLC或者MLC闪存)质量还是比较高的,发生位翻转的情况不是很多,当时主要用的纠错算法是BCH算法,它只支持硬解码。后来随着闪存变得越来越不可靠,更强的纠错算法LDPC成为SSD中的主流纠错算法,它不仅支持硬解码,还支持软解码,纠错能力与BCH相比上了一个台阶。

3.2 重读

所谓重读,就是当有错误通过ECC纠不过来时,固件再读一次或若干次。注意,重读不是简单地重复读取,而是需要改变施加在控制极的参考电压来重读。

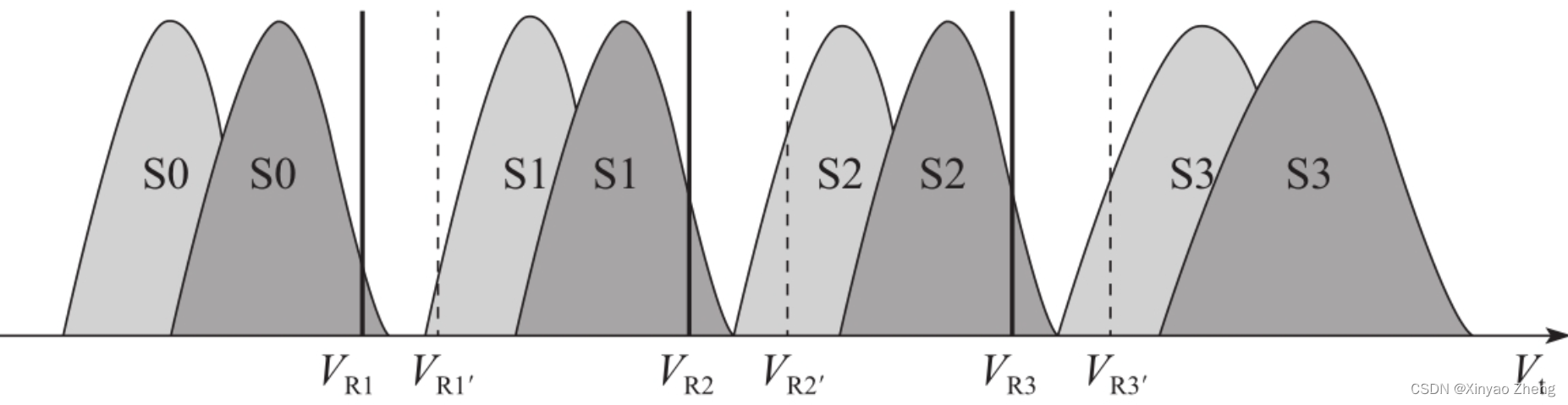

前面讲了,读干扰会导致一些闪存页阈值电压整体向右偏移(进入了额外的电子,阈值电压整体变大),以MLC为例,如图所示(从浅色右移到深色)。如果这个时候把读取的参考电压也相应增大,如VR1′,VR2′,VR3′,就能完美地把右移后的4个状态区分开来,各个状态不会和读取电压发生重叠,因此能正确把数据读取出来。

由于导致位翻转的因素很多,在实际场景中阈值电压的分布并不像上述介绍的读干扰一样只是简单右移,因此闪存厂家会提供若干种重读电压选项来帮用户应对各种复杂场景。重读也不是万能的,比如相邻状态如果重叠在一起,就很难通过重读来恢复了。

3.3 刷新

一旦检测到某个闪存页或者闪存块上面数据出错位的个数比较多(但ECC纠错模块能够很快纠过来),就提前把这个闪存页或者闪存块的数据搬移到新的地方,避免更多位发生翻转导致ECC纠错模块纠正不了。

3.4 RAID

固态硬盘内部本质就是一个闪存阵列,所以可以借鉴磁盘阵列技术来确保数据的完整性。固态硬盘的RAID一般采用RAID 5。

某个SSD的闪存阵列由4个Die构成,写入用户数据A~G的时候,通过异或操作生成校验数据(Parity):Parity=A+B+C+D+E+F+G(其中“+”为异或操作)把校验数据存储在闪存上,A~G和Parity组成一个RAID条带。

假设后续读取C失败,我们就可以通过读取该RAID条带上的其他数据来恢复C:C=Parity+A+B+D+E+F+G(其中“+”为异或操作)。

采用RAID 5的SSD只能恢复单个ECC不可纠错的数据,如果出现多个ECC不可纠错的错误数据,它就无能为力了。由于RAID 5采用了冗余纠错技术,需要额外的空间来存储冗余数据(校验数据),因此它必然会占用一部分闪存空间。

RAID需要软硬件共同实现:首先,SSD控制器需要支持RAID操作,即支持硬件异或功能,否则用软件去做异或运算会严重影响SSD的写入性能;其次,SSD固件需要利用控制器的RAID模块,综合闪存失效特征、硬件RAM资源、闪存资源(冗余空间)等因素,设计合适的RAID算法。

4. 三个与性能相关的闪存特性

针对闪存性能参数下降的问题,闪存厂商提供了一些特性,用于提升系统读写性能。这些特性的基本思想是提升闪存访问的并行度。

4.1 多Plane操作

数据传输必须串行的原因是一个Die只能挂在一个闪存通道上,即同一Die上的不同Plane共用闪存传输总线。一个Die的Plane越多,多Plane操作并发度越高,闪存读写性能越好。所以,现在闪存的一个发展方向是在一个Die上提供更多的Plane,其目的就是提升闪存的整体性能。

多Plane操作在执行时有一些限制,比如要求读写的每个Plane上的闪存页编号要一致,否则不能使用多Plane操作,因此多Plane操作只适合写入操作和顺序读操作,即只能提升SSD写入性能和顺序读取性能

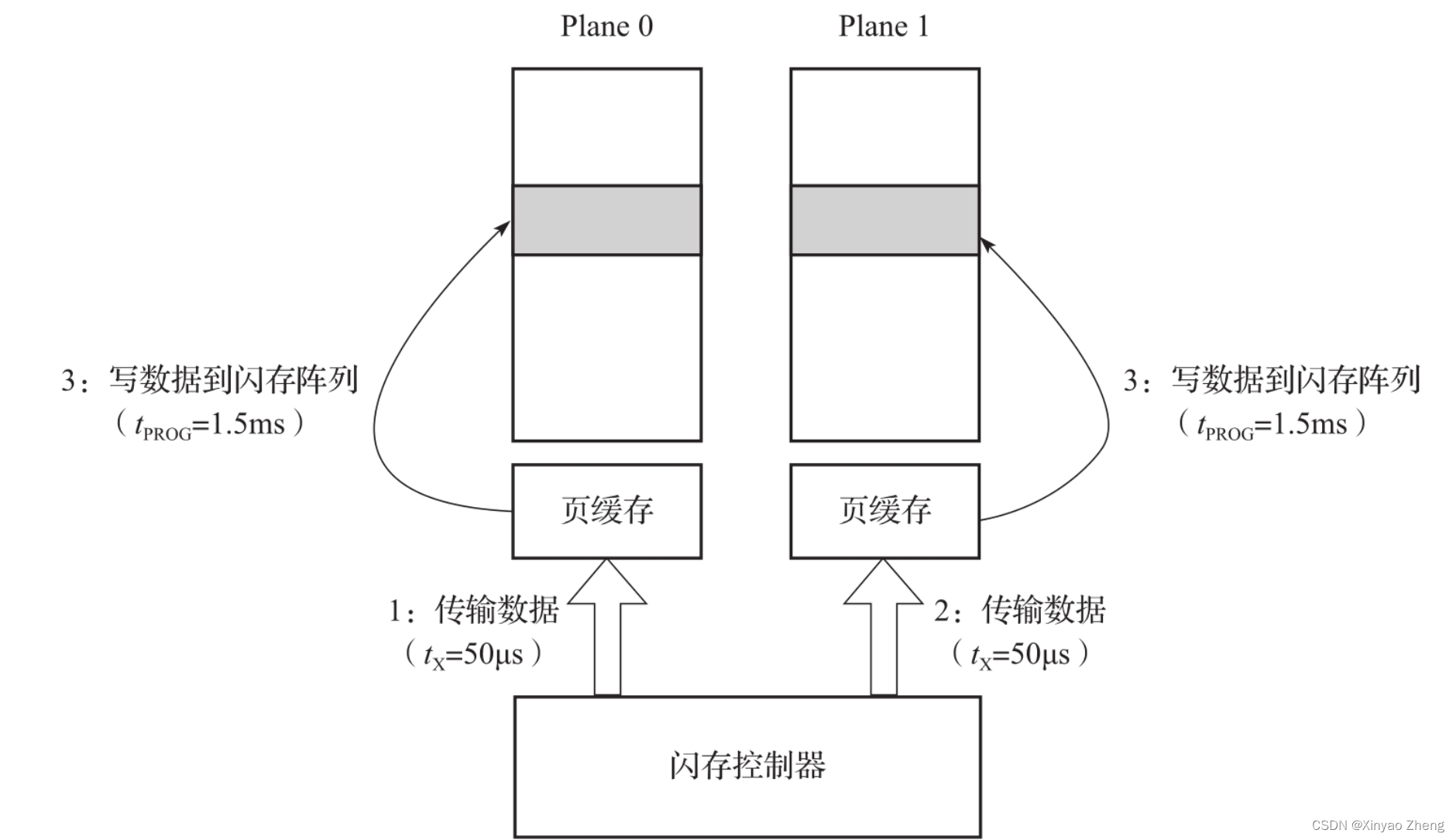

对多Plane写操作来说,SSD主控先把数据写入第一个Plane的闪存缓存中,数据保持在那里,并不立即写入闪存介质,等主控把同一个Die上的另外一个或者多个Plane上的数据传输到相应的闪存缓存中,再统一写入闪存介质。假设写入一个闪存页的时间为1.5ms,传输一个闪存页数据的时间为50μs:如果按原始的单Plane操作,写两个闪存页需要至少(1.5ms+50μs)×2;但如果按照多Plane操作,由于隐藏了一个闪存页的写入时间,写入两个闪存页只要1.5ms+50μs×2,缩减了近一半的时间,写入速度几乎翻番。

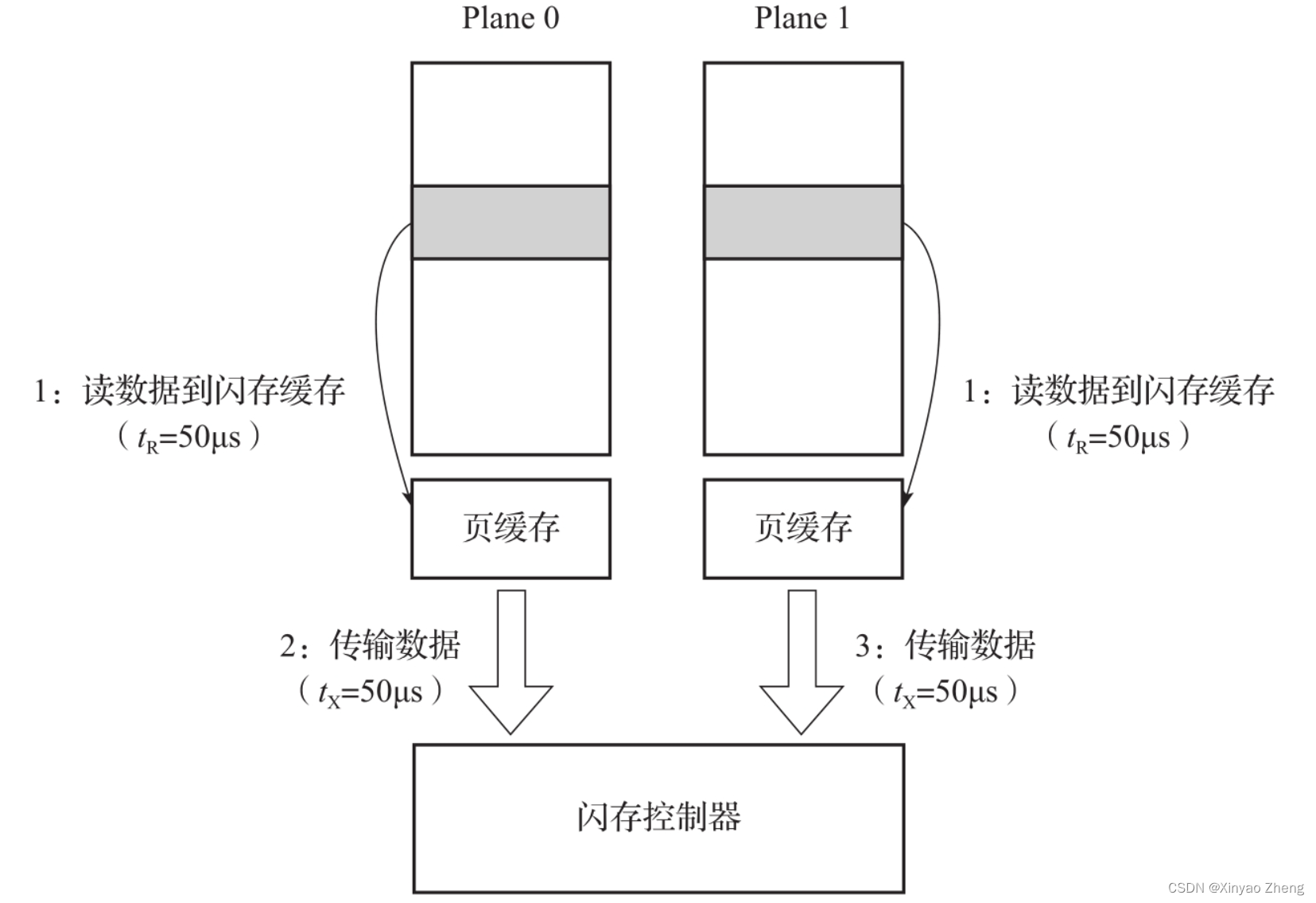

对多Plane读操作来说,不同Plane上的闪存页数据会在一个闪存读取时间内加载到各自的闪存缓存中,这样可用一个读取时间读取到多个闪存页的数据,读取速度加快。假设读取时间和数据传输时间一样,都是50μs,单Plane读取并传输两个闪存页需要50μs×4=200μs,多Plane则只需要50μs×2+50μs=150μs,时间为前者的75%,读取速度也有较大提升。

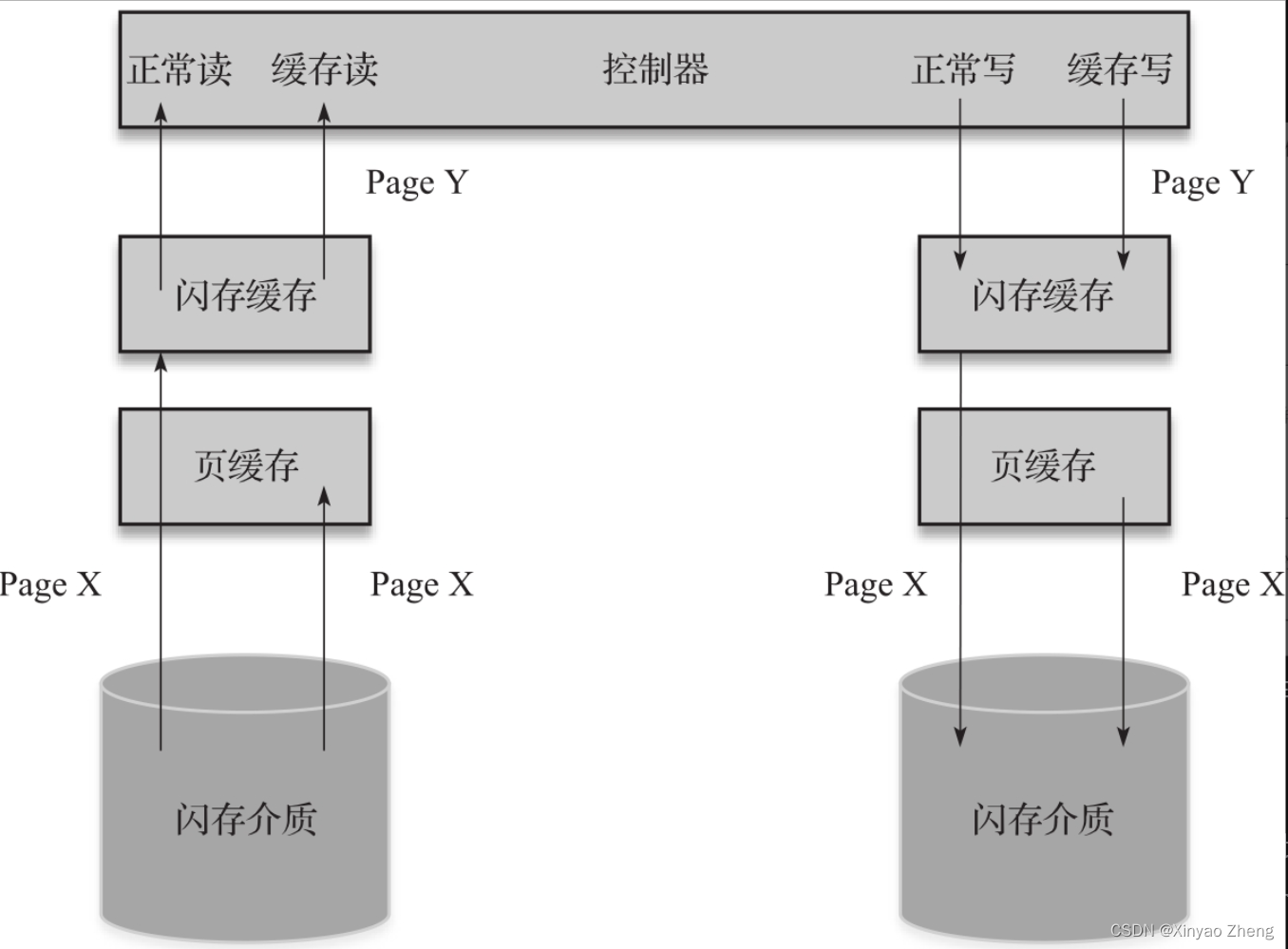

4.2 缓存读写操作

缓存读操作(左图)支持在将前一个闪存页(Page Y)数据传输给主控(闪存缓存→主控)的同时,从闪存介质将下一个主控需要读的闪存页(Page X)数据读取到页缓存(闪存介质→页缓存),这样前一个闪存页(Page Y)数据在闪存总线上传输的时间就可以隐藏在后一个闪存页(Page X)的读取时间里(或者相反,取决于哪个时间更长)。缓存写操作(右图)与之类似,它支持闪存在写前一个闪存页(Page X)数据的同时(页缓存→闪存介质),将下一个要写的闪存页(Page Y)数据传输到闪存缓存(主控→闪存缓存),这样下一个要写入闪存页的数据在闪存总线上传输的时间可以隐藏在前一个闪存页的写时间里。

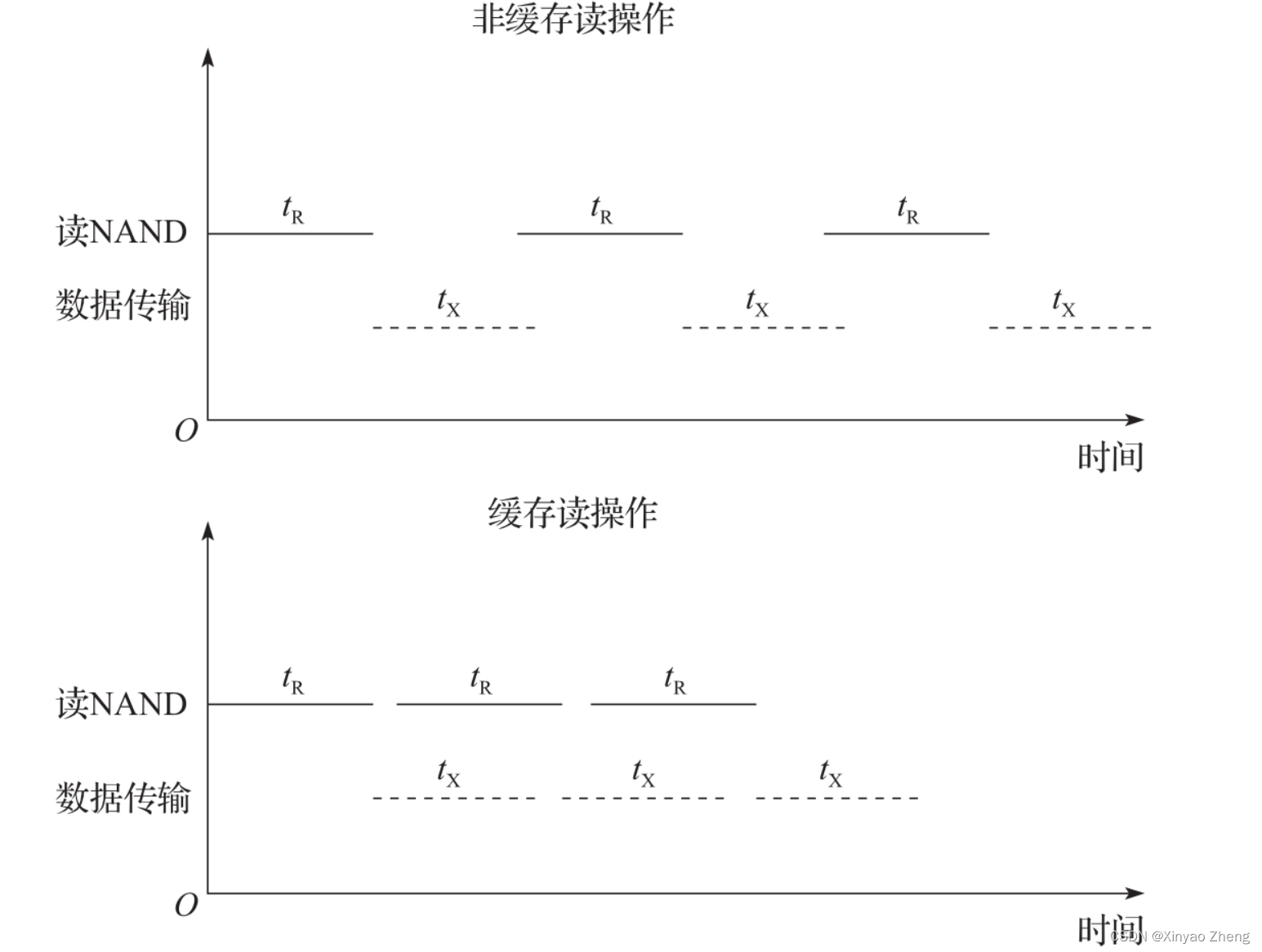

对非缓存读操作,读3个闪存页的总时间为(tR+tX)×3,其中tR是读取一个闪存页的时间,tX为一个闪存页数据在总线上传输的时间;对缓存读操作,读取3个闪存页的总时间大约为3×tR+tX(当tR>tX时)或者tR+3×tX(当tR<tX时),总的时间比非缓存读操作要少。可以看出,这样流水线式的写入或者读取方式能提升闪存的读写性能。

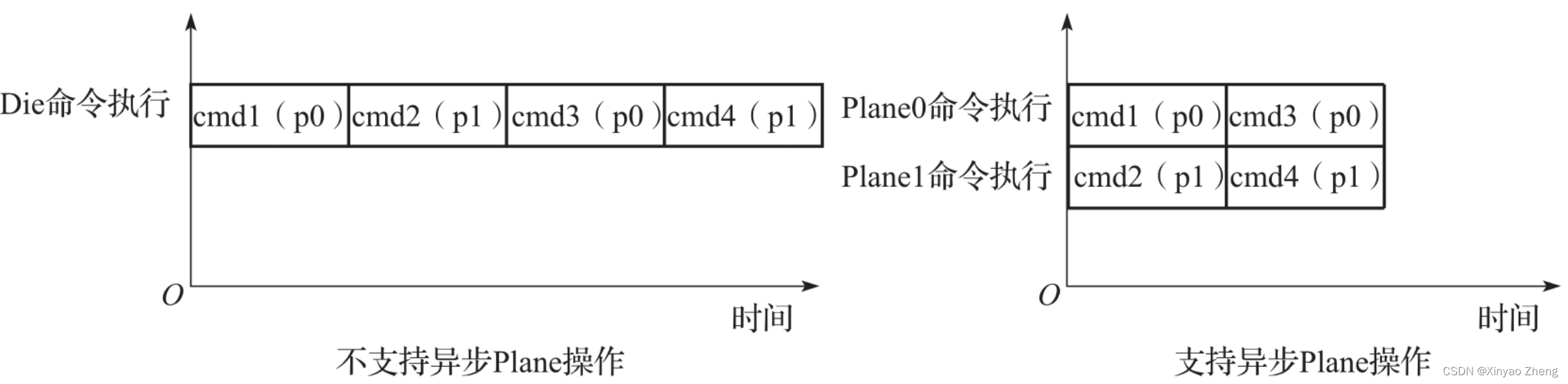

4.3 异步Plane操作

、多Plane操作在执行时有一些限制,比如要求读写的每个Plane上的闪存页编号要一致,对随机读取来说,很难遇到相邻的两笔读取落在“不同Plane上且具有同样编号的闪存页”上,多Plane操作大概率用不了。为解决这个问题,闪存厂商近年来引入了一个新的特性——异步Plane操作。

**异步Plane操作是指用户在随机读取同一个Die的时候,不需要等前一个Plane随机读操作完成,就可以把下一个随机读取命令发给别的Plane。**这个时候每个Plane表现得就像Die一样,可以独立执行随机读取命令。这样一个Die的随机并发度不是传统的“1”,而是Plane个数,因而大大提升了单Die的随机读取并行度,从而最终提升SSD等存储设备的随机读取性能。Plane个数越多,异步Plane操作并行度越高。

5 3D闪存

5.1 使用3D技术提高闪存密度

为提升闪存密度,闪存厂商想尽一切办法:逻辑上,他们让单个存储单元存储更多位数据,从之前的SLC到现在的QLC,存储单元存储的位数不断增加;物理上,他们使用更先进的制程,从早期几百纳米的工艺,到当前十几纳米的工艺。因为随着制程越来越先进,存储单元之间的距离越来越短,存储单元之间的干扰越来越严重,数据的可靠性也越来越难以保证。

通过闪存的堆叠技术,同样大小的晶圆能承载更多的数据,闪存厂商们在提升闪存密度的路上又找到新的思路。

5.2 3D闪存存储单元

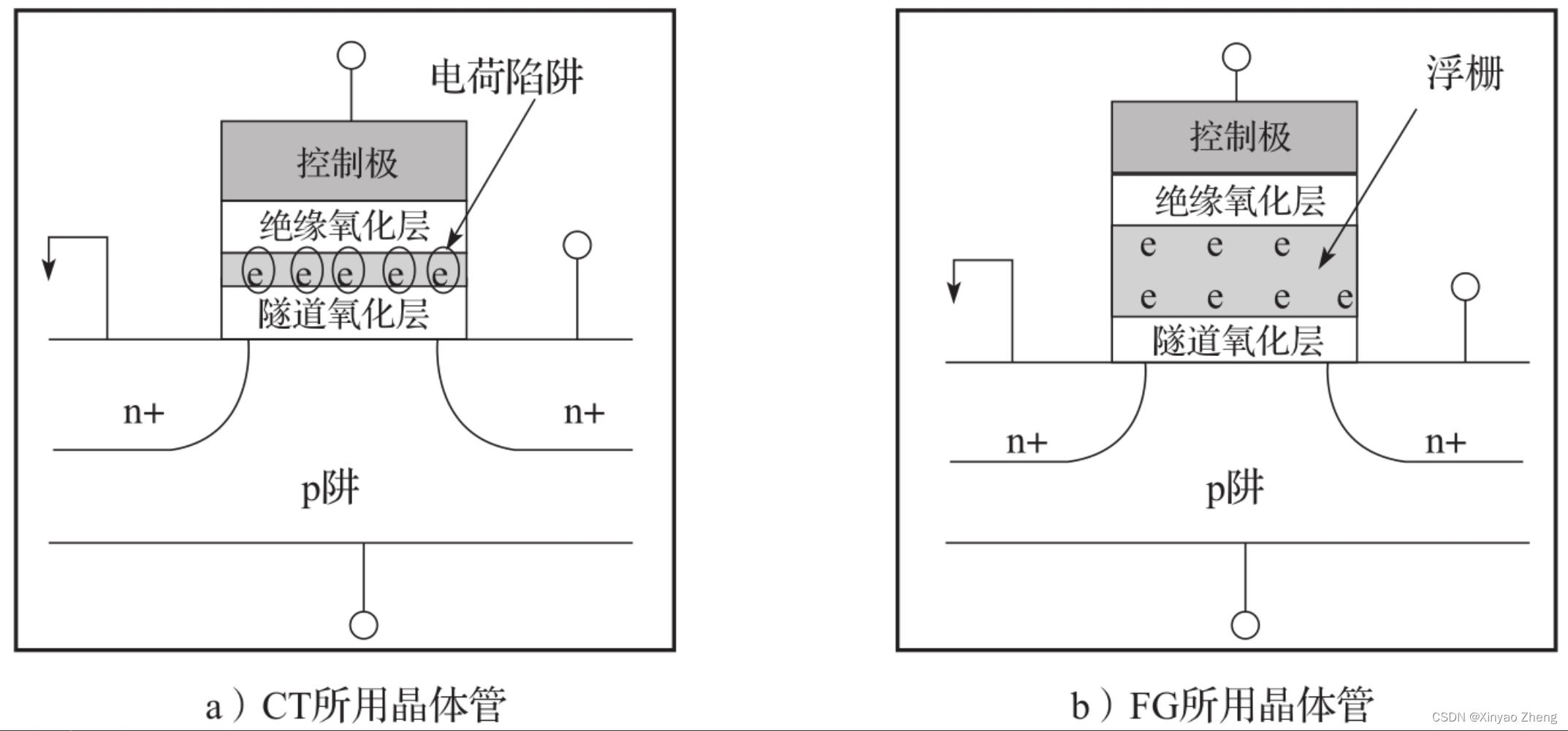

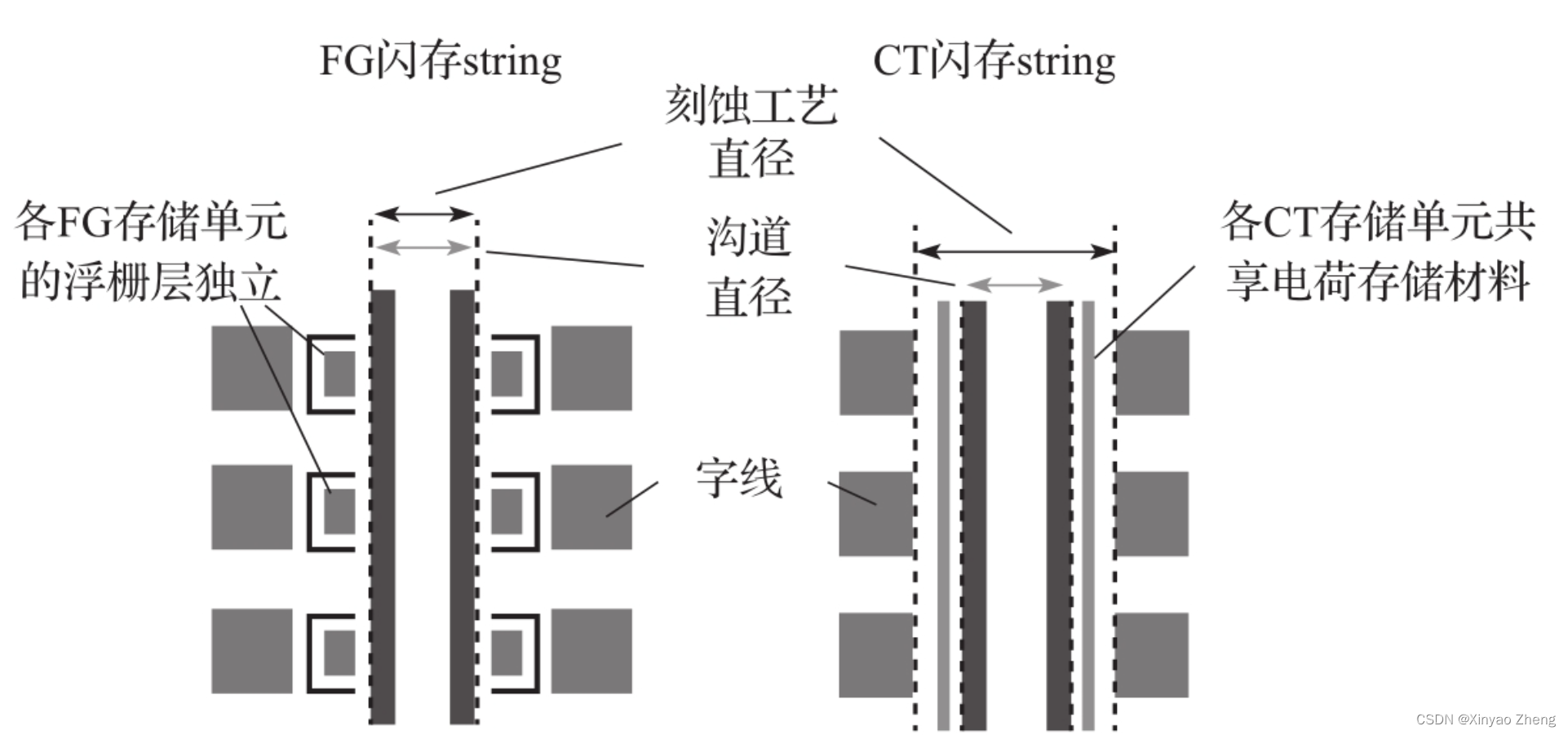

在2D时代,闪存存储单元是浮栅(Floating Gate,FG)晶体管;而到了3D时代,人们开始使用一种名为电荷捕获(Charge Trap,CT)的新型存储单元。

FG所用晶体管的浮栅极材料是导体,而CT所用晶体管存储电荷的是具有高电荷捕获密度的绝缘材料。CT捕获电子的材料上面就像布了很多陷阱,电子一旦陷入其中,就难以逃脱;而FG的浮栅极是导体材料,电子可以在里面自由移动。

相对FG,CT的一个优势就是:对隧道氧化层不敏感。隧道氧化层就算变薄或者因擦除导致老化,对CT影响也不大。任何两个存储单元的浮栅极都构成一个电容器,一个浮栅极里面电荷的变化,都会引起相邻存储单元浮栅极电荷的变化;而CT存储电荷的材料是绝缘体,相邻存储单元之间的耦合电容很小,因此从这个角度来看,存储单元之间干扰变弱。在编程(写入)方面,CT需要的电压比FG更小,这意味着对隧道氧化层的损伤变小,从而能提升闪存寿命。

在存储单元读写操作方面,CT和FG一样,但在擦除操作上,它们有一些不同:FG是使用的F-N隧道效应完成电子擦除的,而CT一般是采用热注入空穴的方式来消除存储在CT中的电子的。

5.3 3D闪存组织结构

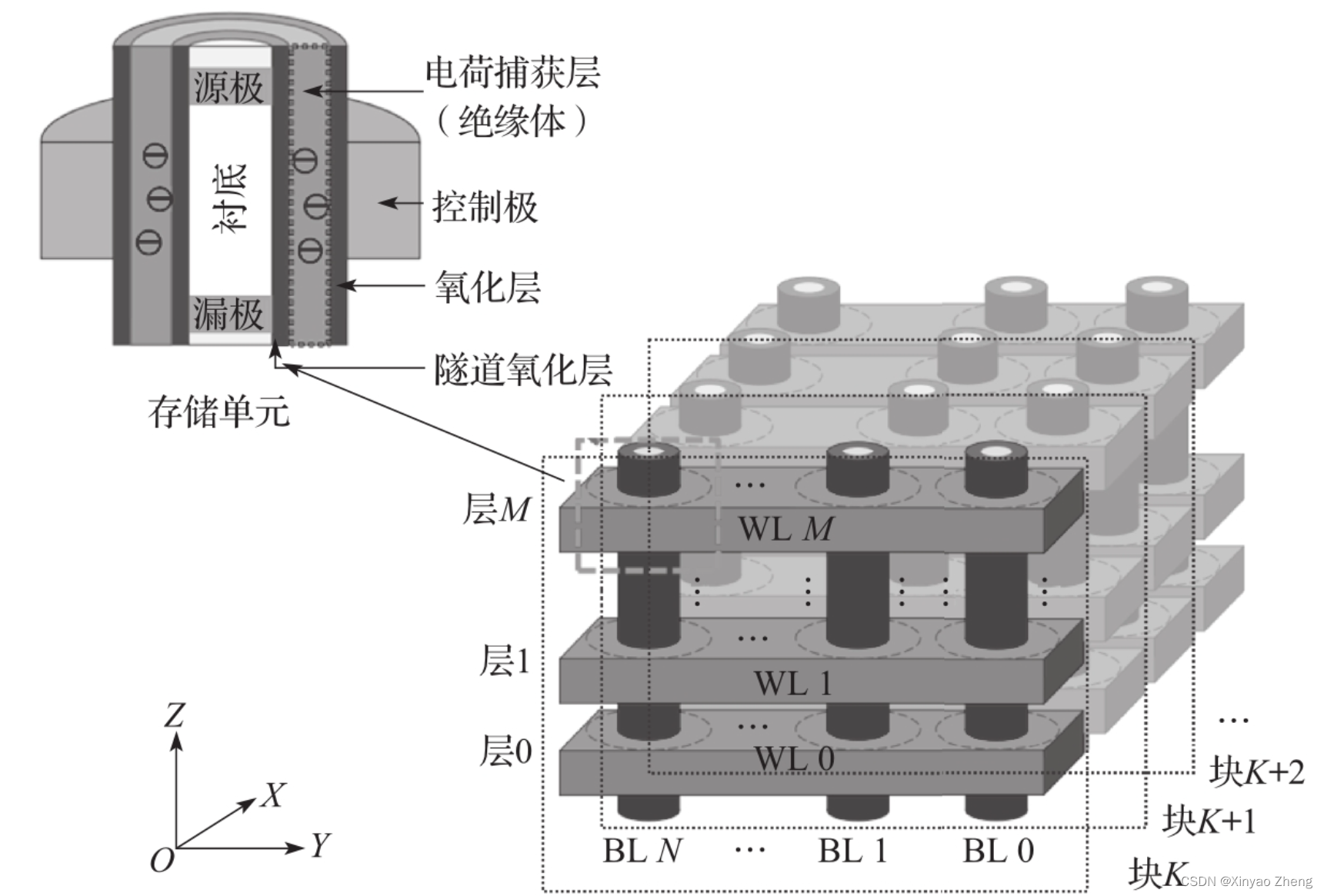

图中坐标轴Z和Y标注的一面就是3D闪存的一个闪存块,它由M+1条字线和N+1个位线组成。沿X方向排列更多的闪存块,就组成了一个3D闪存。圆柱内部,由不同层次的小圆柱构成,从里到外依次为衬底、隧道氧化层、电荷捕获层和氧化层。这些圆柱和每层的控制极(图中长方体)的交叉点就是一个个存储单元。

基于FG的闪存,一个闪存块位线上的各个存储单元共用衬底,但每个存储单元的浮栅层(即存储电荷的地方)都是独立的。它们必须是独立的,因为浮栅层是导体材料,如果所有存储单元共享浮栅层,那么电子来回游动,每个单元就存储不了数据了。对CT闪存来说,一个位线(图5-40所示的圆柱)的所有存储单元,除了控制极不一样,其他都是共享的,包括电荷捕获层。为什么它们可以共享电荷捕获层?因为CT中电子捕获材料是绝缘体,电子不容易从一个存储单元跑到另一个存储单元。对FG的圆柱来说,在浇筑时每个存储单元的浮栅层都要分别进行浇筑加工;而对CT的圆柱来说,圆柱从里到外,从上往下浇筑不同的材料就可以了,显然实现起来方便了很多。

CT这种组织结构虽说“施工方便”,但会引入新的数据保持问题。虽然说CT采用绝缘材料,电子在里面不易移动,但随着时间的推移,相邻存储单元之间还是会发生电子迁移的。因此,在数据保持问题上,除了传统的电子从存储层流失到衬底这个因素外,现在CT还有电子侧向流失的数据保持问题。

5.4 3D闪存外围电路架构

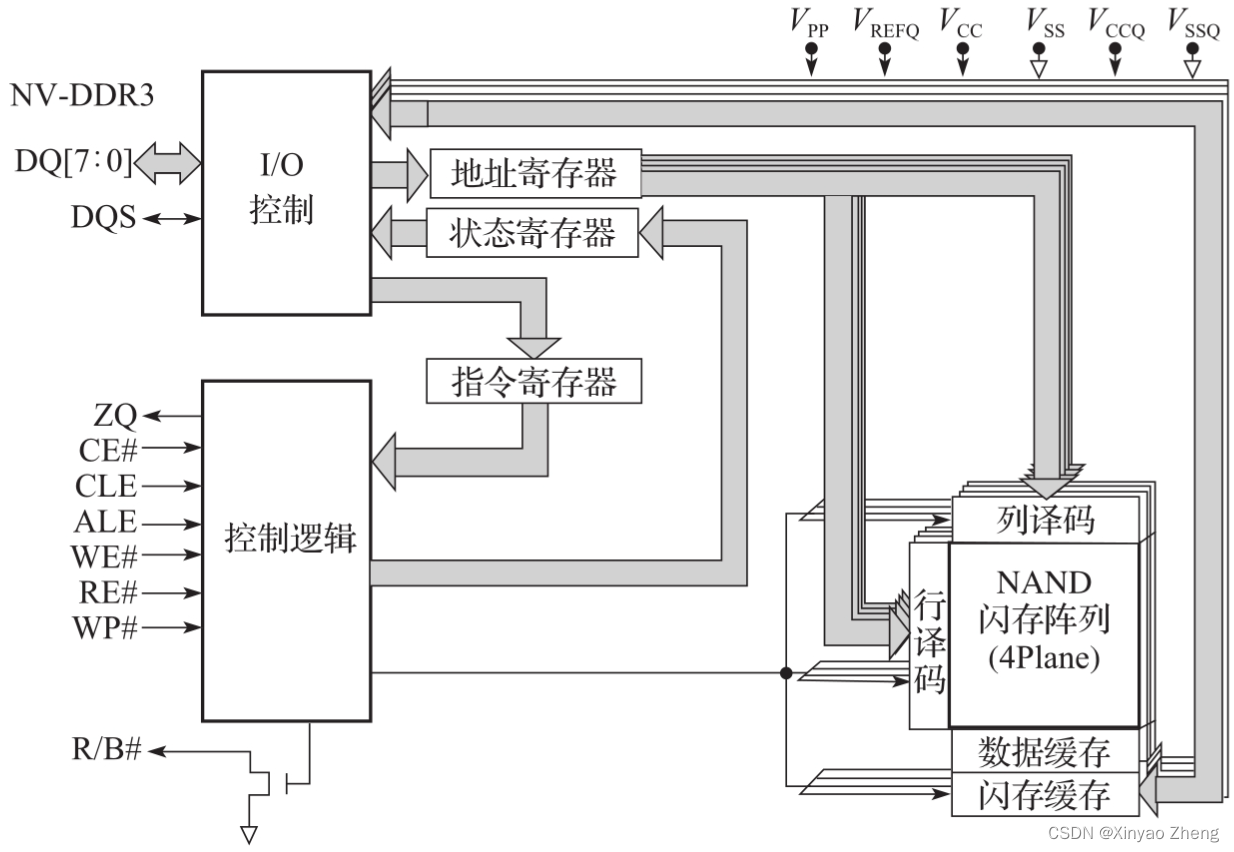

一个闪存,除了存储单元阵列外,还包括外围电路,用以实现控制逻辑、I/O控制、命令解析执行、电压控制、数据缓存等。

6153

6153

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?