文章目录

基础例程

1.CPU基础知识

1.1 ISA 指令集架构

-

架构:抽象层,软件无需做任何修改便可完全运行在任何一款遵循同一抽象层标准的处理器上。如:RISC-V x86

-

微架构:处理器具体的硬件实现。如:Intel AMD

-

精简指令集架构RISC

常见的有:RICV-V ARM

1.2 常见ISA

- x86 CISC:由8086发展而来

- power RISC:IBM 高端服务器

- ARM:英国,IP授权

- RISC-V 新的希望 www.riscv.org www.rvmcu.com

2.RISC-V基础知识

2.1 模块化的指令子集

- 可配置的通用寄存器组:通用寄存器个数、通用寄存器宽度、浮点寄存器组

- 规整的指令编码:通用寄存器索引位置不变(4种数据类型)

- 简介的存储器访问指令:load&store、仅支持小端格式、不支持地址自增/自减模式、采用松散存储器模式

- 高效的分支跳转指令:2条无条件跳转指令、6条带条件跳转指令、采用默认的静态分支预测机制

- 优雅的压缩指令子集

- 自定义指令扩展

常见的有:RICV-V ARM

2.2 RISC-V编码器特点

K.I.S.S

- 简洁的子程序调用

- 简洁的运算指令

- 无条件码执行

- 无分支延迟槽

- 无零开销硬件循环指令

硬件搭台,软件唱戏。hhhhhhh

2.3 RISC-V工具链

- riscv-tools: spike

- riscv-gnu-toolchain: riscv-gcc

2.4 RISC-V实现简介

- rocket core:面积和功耗远小于ARM-A7 chisel语言

- boom core:超标量乱序发射、乱序执行的处理器核

- freedom soc: lowrisc soc 硬件界的Linux hhh

3.蜂鸟E203处理器设计

3.1 设计原则

- 模块化核可重用i选哪个

- 面积最小化 数据通路

- 结构简单化

- 性能不追求极端:性能提倡够用就行 最高能效比

从模块到SoC,从硬件到软件,从运行到调试的完整解决方案

图1

3.2 处理器内核

图2

3.3 代码风格

Verilog RTL

- 使用标准的DFF模块例化生成寄存器

- 用assign 代替 if-else case(因为这俩 1优先级非并行,2不能传递不定态)

- 在数据通路上可使用不带reset的寄存器,只在控制通路上使用带reset的寄存器

- 信号名定义 注意使用英文缩写

- clk rst信号 禁止被用于其他的任何逻辑功能,只作为接入DFF的时钟和复位信号

4.指令流水线设计

4.1 经典五级流水线设计

- 取指IF

- 译码ID

- 执行EX

- 访存MEM:可能空闲

- 写回WB

4.2 蜂鸟

变长的流水线

- 取值

简化

预测机制:BPU RAS

连续取址:Mini-decode simple-BPU 生成下一条待取指令的PC

simple-BPU

最简单的静态预测 BTFN

JARL进行了一定优化

ICB总线

非对齐指令取址:剩余缓存 leftover buffer

- 执行

译码decode 组合逻辑

整数通用寄存器组 integer-regfile

CSR寄存器 处理器内部寄存器,使用其自身地址编码空间

访问采用专用的CSR读写指令

指令发射派遣 dispatch

valid-ready握手(解决资源冲突)

数据冲突:RAW WAR WAW

ALU单元

普通ALU运算 访存地址生成 分支预测解析 CSR读写控制 多周期乘除法器

共享一份实际的运算数据通路

- 交付

只用管:分支预测错误 和 中断与异常 造成的后续取消

- 写回

长指令写回仲裁:(OITF 先入先出的FIFO)顺序发射 乱序执行 顺序写回

混合机制 三种

5.存储器架构

5.1 存储器相关指令

load&store

"A"扩展指令

Fence指令 ~.I

5.2 存储器子系统结构

- AGU

ALU的以一个子单元,共享数据运算通路

通过ICB总线与LSU交互

- LSU

两组输入ICB总线接口:AGU EAI(高优先级)

三组输出ICB总线接口:ITCM DTCM BIU

通过写回接口将结果写回

出现访问异常,则传送异常给交付模块

- ICTM

64位单口SRAM 大小和及地址可配置(需要位宽转换)

优先级:IFU>LSU>外部访问

- DTCM

32位单口SRAM 大小和及地址可配置

优先级:LSU>外部访问

5.3 ICB总线

6.异常和中断

广义异常(包含中断)

6.1 中断定义

1. external interrupt

2. timer interrupt

3. software interrupt

4. debug interrupt

外部》软件》计时器

RISC-V 默认无法支持中断嵌套;可通过关断控制位实现软件嵌套

7.低功耗与可拓展性处理器

4.1 经典五级流水线设计

1.系统层面并不在程序中显示,只在工艺上实现

DSA 专用领域架构(与异构不同 如CPU+GPU)

EAI接口 协处理器

8.实战开发

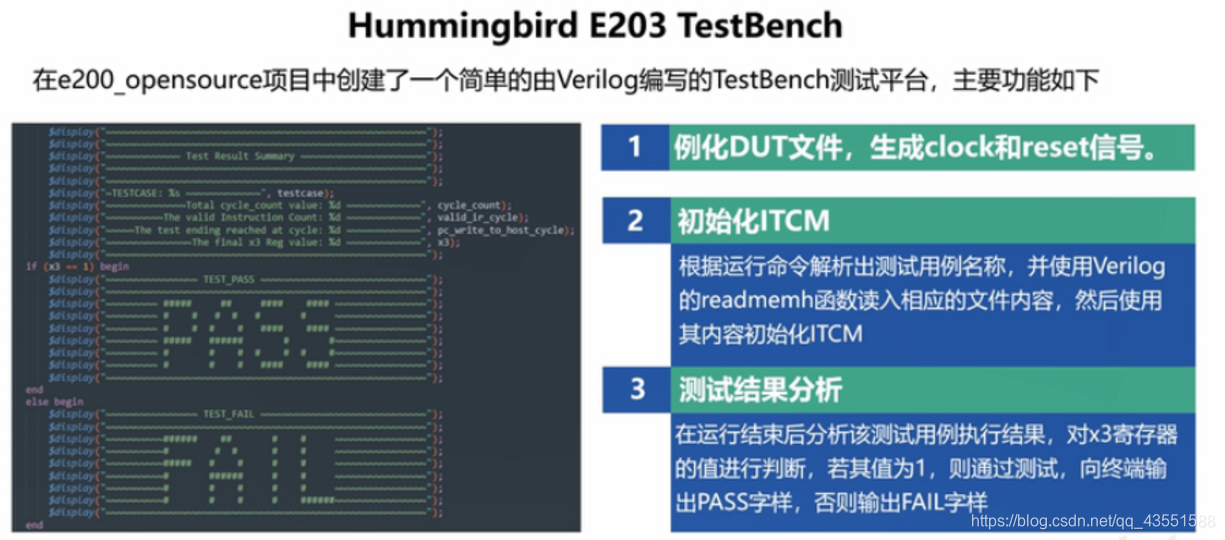

8.1 测试

hbird-e203-soc模块

实战

157

157

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?