计算机组成原理总目录

主存储器

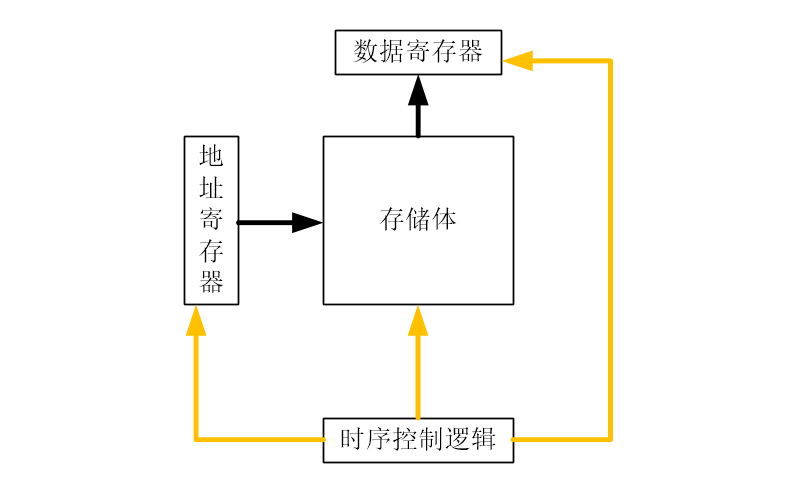

主存储器在结构上主要包括:存储体、地址寄存器、数据寄存器、(控制电路)、时序控制逻辑

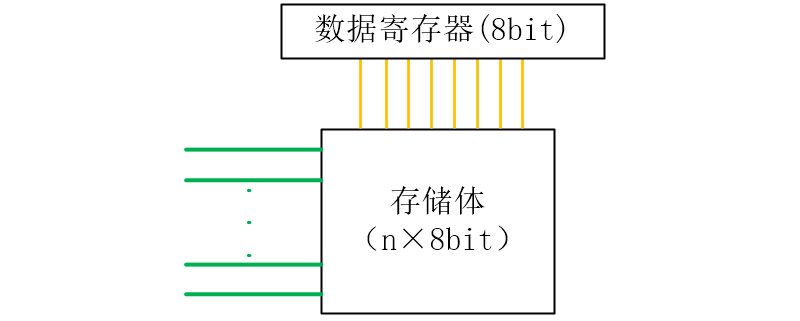

1. 数据寄存器

数据寄存器(MDR):用于存放从存储体所读取出来的数据,或者需要写入存储体的数据(Memory Data Register)

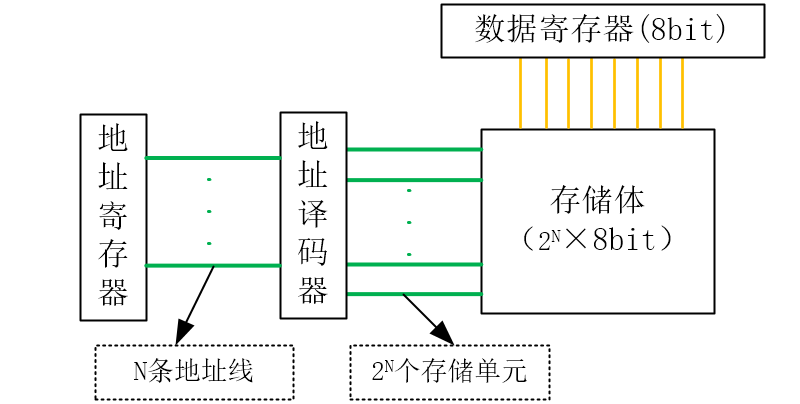

2. 地址寄存器

地址寄存器(MAR):用于存放所需要读写的地址(Memory Address Register)

因为存储体内包含多个存储体,如果一个存储单元对应一条地址线,那么当存储体数量很多的时候,就需要相同多的地址线

但这极大的增加了存储器的成本问题,而为了解决这个问题,于是就有了【地址译码器】,它能将N条地址线翻译成2N个地址

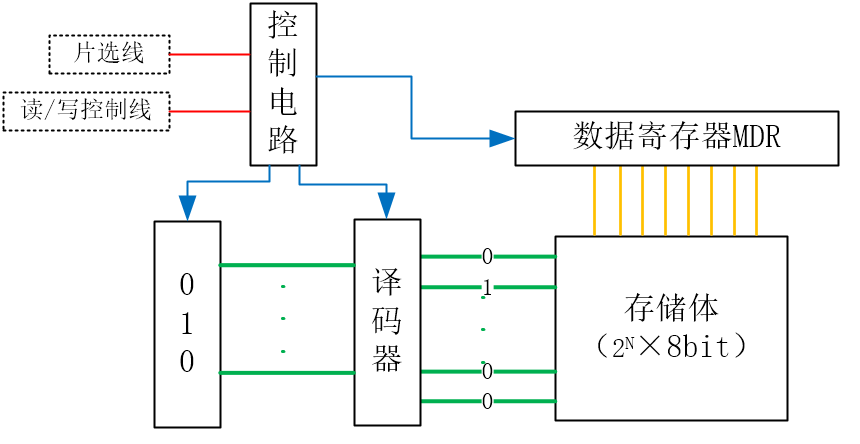

- 地址译码器:从翻译的结果来看,其实就是二进制转十进制的理解方式

例如:若地址寄存器存储的是【010】,则代表着3根地址线,经过地址译码器后有8根地址线,但只有第【2】根地址线会被导通

3. 控制电路

控制电路:用于控制主存储器的读写状态以及工作状态

- 片选线:用于控制当前存储体的工作状态,即开关功能

- 读/写控制线:控制当前的操作是读取数据还是写入操作

4. 时序控制逻辑

时序控制逻辑:按照时间为轴线的逻辑,控制对应操作的顺序

例如(仅做理解):

- 第一阶段(0s~1s),控制电路根据片选线和读写控制线进行一系列操作

- 第二阶段(2s~4s),如果是写操作,则打开数据寄存器的外部开关,使得数据导入数据寄存器中

- 第三阶段(4s-7s),将地址数据存储到地址寄存器中,并经过译码器导通第x根地址线

- 第四阶段(7s~9s),打开数据寄存器通向存储体的开关,使得数据寄存器的数据存入存储体中

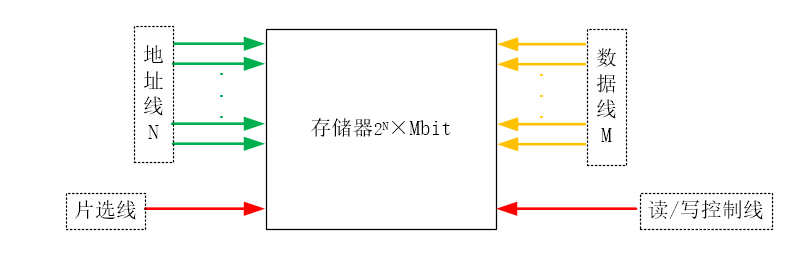

最后我们将存储器的结构进行简化表示,方便后序的学习

本文详细介绍了计算机主存储器的组成,包括存储体、地址寄存器、数据寄存器、控制电路和时序控制逻辑。地址寄存器存储读写地址,地址译码器用于解决大量存储体的地址线问题。控制电路管理和协调读写操作,时序控制逻辑确保操作顺序正确。此外,还讨论了数据寄存器和片选线的功能,以及简化存储器结构的方法。

本文详细介绍了计算机主存储器的组成,包括存储体、地址寄存器、数据寄存器、控制电路和时序控制逻辑。地址寄存器存储读写地址,地址译码器用于解决大量存储体的地址线问题。控制电路管理和协调读写操作,时序控制逻辑确保操作顺序正确。此外,还讨论了数据寄存器和片选线的功能,以及简化存储器结构的方法。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?