项目场景:

数字信号处理

问题描述

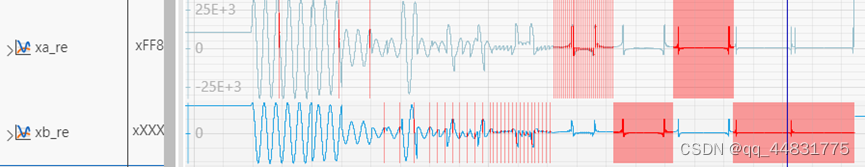

在对ADC模块进行故障注入的过程中,可能会产生ADC传入给FPGA的数据为高阻态的错误。而在verilog描述的FFT算法中,如果对这种情况不加已处理,那么数据寄存器中将会存入这个高阻态数据用以后续运算。而verilog中操作数是高阻态的运算结果将会也是高阻态。对于FFT运算,每一层运算的结果将会存入,并用于后续运算。这样一来,只要输入的数据中又一个为高阻态,那么FFT运算结果将只会是高阻态。

输出(FFT运算过程可视化

解决方案:

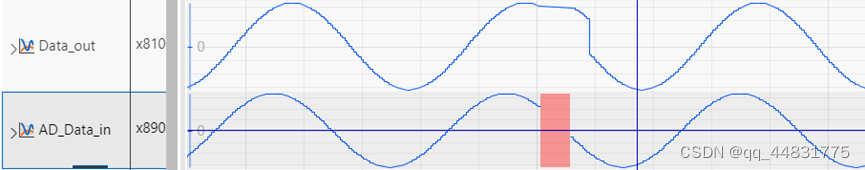

由于高阻态的本质是类似于悬空的特性,输入端高阻态意味着这条连线的电平又后面的接收模块决定。因此当输入为高阻态,应该保持上一个数据的电平,也就是重复输入上一个数据。基于此,只需判断AD传入数据是否为高阻态,是则重复上次数据输入。

此处又遇到了如何判别高阻态的问题。对于if a==16‘bz这样的条件语句,verilog中并不能正确判别。最终采用if |a的判别式,对a信号做或运算,将正常输入与高阻态和全零区分开,在单独处理全零的情况即可。

// A code block

always @(posedge SYSCLK) begin

if (|AD_Data_in) begin

AD_Data_reg[head] = AD_Data_in; // 将新数据存入缓冲区的头部

head = head + 1; // 移动头部指针

if (head == 8) // 如果头部指针到达缓冲区的末尾,将其重置为0

head = 0;

AD_Data_out_reg = AD_Data_reg[tail]; // 从缓冲区的尾部读出数据

tail = tail + 1; // 移动尾部指针

if (tail == 8) // 如果尾部指针到达缓冲区的末尾,将其重置为0

tail = 0;

end

else begin

if(AD_Data_in == 16'b0) begin

AD_Data_reg[head] = AD_Data_in; // 将新数据存入缓冲区的头部

head = head + 1; // 移动头部指针

if (head == 8) // 如果头部指针到达缓冲区的末尾,将其重置为0

head = 0;

AD_Data_out_reg = AD_Data_reg[tail]; // 从缓冲区的尾部读出数据

tail = tail + 1; // 移动尾部指针

if (tail == 8) // 如果尾部指针到达缓冲区的末尾,将其重置为0

tail = 0;

end

end

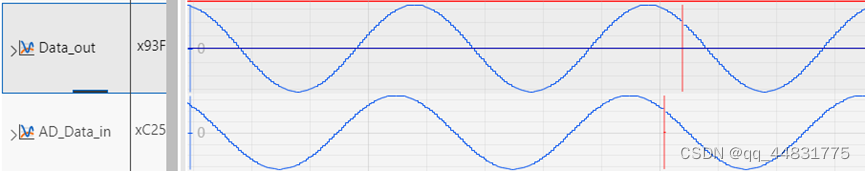

下图是正常输出

为方便观察 错误持续十个数据周期

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?