存储体系结构

简介

存储系统

- 存储器的容量由寻址策略决定

| 例如 |

|---|

| 采用16位地址,寻址空间为216=65536存储单元 |

- 大多数存储器是

字节可寻址(byte-addressable) - 每个存储单元的大小为

1字节 - 大多数计算机是以字为单位(word)检索或存储数据

- 常用缩写

- 1K=210(Kilo)

- 1M=220(Mega)

- 1G=230(Giga)

- 1T=240(Tera)

存储访问模式

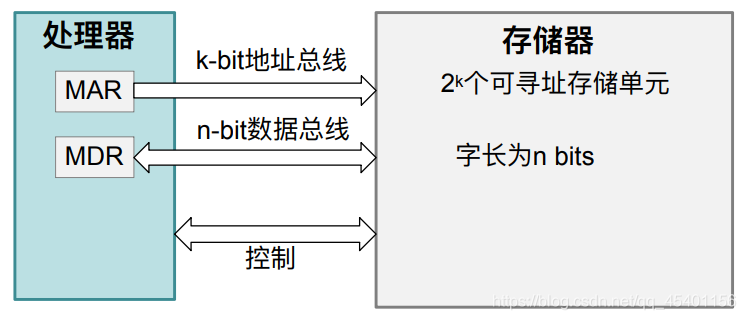

- 数据传输通过

MAR存储地址寄存器MDR存储数据寄存器

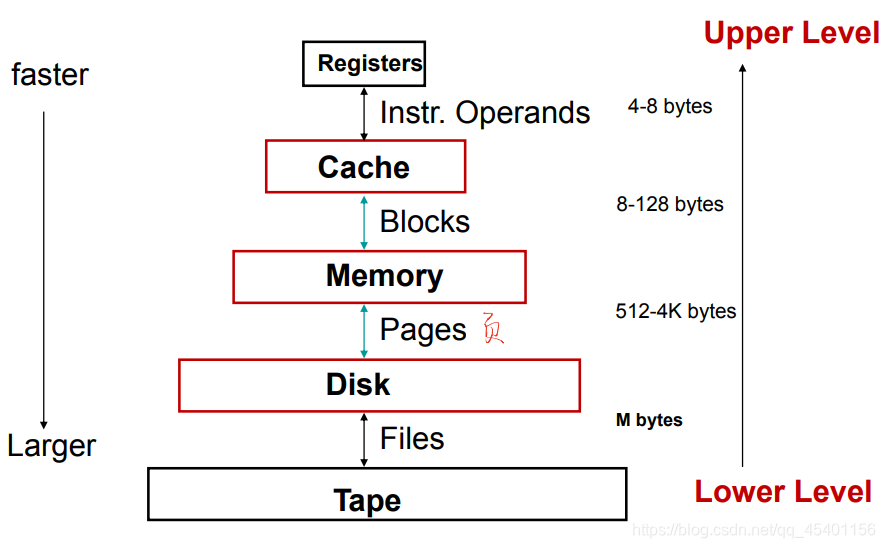

存储体系结构

局部性原理

程序局部性的访问地址空间

- 时间局部性

如果某个数据项被访问,那么在不久的将来他可能再次被访问- 例如,loop循环中的指令

- 空间局部性

如果某个数据项被询问,与它地址相邻的数据项可能很快也将被询问- 例如,顺序的指令执行,数组数据等

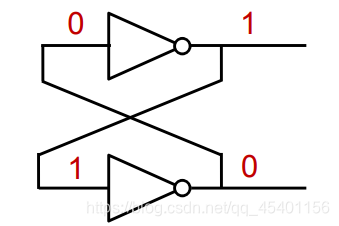

随机访问存储器(RAM)

- 稳定存储1bit数据的方式(交叉耦合反相器)

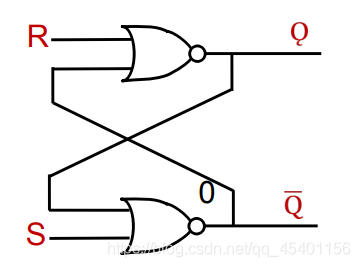

- 改变存储的值:S-R锁存器(用或非门替换反相器)

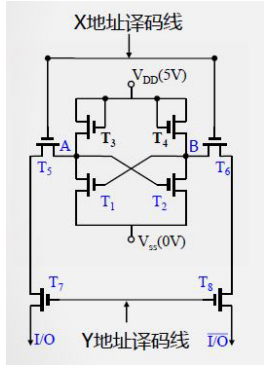

静态随机存储器(SRAM)

- 存储1bit数据需要6个晶体管

- 大多数芯片使用SRAM

- 一对弱交叉耦合反相器

- 数据存储在交叉耦合反相器

- X地址译码线

- Y地址译码线

- T1、T2保存数据

- T3、T4补充电荷

- T5、T6、T7、T8起开关作用

工作原理

- X地址译码线(行选通)

- T5、T6导通

- A点与位线(Bit line)相连

- Y地址译码线(列选通)

- T7、T8导通

- A点输出到I/O端

- 读写时,X和Y译码线需要同时有效

- 写1:

- I / O = 1 → A = 1 → T 2 通 → B = 0 → T 1 断 I/O=1 \rightarrow A=1 \rightarrow T2通 \rightarrow B=0 \rightarrow T1断 I/O=1→A=1→T2通→B=0→T1断

- I / O ‾ = 0 → B = 0 → T 1 断 − > A = 1 − > T 2 通 \overline{I/O}=0 \rightarrow B=0 \rightarrow T1断 -> A=1 -> T2通 I/O=0→B=0→T1断−>A=1−>T2通

- T1和T2形成稳态:A=1,B=0

- 读数据

- 通过外接在 I / O 和 I / O ‾ I/O和\overline{I/O} I/O和I/O之间的电流放大器中的电流方向来判断

- X与Y变成无效后,

由负载管T3和T4为T1和T2提供工作电流,使其保持稳定互锁- 因此保存数据必须通电

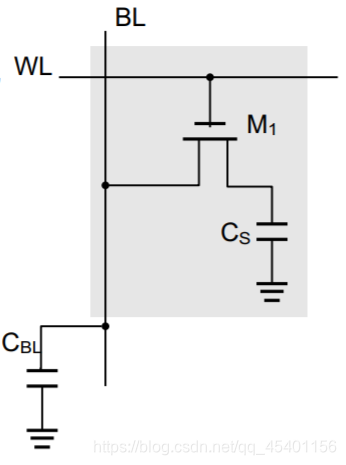

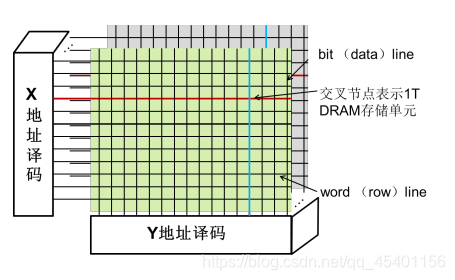

1-T DRAM存储单元

- 1个晶体管和一个存储电容存储数据,有电荷为1,否则是0

写数据

- 写0

BL=0V,WL=5V,M1通,Cs电荷减少为0,表示0 - 写1

BL=5V,WL=5V,M1通

Cs电荷增加,表示1

读数据

- 读0

BL=2.5V,WL=5V,M1通,感应BL线电势降低,低于2.5V,识别为0 - 读1

BL=2.5V,WL=5V,M1通,感应BL线电势升高,高于2.5V,识别为1

保存数据

- WL=0V,M1断,电荷保存在电容Cs中

交叉存取

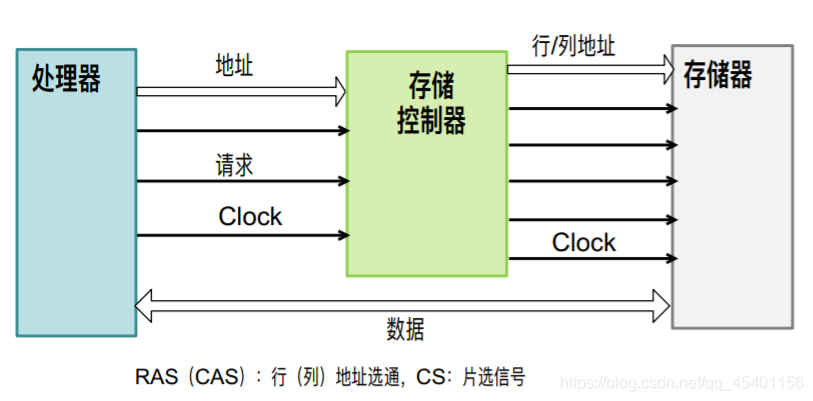

存储控制器

- 控制处理器与存储器间的交互

- DRAM需要频繁刷新,并且采用时分复用信号减少引脚数

- SRAM管理简单,通常不需要存储控制器

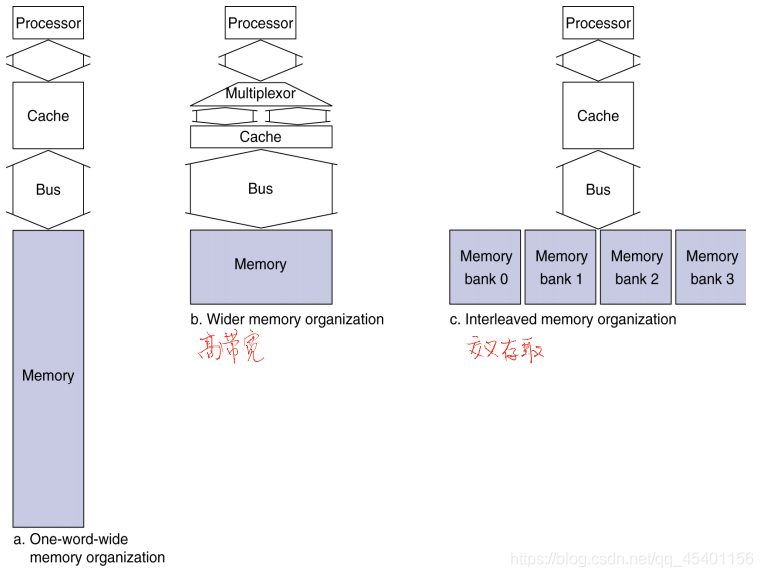

存储模块交叉存取

- 可以通过交叉访问几个存储模块(

连续的字在多个模块中交叉存储)来隐藏访问延迟 - 两个或多个兼容的存储模块

- 在一个存储模块中,采用多个并行访问的片

| 例如 |

|---|

| 八个存储模块,每个模块有八个片,实现8*8 bit的存储器总线 |

- 交叉存储可以在类似于双通道内存架构中实现

- 非交叉存储 VS 交叉存储

2669

2669

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?