DSP系列文章目录

第一章:DSP28337D-ePWM之Trip-Zone是什么

第二章:DSP28337D-ePWM之Trip-Zone实战测试

第三章:DSP28337D-IPC共享内存

第四章:DSP28337D-EMIF&ASRAM

文章目录

前言

最近在EMFI与FPGA/ASRAM的调试上可谓是一波三折。记录一下各种EMIF隐秘的角落(大坑)

一、EMIF配置注意事项

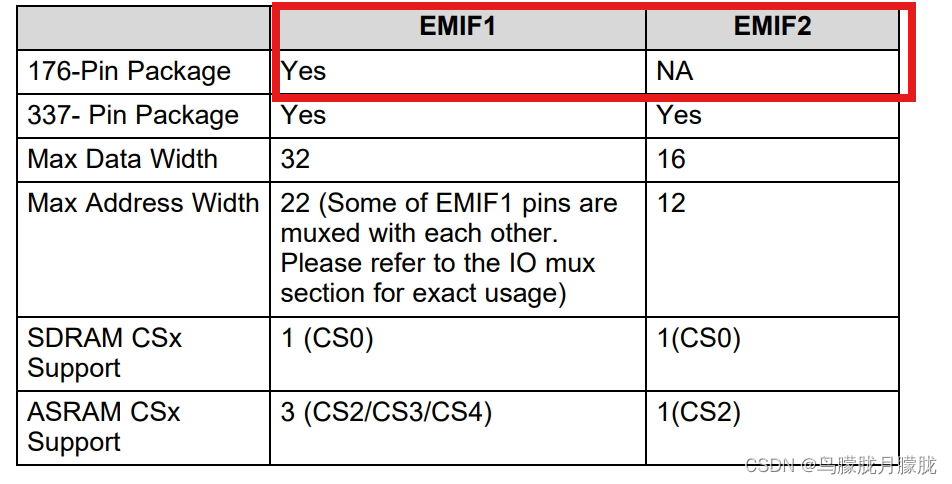

1、SDRAM与ASRAM的注意事项

CS0只能用于SDRAM

CS2/3/4只能用于ASRAM

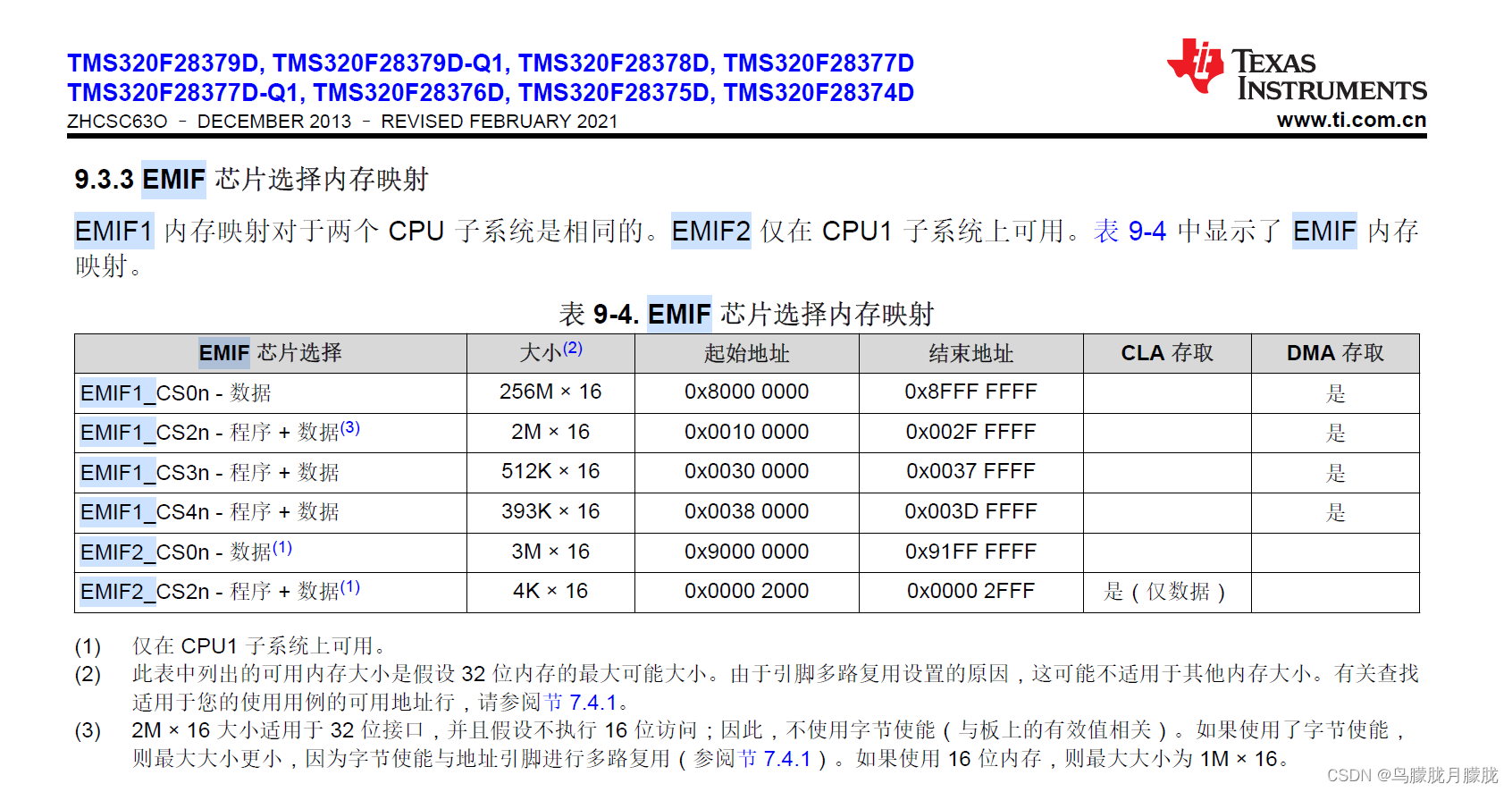

2、SDRAM与ASRAM的内存映射

使用EMIF1_CS3N,那么最大限值内存空间为512KB*2,地址总线位数最大为19位

3、SDRAM与ASRAM的地址总线对应关系

以16位ASRAM举例,EMIFA0-EMIFAX-------SRAMA1-SRAMAX+1,记住EM1BA1对应16位ASRAM的A0,这个很重要,敢A0对A0让你找问题找的怀疑人生

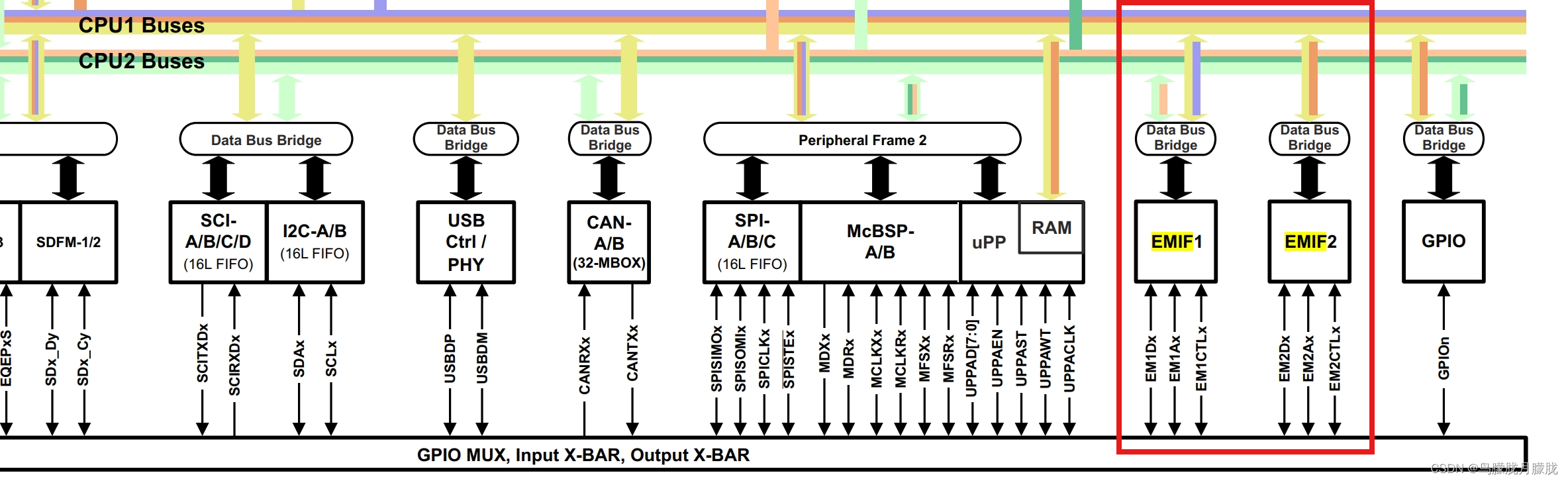

二、EMIF在CPU双核间的使用权限

EMIF2只能用在CPU2上,EMIF1在CPU1和CPU2上够可以

三、EMIF1及ASRAM实际使用

1、ASRAM基于EMIF1的基础配置及读写实测

直接上c2000ware源码,稍作修改,main.c代码如下:

//main.c

#include "device.h"

#include "driverlib.h"

// Defines

#define TEST_PASS 0xABCDABCD

#define TEST_FAIL 0xDEADDEAD

#define ASRAM_CS2_START_ADDR 0x100000

#define ASRAM_CS2_SIZE 0x8000

#define ASRAM_CS3_START_ADDR 0x300000

#define ASRAM_CS3_START_ADDR 0x380000

// Globals

uint16_t errCountGlobal = 0;

uint32_t testStatusGlobal;

uint32_t i;

// Function Prototypes

void setupEMIF1PinmuxAsync16Bit(void)

{

uint16_t i;

GPIO_setPinConfig(GPIO_28_EM1CS4N);

GPIO_setPinConfig(GPIO_29_EM1SDCKE);

GPIO_setPinConfig(GPIO_30_EM1CLK);

GPIO_setPinConfig(GPIO_31_EM1WEN);

GPIO_setPinConfig(GPIO_32_EM1CS0N);

GPIO_setPinConfig(GPIO_33_EM1RNW);

GPIO_setPinConfig(GPIO_34_EM1CS2N);

GPIO_setPinConfig(GPIO_35_EM1CS3N);

GPIO_setPinConfig(GPIO_36_EM1WAIT);

GPIO_setPinConfig(GPIO_37_EM1OEN);

// Selecting address lines.

GPIO_setPinConfig(GPIO_38_EM1A0);

GPIO_setPinConfig(GPIO_39_EM1A1);

GPIO_setPinConfig(GPIO_40_EM1A2);

GPIO_setPinConfig(GPIO_41_EM1A3);

GPIO_setPinConfig(GPIO_44_EM1A4);

GPIO_setPinConfig(GPIO_45_EM1A5);

GPIO_setPinConfig(GPIO_46_EM1A6);

GPIO_setPinConfig(GPIO_47_EM1A7);

GPIO_setPinConfig(GPIO_48_EM1A8);

GPIO_setPinConfig(GPIO_49_EM1A9);

GPIO_setPinConfig(GPIO_50_EM1A10);

GPIO_setPinConfig(GPIO_51_EM1A11);

GPIO_setPinConfig(GPIO_52_EM1A12);

GPIO_setPinConfig(GPIO_86_EM1A13);

GPIO_setPinConfig(GPIO_87_EM1A14);

// Selecting data lines.

GPIO_setPinConfig(GPIO_63_EM1D21);

GPIO_setPinConfig(GPIO_64_EM1D20);

GPIO_setPinConfig(GPIO_65_EM1D19);

GPIO_setPinConfig(GPIO_66_EM1D18);

GPIO_setPinConfig(GPIO_67_EM1D17);

GPIO_setPinConfig(GPIO_68_EM1D16);

GPIO_setPinConfig(GPIO_69_EM1D15);

GPIO_setPinConfig(GPIO_70_EM1D14);

GPIO_setPinConfig(GPIO_71_EM1D13);

GPIO_setPinConfig(GPIO_72_EM1D12);

GPIO_setPinConfig(GPIO_73_EM1D11);

GPIO_setPinConfig(GPIO_74_EM1D10);

GPIO_setPinConfig(GPIO_75_EM1D9);

GPIO_setPinConfig(GPIO_76_EM1D8);

GPIO_setPinConfig(GPIO_77_EM1D7);

GPIO_setPinConfig(GPIO_78_EM1D6);

GPIO_setPinConfig(GPIO_79_EM1D5);

GPIO_setPinConfig(GPIO_80_EM1D4);

GPIO_setPinConfig(GPIO_81_EM1D3);

GPIO_setPinConfig(GPIO_82_EM1D2);

GPIO_setPinConfig(GPIO_83_EM1D1);

GPIO_setPinConfig(GPIO_85_EM1D0);

// Setting DQM and Bank Select lines.

GPIO_setPinConfig(GPIO_88_EM1DQM0);

GPIO_setPinConfig(GPIO_89_EM1DQM1);

GPIO_setPinConfig(GPIO_90_EM1DQM2);

GPIO_setPinConfig(GPIO_91_EM1DQM3);

GPIO_setPinConfig(GPIO_92_EM1BA1);

GPIO_setPinConfig(GPIO_93_EM1BA0);

GPIO_setPinConfig(GPIO_94_EM1A21);

// Setup async mode and enable pull-ups for Data pins.

for(i=69; i<=85;i++)

{

if(i != 84)

{

GPIO_setPadConfig(i, GPIO_PIN_TYPE_PULLUP);

GPIO_setQualificationMode(i, GPIO_QUAL_ASYNC);

}

}

}

void main(void)

{

uint numi = 2;

uint16_t errCountLocal;

EMIF_AsyncTimingParams tparam;

testStatusGlobal = TEST_FAIL;

// Initialize device clock and peripherals.

Device_init();

// Disable all the interrupts.

DINT;

// Setup GPIO by disabling pin locks and enabling pullups.

Device_initGPIO();

// Initialize PIE and clear PIE registers. Disables CPU interrupts.

Interrupt_initModule();

// Initialize the PIE vector table with pointers to the shell Interrupt Service Routines (ISR).

Interrupt_initVectorTable();

// Configure to run EMIF1 on full Rate. (EMIF1CLK = CPU1SYSCLK)

SysCtl_setEMIF1ClockDivider(SYSCTL_EMIF1CLK_DIV_1);

// Grab EMIF1 For CPU1.

EMIF_selectMaster(EMIF1CONFIG_BASE, EMIF_MASTER_CPU1_G);

// Disable Access Protection. (CPU_FETCH/CPU_WR/DMA_WR)

EMIF_setAccessProtection(EMIF1CONFIG_BASE, 0x0);

// Commit the configuration related to protection. Till this bit remains set, contents of EMIF1ACCPROT0 register

EMIF_commitAccessConfig(EMIF1CONFIG_BASE);

// Lock the configuration so that EMIF1COMMIT register can't be changedany more.

EMIF_lockAccessConfig(EMIF1CONFIG_BASE);

// Configure GPIO pins for EMIF1.

setupEMIF1PinmuxAsync16Bit();

// Configures Normal Asynchronous Mode of Operation.

EMIF_setAsyncMode(EMIF1_BASE, EMIF_ASYNC_CS2_OFFSET, EMIF_ASYNC_NORMAL_MODE);

// Disables Extended Wait Mode.

EMIF_disableAsyncExtendedWait(EMIF1_BASE, EMIF_ASYNC_CS2_OFFSET);

// Configure EMIF1 Data Bus Width.

EMIF_setAsyncDataBusWidth(EMIF1_BASE, EMIF_ASYNC_CS2_OFFSET, EMIF_ASYNC_DATA_WIDTH_16);

// Configure the access timing for CS2 space.

tparam.rSetup = 0;

tparam.rStrobe = 3;

tparam.rHold = 0;

tparam.turnArnd = 0;

tparam.wSetup = 0;

tparam.wStrobe = 1;

tparam.wHold = 0;

EMIF_setAsyncTimingParams(EMIF1_BASE, EMIF_ASYNC_CS2_OFFSET, &tparam);

// Checks basic RD/WR access to CS2 space.

while(numi --)//反复读写测试

{

uint16_t memReadData = 0;

uint16_t memWriteData = 0;

uint16_t *memPtr;

uint16_t i;

memPtr = (uint16_t *)ASRAM_CS2_START_ADDR ;

for(i = 0; i < ASRAM_CS2_SIZE ; i++)//写

{

*memPtr++ = memWriteData;

memWriteData += 1;

}

memPtr = (uint16_t *)ASRAM_CS2_START_ADDR ;

for(i = 0; i < ASRAM_CS2_SIZE ; i++)//读一

{

memReadData = *memPtr;

printf("readdata:%u", memReadData );

memPtr++;

memWriteData += 1;

}

printf("\r\n");

printf("emif test over\r\n");

}

}

中间自己测试发现了奇怪现象,初始化所有EMIF管脚,配置ASRAM-CS2后,执行CS2对应地址空间操作的时候,不仅CS2有使能现象,CS0也有,虽然不影响写入读取,但严重激发了我对这个片子的设计不合理,并提出了质疑!!!

1.1、现象展示:

2、SDRAM基于EMIF1的基础配置及读写实测

等我更新,先空着

2.1、现象展示:

4、原理解释

总结

本期先展示ASRAM的测试及填坑记录,后期在更新SDRAM的大坑

1642

1642

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?