说明

- 博客作为笔记备份,不定时更新

- 参考内容为《计算机组成原理(第3版)》唐朔飞 高等教育出版社;王道考研《计算机组成原理考研复习指导2023》

- 文中的例题摘自王道考研《计算机组成原理考研复习指导2023》,大多是我个人认为较为典型的题目以及错题的部分整理

文章目录

CPU功能和基本结构

1. CPU功能

1.1 概述

- CPU 由运算器和控制器组成。运算器负责协调并控制计算机各部件执行程序的指令序列,包括取指、分析指令、执行指令;运算器对数据进行加工

1.2 CPU的具体功能

- 指令控制:完成取指令、分析指令、执行指令的操作,即程序的顺序执行

- 操作控制:一条指令的功能往往由若干操作信号的组合来实现。CPU管理并产生由内存取出的每条指令的操作信号,把各种操作信号送往相应的部件,从而控制这些部件按指令要求进行动作

- 时间控制:对各种操作加以时间上的控制。时间控制要求为每条指令按时间顺序提供应有的控制信号

- 数据加工:对数据进行算术和逻辑运算

- 中断处理:对计算机运行过程中出现的异常情况和特殊请求进行处理

2. CPU基本结构

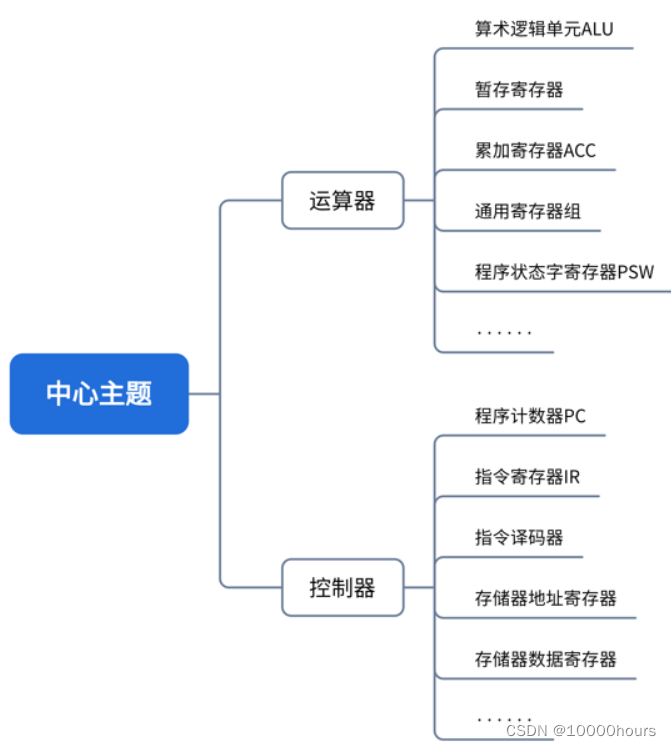

2.1 CPU结构框图

2.2 运算器

- 功能:接收从控制器送来的命令并执行相应的动作,对数据进行加工和处理,是计算机对数据进行加工处理的中心

- 基本组成

- 算术逻辑单元ALU:主要功能是进行算术/逻辑运算

- 暂存寄存器:用于暂存从主存读来的数据,该数据不能存放在通用寄存器中,否则会破坏其原有内容。暂存寄存器对应用程序员透明

- 累加寄存器ACC:是一个通用寄存器,用于暂存ALU运算的结果信息,可以作为加法运算的一个输入端

- 通用寄存器组:例如AX、BX、CX、DX、SP等,用于存放操作数(包括源操作数、目的操作数和中间结果)和各种地址信息。SP是堆栈指针

- 程序状态字寄存器PSW:保留由算术逻辑运算指令或测试指令的结果而建立的各种状态信息,例如OF、SF、ZF、CF等。PSW中的这些位参与并决定微操作的形成

- 移位器:对操作数或运算结果进行移位运算

- 计数器:控制乘除运算的操作步数

2.3 控制器

- 功能:控制器的基本功能是取指、分析执行、执行指令,每条指令的执行是由控制器发出的一组微操作实现的。控制器是整个系统的指挥中枢

- 两种类型的控制器:硬布线控制器和微程序控制器

- 基本组成

- 程序计数器PC:指出下一条指令在主存中的存放地址,CPU根据PC中的内容去主存中取指令。因程序中的指令通常是顺序执行的,因此PC有自增功能

- 指令寄存器IR:保存当前正在执行的指令

- 指令译码器:仅对操作码字段进行译码,向控制器提供特定的操作信号

- 存储器地址寄存器MAR:存放要访问的主存单元的地址

- 存储器数据寄存器MDR:存放向主存写入的信息或从主存中读出的信息

- 时序系统:产生各种时序信号,它们都由统一时钟(CLOCK)分频得到

- 微操作信号发生器:根据IR、PSW的内容以及时序信号,产生控制整个计算机系统所需的各种控制信号,其结构有组合逻辑型和存储逻辑型两种

- 工作原理:根据指令操作码、指令的执行步骤(微命令序列)和条件信号形成当前计算机各部件要用到的控制信号,计算机各硬件系统在这些控制信号的控制下协同运行,产生预期的结果

2.4 CPU的寄存器

- CPU的寄存器大致可分为两类:用户可见寄存器;控制和状态寄存器

- 用户可见寄存器

- 通用寄存器:可用于存放操作数,也可作为满足某种寻址方式所需的寄存器

- 数据寄存器:存放操作数,位数应该满足多数数据类型的数值范围,有些机器允许使用两个连续的寄存器存放双倍字长的值。还有些机器的数据寄存器只能用于保存数据,不能用于操作数地址的计算

- 地址寄存器:存放地址,其本身可以具有通用性,也可用于特殊的寻址方式(例如段指针、栈指针等)

- 条件码寄存器:存放条件码,它们对用户来说是部分透明的

- 控制和状态寄存器(在一些机器里,大部分这类寄存器对用户是透明的)

- MAR:存储器地址寄存器,存放将被访问的存储单元的地址

- MDR:存储器数据寄存器,存放欲存入存储器的数据或最近从存储器读出的数据

- PC:程序计数器

- IR:指令寄存器

- MAR、MDR、PC、IR、CPU和主存可以交换信息

3. 例题

关于“n位CPU”

- (

P

201

6

P_{201}6

P2016)在所谓的n位CPU中,n指的是()

A. 地址总线线数 B. 数据总线线数 C. 控制总线线数 D. I/O线数

解答:数据总线的位数与处理器位数相同,它表示CPU一次能处理的数据的位数,即CPU的位数

错误原因:错选A

各种寄存器的位数

- (

P

202

11

P_{202}11

P20211)程序计数器的位数取决于()

A. 存储器的容量 B. 机器字长 C. 指令字长 D. 都不对

解答:程序计数器中存放的是指令在主存中的地址,所以PC的位数与存储器地址的位数相等,而存储器地址取决于存储器的容量。选A - (

P

202

12

P_{202}12

P20212)指令寄存器的位数取决于()

A. 存储器的容量 B. 机器字长 C. 指令字长 D. 存储字长

解答:指令将寄存器存放当前正在执行的指令,所以其位数取决于指令字长。选C - (

P

202

13

P_{202}13

P20213)CPU中通用寄存器的位数取决于()

A. 存储器的容量 B. 指令的长度 C. 机器字长 D. 都不对

解答:通用寄存器用于存放操作数和各种地址信息等,其位数与机器字长相等,因此便于操作控制。选C

说明:1~3题,通过各个寄存器中存放的内容来推断该寄存器的位数 - (

2016

2016

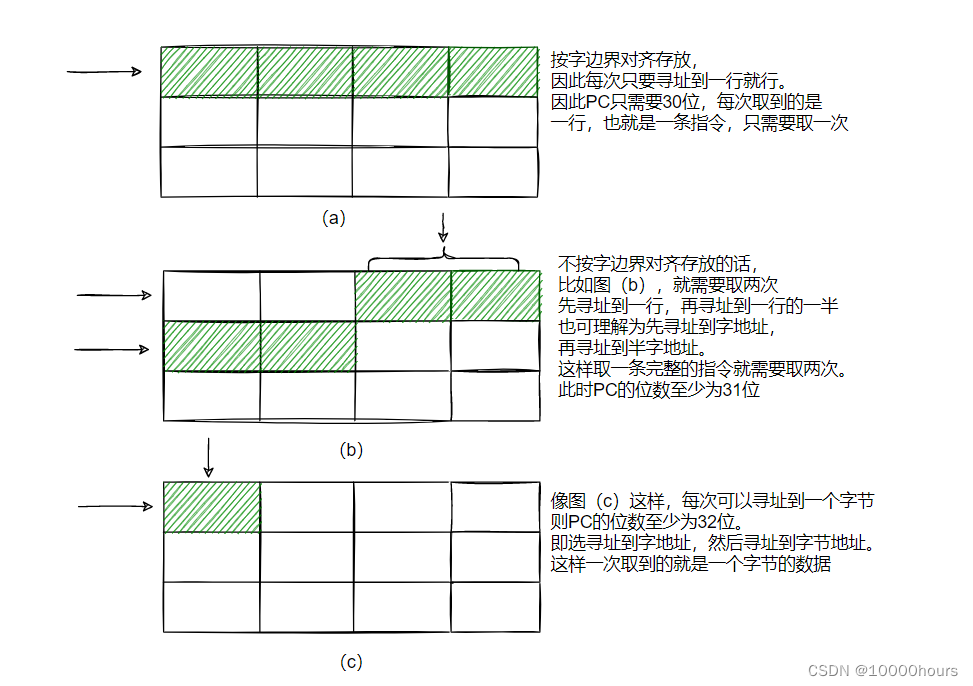

2016)某计算机的主存空间为4GB,字长为32位,按字节编址,采用32位字长指令字格式,若指令按字边界对齐存放,则程序计数器(PC)和指令寄存器(IR)的位数至少分别是()

A. 30、30 B. 30、32 C. 32、30 D. 32、32

解答:(1)首先IR中存放的是指令,其位数就是指令字长,即32位。(2)PC中存放的是指令的地址,因此要找到“定位存储器中每条指令所需的位数”。题中说“指令是按字边界对齐存放”,而该计算机的字长是32位,因此定位到一条指令至少需要 4 G B 32 b i t = 2 30 \cfrac{4GB}{32bit}=2^{30} 32bit4GB=230,即30位

更新文档

| 更新日期 | 更新内容 |

|---|---|

| 2022/7/20 | 增加了例题 |

620

620

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?