作业3

题量: 15 满分: 100

作答时间:03-09 09:43至03-15 23:59 100分

一. 单选题(共10题,50分)

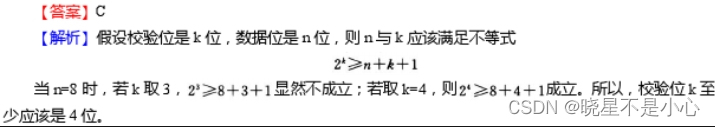

1. (单选题, 5分)用海明码对长度为8位的数据进行检纠错时, 若能纠正一位错,则检验位数至少为( )。

- A. 4

- B. 5

- C. 2

- D. 3

我的答案: A

2. (单选题, 5分)补码加/减法是指________。

- A. 操作数用补码表示, 连同符号位直接相加,减某数用加某数的机器负数代替,结果的符号在运算中形成;

- B. 操作数用补码表示, 两尾数相加/减, 符号位单独处理;

- C. 操作数用补码表示, 符号位和尾数一起参加运算, 结果的符号与加/减数相同;

- D. 操作数用补码表示, 由数符决定两尾数的操作, 符号位单独处理。

我的答案: A

3. (单选题, 5分)8位补码10010011等值扩展为16位后,其机器数为________。

- A. 0000000010010011

- B. 1111111101101101

- C. 1000000010010011

- D. 11111111 10010011

我的答案: D

带符号数的补码扩展原则,是用符号位填充扩展的高位

4. (单选题, 5分)在定点二进制运算器中,减法运算一般通过________来实现。

- A. 原码运算的二进制减法器

- B. 补码运算的二进制加法器

- C. 补码运算的二进制减法器

- D. 补码运算的十进制加法器

我的答案: B

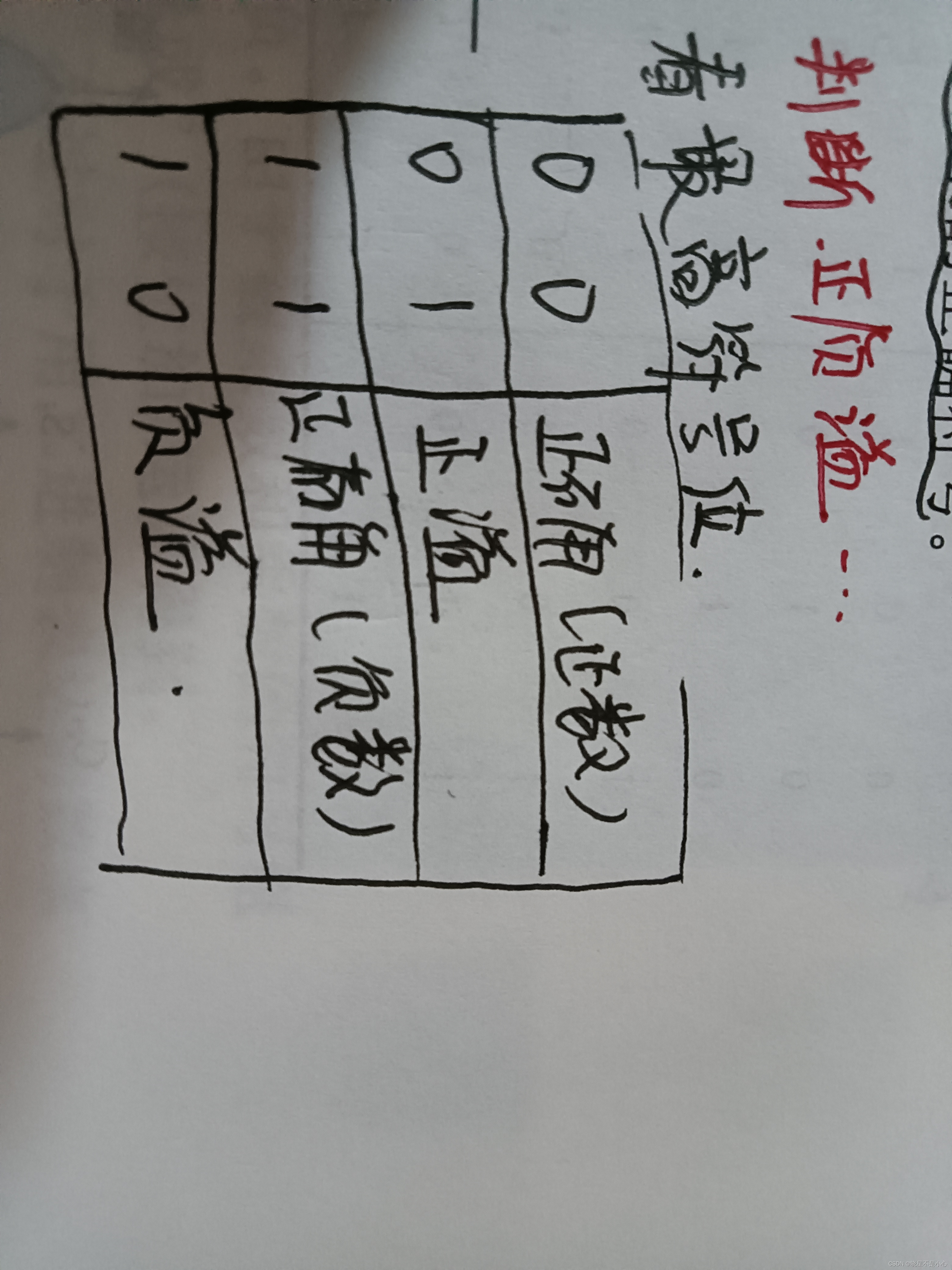

5. (单选题, 5分)在双符号位判别溢出的方案中,出现正溢出时,双符号位应当为________。

- A. 11

- B. 01

- C. 10

- D. 00

我的答案: B

6. (单选题, 5分)当定点运算发生溢出时,应进行________。

- A. 向右规格化

- B. 舍入处理

- C. 发出出错信息

- D. 向左规格化

我的答案: C

7. (单选题, 5分)在串行进位的并行加法器中,影响加法器运算速度的关键因素是________。

- A. 各位加法器速度的不同

- B. 元器件速度

- C. 进位传递延迟

- D. 门电路的级延迟

我的答案: C

8. (单选题, 5分)原码加减交替除法又称为不恢复余数法,因此________。

- A. 不存在恢复余数的操作

- B. 当某一步运算不够减时,做恢复余数的操作

- C. 当某一步余数为负时,做恢复余数的操作

- D. 仅当最后一步余数为负时,做恢复余数的操作

我的答案: D

9. (单选题, 5分)下列叙述中, 错误的是________。

- A. 补码乘法器中, 被乘数和乘数的符号都不参加运算

- B. 并行加法器中高位的进位依赖于低位

- C. 在小数除法中, 为了避免溢出,要求被除数的绝对值小于除数的绝对值

- D. 运算器中通常都有一个状态标志寄存器,为计算机提供判断条件,以实现程序转移

我的答案: A

10. (单选题, 5分)一个C语言程序在一台32位机器上运行。程序中定义了3个变量x、y和z, 其中x和y为int型, y为short型。(32位机int为4个字节,short为两个字节)。

当x=127,y=-9时,执行赋值语句z=x+y后,x、y和z的值分别是________。

- A. x=0000007FH, y=FFF9H, z=FFFF0076H

- B. x=0000007FH, y=FFF7H, z=FFFF0076H

- C. x=0000007FH, y=FFF7H, z=00000076H

- D. x=0000007FH, y=FFF9H, z=00000076H

我的答案: C

由题,int为32位,short为16位;

又因为,C语言的整型数据在内存中为补码形式

所以,x,y 的机器数写为十六进制为0000007F H ,FFF7 H,

(x= 0000 0000 0000 0000 0000 0000 0111 1111;127除2取余,再补零所得,再取补码

y= 1111 1111 1111 0111 ;(1 0111是1 1001的补码))

执行z=x+y时,需将短字长数据转换为长字长数据,称为 “ 符号扩展 ”

因为y的符号为 1 ,所以在y前添加16个1,即可将y上升为int型,

即为十六进制:FFFFFFF7 H

最后执行加法。即 0000007F H+FFFFFFF7 H=00000076 H,

其中最高位的进位1 自然丢弃

二. 填空题(共5题,50分)

11. (填空题, 8分)

原码阵列乘法器的输入为原码,输出也为原码。

用原码阵列乘法器计算x×y,x=-15,y=-10。

运算过程如下:(设原码长度为5,符号位1位,数值位4位)

机器内部原码数据:[x]原=______,[y]原=______;

符号位单独运算: 1⊕1=______;

其他位直接运算:|x|=_____,|y|=______;

乘法阵列:|x| ×|y| =______(本步骤请在草稿纸上列出竖式);

算后加符号位输出:[x×y]原=______;

所以 x×y =______。(此处为十进制,为方便比对,请明确标出+、 -)

我的答案:

8分

(1) 11111

(2) 11010

(3) 0

(4) 1111

(5) 1010

(6) 10010110

(7) 010010110

(8) +150

12. (填空题, 8分)

原码阵列乘法器的输入为原码,输出也为原码。

用原码阵列乘法器计算x×y,设x、y为二进制数,x=11011,y=-11111。

运算过程如下:(设原码长度为6,符号位1位,数值位5位)

机器内部原码数据:[x]原=______,[y]原=______;

符号位单独运算: 0⊕1=______;

其他位直接运算:|x|=_____,|y|=______;

乘法阵列:|x| ×|y| =______(本步骤请在草稿纸上列出竖式);

算后加符号位输出:[x×y]原=______;

所以 x×y =______。

我的答案:

8分

(1) 011011

(2) 111111

(3) 1

(4) 11011

(5) 11111

(6) 1101000101

(7) 11101000101

(8) -1101000101

13. (填空题, 8分)

补码阵列乘法器的输入为补码,输出也为补码。

用补码阵列乘法器计算x×y,x=-13,y=9。

运算过程如下:(设补码长度为5,符号位1位,数值位4位)

机器内部补码数据:[x]补=______,[y]补=______;

符号位单独运算: 1⊕0=______;

其他位算前求补器输出为:|x|=_____,|y|=______;

乘法阵列:|x| ×|y| =______(为方便比对,数字写8位,本步骤请在草稿纸上列出竖式);

算后求补器加符号位输出为:[x×y]补=______;

所以 x×y =______。(本题开始给出的xy为十进制,此处为十进制,为方便比对请为数字加上+、-符号)

我的答案:

8分

(1) 10011

(2) 01001

(3) 1

(4) 1101

(5) 1001

(6) 01110101

(7) 110001011

(8) -117

14. (填空题, 8分)

补码阵列乘法器的输入为补码,输出也为补码。

用补码阵列乘法器计算x×y,设x、y为二进制数,x=-10011,y=11001。

运算过程如下:(设补码长度为6,符号位1位,数值位5位)

机器内部补码数据:[x]补=______,[y]补=______;

符号位单独运算: 1⊕0=______;

其他位算前求补器输出为:|x|=_____,|y|=______;

乘法阵列:|x| ×|y| =______(为方便比对,数值位长度写10位,本步骤请在草稿纸上列出竖式);

算后求补器加符号位输出为:[x×y]补=______;

所以 x×y =______(为方便比对,数值位长度写10位)。

我的答案:

8分

(1) 101101

(2) 011001

(3) 1

(4) 10011

(5) 11001

(6) 0111011011

(7) 11000100101

(8) -0111011011

15. (填空题, 18分)

用原码阵列除法器计算X÷Y,设X、Y为二进制数,X=110000 Y=-11111。

运算过程:

先将X、Y乘一个比例系数化成小数,转换时需使被除数比除数小,使商也为一个小数。

X=11000=0.11000×26= x×26,Y=-11111=-0.11111 ×25 = y×25

[x]原=011000,[y]原=111111。符号位单独运算: 0⊕1=1。

用加减交替法计算|x|÷|y|,[|x|]补=011000, [|y|]补=011111,[-|y|]补=100001。

0.11000 被除数 第1步做减法

+ 1.00001 减除数

----------------------------------------------------

1.110010 余数为负,商0,下步做加法

+ 0.011111 除数右移1位,加

----------------------------------------------------

0.0100010 余数为正,商1,下步做减法

+ _________

----------------------------------------------------

0.00000110 余数为正 商1,下步做减法

+ _________

----------------------------------------------------

1.111001110 余数为负 商0 下步做加法

+ __________ 除数右移1位,加

----------------------------------------------------

1.1111011010 余数为负 商0 下步做加法

+ 0.0000011111 除数右移1位,加

----------------------------------------------------

1.1111111001 余数为负 商0 ,下步停止,

+ 0.0000011111 余数依然为负,不移位加

----------------------------------------------------

0.0000011000

故|x|÷|y|=______,余数为______。故 [x÷y]原=______。即 x÷y=______。

最后商和余数需要乘比例因子,余数修正时随被除数。X÷Y=______,余数为______。

我的答案:

18分

(1) 1.1100001

(2) 1.11100001

(3) 0.000011111

(4) 011000

(5) 0.0000011000

(6) 111000

(7) -0.11000

(8) -1.1000

(9) 1.1000

584

584

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?