作业6

一. 单选题(共19题,57分)

1. (单选题, 3分)计算机的存储器系统是指______。

- A. RAM存储器

- B. ROM存储器

- C. 主存储器

- D. cache,主存储器和外存储器 3分

2. (单选题, 3分)和内存储器相比,外存储器的特点是______。

- A. 容量大,速度快,成本低

- B. 容量大,速度慢,成本低

- C. 容量小,速度快,成本高

- D. 容量小,速度快,成本低

3. (单选题, 3分)存储单元是指______。

- A. 存放一个二进制信息位的存储元

- B. 存放一个机器字的所有存储元集合

- C. 存放一个字节的所有存储元集合

- D. 存放两个字节的所有存储元集合

4. (单选题, 3分)某存储器芯片的存储容量为8K×8位,则它的地址线和数据线引脚相加的和为______。

- A. 12

- B. 13

- C. 21

- D. 22

5. (单选题, 3分)某机字长64位,存储器容量是32MB。若按半字编址,那么它的寻址范围是______。

- A. 64M

- B. 32M

- C. 16M

- D. 8M

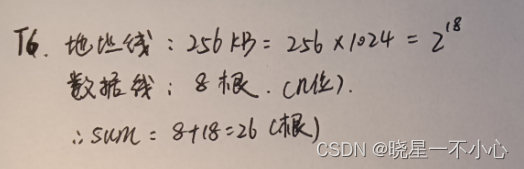

6. (单选题, 3分)一个256K×8的存储器,其地址线和数据线总和为______。

- A. 16

- B. 18

- C. 26

- D. 20

7. (单选题, 3分)某存储器芯片的存储容量为8K×12位,则它的地址线为____。

- A. 11

- B. 12

- C. 13

- D. 14

8. (单选题, 3分)某DRAM芯片,其存储容量为512K×8位,该芯片的地址线和数据线数目为______ 。

- A. 8,512

- B. 512,8

- C. 18,8

- D. 19,8

9. (单选题, 3分)没有外存储器的计算机初始引导程序可以放在______ 。

- A. RAM

- B. ROM

- C. RAM和ROM

- D. CPU

10. (单选题, 3分)EPROM是指______。

- A. 读写存储器

- B. 只读存储器

- C. 可编程的只读存储器

- D. 光擦除可编程的只读存储器

11. (单选题, 3分)某单片机的系统程序,不允许用户在执行时改变,则可以选用______作为存储芯片。

- A. SRAM

- B. 闪速存储器

- C. cache

- D. 辅助存储器

12. (单选题, 3分)“与非”门中的某一个输入值为“0”,那么它的输出值______。

- A. 为“0”

- B. 为“1”

- C. 要取决于其他输入端的值

13. (单选题, 3分)假定下列字符码中有奇偶校验位,但没有数据错误,采用奇校验的字符码有______。 (四个数为 ①10011010 ②11010000 ③11010111 ④10111100)

- A. ①③

- B. ①

- C. ②④

- D. ④

14. (单选题, 3分)双端口存储器之所以能高速进行读/写,是因为采用______。

- A. 新型器件

- B. 流水技术

- C. 两套相互独立的读写电路

- D. 高速芯片

15. (单选题, 3分)双端口存储器在______情况下会发生读/写冲突。

- A. 左端口与右端口的地址码不同

- B. 左端口与右端口的地址码相同

- C. 左端口与右端口的数据码不同

- D. 左端口与右端口的数据码相同

16. (单选题, 3分)模4交叉存储器有4个存储模块,它们有各自的______。

- A. 地址寄存器

- B. 地址寄存器和指令寄存器

- C. 地址寄存器和数据缓冲寄存器

- D. 地址寄存器、数据缓冲寄存器和指令寄存器

17. (单选题, 3分)某计算机使用4体交叉存储器,假定在存储器总线上出现的主存地址(十进制)序列为8005,8006,8007,8008,8001,8002,8003,8004,8000,则可能发生缓冲冲突的地址是

- A. 8004,8008

- B. 8002,8007

- C. 8001,8008

- D. 8000,8004

18. (单选题, 3分)交叉存储器实质上是一种______存贮器,它能_____执行______独立的读写操作。

- A. 模块式,并行,多个

- B. 模块式串行,多个

- C. 整体式,并行,一个

- D. 整体式,串行,多个

19. (单选题, 3分)多总线结构的计算机系统,采用______方法,对提高系统的吞吐率最有效。

- A. 多端口存储器

- B. 提高主存的速度

- C. 交叉编址多模块存储器

- D. 高速缓冲存储器

二. 填空题(共11题,43分)

20. (填空题, 3分)DRAM采用读出方式进行刷新。因为读出过程中恢复了存储单元的MOS栅极电容电荷,并保持原单元的内容,所以读出过程就是再生过程。常用的刷新方式由三种:____式、____式、____式。

我的答案:

3分

(1) 集中

(2) 分散

(3) 异步

21. (填空题, 3分)____能提供高性能、低功耗、高可靠性以及瞬间启动能力,因此作为固态盘用于便携式电脑中。

我的答案:

(1) 闪速存储器

22. (填空题, 3分)存储器的性能指标主要是____、____、存取(存储)周期和存储器带宽。

我的答案:

3分

(1) 存储容量

(2) 存取时间

23. (填空题, 3分)由于存储器芯片的容量有限,所以往往需要在____和____两方面进行扩充才能满足实际需求。

我的答案:

3分

(1) 位

(2) 字

24. (填空题, 3分)CPU能直接访问____和____,但不能直接访问磁盘和光盘。

我的答案:

3分

(1) Cache

(2) 主存

25. (填空题, 3分)动态存储器的刷新是按____(行/列)进行;若存储单体的容量为64K,采用双译码且地址线平均送到两个译码器中, 则刷新地址计数器位数为____。

我的答案:

3分

(1) 行

(2) 8

26. (填空题, 5分)片选信号为101时,选定一个128K*8位的存储芯片,则该芯片的所在存储单元空间的首地址为____H,末地址为____H。 (为方便比对,书写为5位)

我的答案:

5分

(1) A0000

(2) BFFFF

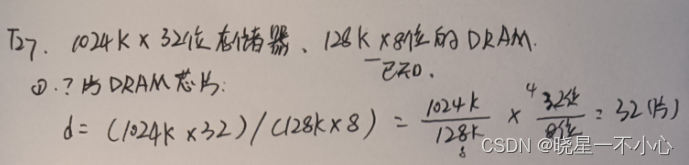

27. (填空题, 5分)有一个1024K×32位的存储器,由128K×8位的DRAM构成,共需要____片DRAM芯片,组织方式,____片一组(位扩展),共____组(字扩展)。

我的答案:

5分

(1) 32

(2) 4

(3) 8

28. (填空题, 5分)64K×8位的DRAM,存储矩阵行列数相同,则行数为____,行地址线需要____条,采用异步刷新,如果单元刷新间隔不超过8ms, 刷新信号周期为____μs(即隔多久刷新一行)。

我的答案:

5分

(1) 256

(2) 8

(3) 31.25

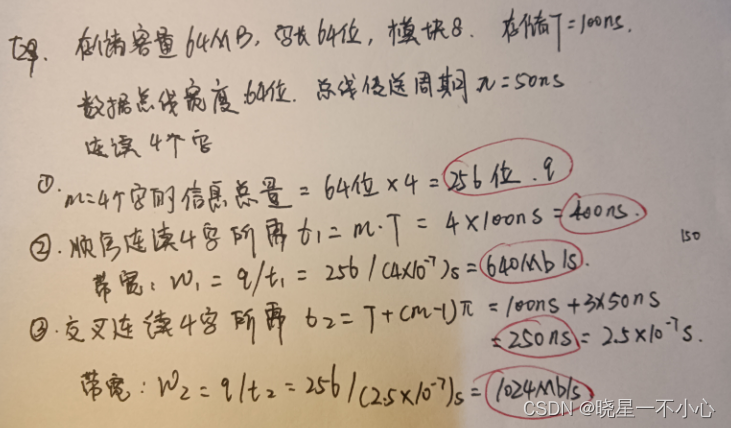

29. (填空题, 5分)定量分析对比顺序和交叉存储方式。

设存储器容量为64MB,字长为64位,模块数m=8, 存储周期T=100ns,数据总线宽度为64位,总线传送周期τ= 50ns。若连续读出4个字。

顺序存储器和交叉存储器连续读出m=4个字的信息总量都是____bit。

顺序存储器连续读出4个字所需的时间是____ns,带宽为____bps。

交叉存储器连续读出4个字所需的时间是____ns,带宽为____bps。

我的答案:

5分

(1) 256

(2) 400

(3) 640M

(4) 250

(5) 1024M

30. (填空题, 5分)若存储器字长64位,模块数m = 8,用交叉方式进行组织,

存储周期T = 200ns, 数据总线宽度为64位,总线传输周期τ = 50ns。

则连续读出 m=8 个字的信息量是____位,

连续读出 8 个字所需的时间是:____ns,

交叉存储器的带宽是:____bps(为方便比对,nM,n四舍五入为整数)

我的答案:

5分

(1) 512

(2) 550

(3) 931M

2031

2031

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?