嵌入式系统-原理与应用技术(第二版)期末复习-第二章

ARM9体系结构

1.ARM命名

ARM系列微处理器扩展命名符号的含义

2. ARM9处理能力的提高

ARM9处理能力的提高是通过增加时钟频率和减少指令执行周期实现的。

1.时钟频率的提高

ARM9采用了五级流水线,而ARM7采用的是三级流水线,ARM9增加的流水线设计提高了时钟频率和并行处理能力。五级流水线能够将各条指令处理分配到5个时钟周期内,在每个时钟周期内同时有5条指令在执行。在同样的加工工艺下,ARM9 TDMI处理器的时钟频率是ARM7 TDMI的2倍左右。

2.指令周期的改进

指令周期的改进有助于处理器性能的提高。性能提高的幅度依赖于代码执行时指令的重叠。

① load指令和store指令

指令周期数改进最明显的是load指令和store指令。

② 互锁(interlock)技术

当指令需要的数据因为以前的指令没有执行完,将产生管道互锁。管道发生互锁时,硬件将停止该指令的执行,直到数据准备就绪为止。

③ 分支指令

ARM9和ARM7的分支指令周期相同。

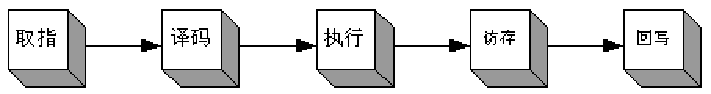

3.五级流水线

ARM9中1条指令的执行可以分为如下几个阶段:

(1)取指:从存储器中取出指令(fetch),并将其放入指令流水线。

(2)译码:对指令进行译码(dec)。

(3)执行:执行运算ALU(exe)

(4)访存(缓冲/数据):如果需要,则访问数据存储器(acc mem);否则ALU的结果只是简单地缓冲1个时钟周期,以便所有的指令具有同样的流水线流程。

(5)回写:将指令产生的结果回写到寄存器(wtbk res),包括任何从存储器中读取的数据。

4.总线接口

ARM嵌入式微处理器使用的是AMBA(Advanced Microcontroller Bus Architecture)总线体系结构。AMBA是ARM公司颁布的总线标准,通过AMBA可以方便地扩充各种处理器及I/O,可以把DSP、其他处理器和I/O(如UART、定时器和接口等)都集成在一块芯片中。该标准定义了如下三种总线:

●AHB(Advanced High-performance Bus):用于连接高性能系统模块。它支持突发数据传输方式及单个数据传输方式;另外,它还支持分离式总线事务处理。

● ASB总线(Advanced System Bus):用于连接高性能系统模块,它支持突发数据传输模式。

● APB总线(Advanced Peripheral Bus):是一个简单接口,支持低性能的外围接口。

5.结构特点

以ARM9系列的ARM9 TDMI和ARM9 E-S为例说明ARM9的结构。

ARM9 TDMI处理器内核的符号含义:

●ARM9:采用哈佛结构,ARMv4T指令集,五级流水线处理以及分离的Cache;

● T:支持16位宽度的Thumb压缩指令集;

● D:支持片上Debug,允许处理器响应调试请求暂停;

● M:支持增强型乘法器,可生成全64位的结果;

● I:嵌入式ICE部件,提供片上断点和调试点的支持。

常用的一种ARM920T处理器核是在ARM9TDMI处理器内核基础上,

- 增加了分离式的指令Cache和数据Cache,

- 并带有相应的存储器管理单元I-MMU和D-MMU、写缓冲器及AMBA接口等。

- 指令缓存和数据缓存允许处理器同时进行取指和读写数据操作。

- 数据可以是8位(字节)、16位(半字)、32位(字),字必须以4字节边界对准,半字必须以2字节边界对准。

ARM9 E-S其主要特点如下:

●32位定点RISC处理器,改进型ARM/Thumb代码,增强型乘法器设计,支持实时调试;

●片内指令和数据SRAM,而且指令和数据的存储器容量可调;

●片内指令和数据高速缓冲器(cache)容量从4K字节到1M字节;

●设置保护单元(protection unit),非常适合嵌入式应用中对存储器进行分段和保护;

●采用AMBA AHB总线接口,为外设提供统一的地址和数据总线;

●支持外部协处理器,指令和数据总线有简单的握手信令支持;

●支持标准基本逻辑单元扫描测试方法,并且支持内建自测试技术(BIST: Built-In-Self-Test);

●支持嵌入式跟踪宏单元(ETM,Embedded Trace Macrocell),支持实时跟踪指令和数据。

6.指令集特点

ARM9的指令集是依据RISC原理而设计的,指令集和相关译码机制较为简单。传统的微处理器体系结构中,指令代码的宽度(位数)和数据的宽度(位数)通常是相同的,而ARM9的指令系统中有一种16位的指令集(Thumb指令集)。通常情况下,16位体系结构与32位体系结构比较而言,在操作32位数据时的性能大约只有32位体系结构的一半,且有效的寻址空间相对较小。而Thumb指令集在32位体系结构中实现了16位指令集,以提供比32位体系结构更高的性能和更高的代码密度。

7.Thumb指令集概况

ARM指令集为32位指令集,可以实现ARM架构下所有功能。Thumb指令集是对32位ARM指令集的扩充,它的目标是为了实现更高的代码密度。Thumb指令集实现的功能只是32位ARM指令集的子集,它仅仅把常用的ARM指令压缩成16位的指令编码方式。在指令的执行阶段,16位的指令被重新解码,完成对等的32位指令所实现的功能。

Thumb指令的操作是在标准的ARM寄存器下进行的,在ARM指令代码和Thumb指令代码之间可以方便地进行切换,并具有很好的互操作性。在执行时,16位的Thumb指令透明地实时解压缩成32位的ARM指令,并没有明显的性能损失。因此,使用Thumb指令以16位的代码密度可以得到32位处理器性能,从而节省了存储空间和硬件成本。

Thumb指令集的16位指令代码长度大约是标准ARM指令代码密度的两倍,因而可以在16位存储系统上运行。

8.ARM指令集与Thumb指令集比较

与ARM指令集相比较,在Thumb指令集中,数据处理指令的操作数仍然是32位的,指令地址也为32位,但Thumb指令集为实现16位的指令长度,舍弃了ARM指令集的一些特性,如大多数Thumb指令是无条件执行的,而几乎所有的ARM指令都是有条件执行的。大多数的Thumb数据处理指令的目的寄存器与其中一个源寄存器相同

与全部采用ARM指令集的方式相比,使用Thumb指令可以在代码密度方面改善大约30%,但这种改进是以代码的效率为代价的。尽管每个Thumb指令都有相对应的ARM指令,但是,执行相同的功能,需要更多的Thumb指令才能完成。因此,当指令预取需要的时间没有区别时,ARM指令相对Thumb指令具有更好的性能。开发者在进行系统设计的时候需要综合考虑成本、性能和功耗等因素。如果在一个系统中综合使用ARM指令和Thumb指令,充分发挥各自的优点,就能在成本、性能和功耗等因素上取得较好的平衡。

9. ARM9工作模式

ARM9 TDMI处理器核共支持7种工作模式,它们分别是:

●用户模式(usr):ARM处理器正常执行程序时的处理。

●快速中断模式(fiq):用于高速数据传输或通道处理。

●外部中断模式(irq):用于通用的中断处理。

●管理模式(svc):操作系统使用的保护模式。

●指令/数据访问终止模式(abt):当数据或指令预取终止时进入该模式,可用于虚拟存储及存储保护。

●系统模式(sys):运行具有特权的操作系统任务时的模式。

●未定义指令中止模式(und):当未定义的指令执行时进入该模式,可用于支持硬件协处理器的软件仿真。

ARM9 TDMI处理器核的运行(工作)模式可以通过软件的控制改变,也可以通过外部中断或异常处理改变。大多数的应用程序运行在用户模式下,当处理器运行在用户模式下时,某些被保护的系统资源是不能被访问的。 除用户模式以外,其余的所有6种模式称之为非用户模式,或特权模式;其中除去用户模式和系统模式以外的5种又称为异常模式,常用于处理中断或异常,以及需要访问受保护的系统资源等情况。

当某种异常发生时,ARM9 TDMI处理器核即进入相应的工作模式。例如,若发生了IRQ中断并响应IRQ中断,则ARM9 TDMI核将进入IRQ模式。每种工作模式下均有其附加的某些寄存器,因此,即使有异常情况发生,异常模式下的处理程序也不至于破坏用户模式的数据及状态。

从ARM9 处理器核所执行的程序代码的角度来看,有两种工作状态:ARM状态和Thumb状态。在ARM状态下,处理器核执行32位的、字对齐的ARM指令;在Thumb状态下,处理器核执行16位的、半字对齐的Thumb指令。在程序的执行过程中,ARM9处理器核可以随时在两种工作状态之间切换,并且处理器工作状态的改变不影响处理器的工作模式和相应寄存器中的内容。

ARM指令集和Thumb指令集中均有切换ARM处理器工作状态的指令,使ARM处理器可在两种工作状态之间切换。但是,ARM处理器核在上电或复位并开始执行程序代码时,应该处于ARM状态。

当操作数寄存器的状态位(位0)为1时,可以采用执行BX指令的方法,使ARM处理器从ARM状态切换到Thumb状态;当操作数寄存器的状态位(位0)为0时,执行BX指令可以使ARM处理器从Thumb状态切换到ARM状态。另外,在处理器进行异常处理时,将PC指针放入异常模式链接寄存器中,并从异常向量地址开始执行程序,也可以使处理器切换到ARM状态。

3078

3078

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?