4.1 为什么选择CMOS反相器?

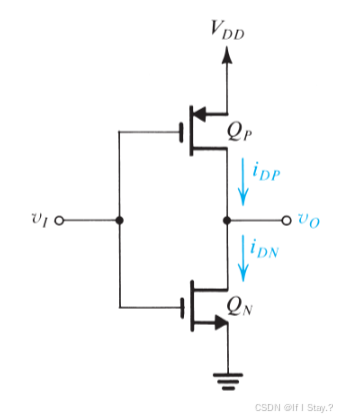

CMOS反相器是数字电路中最基础的单元电路,由PMOS和NMOS管组成,具有功耗低、噪声容限高等特点。测试其输出特性(VOH/VOL、驱动能力)是理解半导体测试原理的最佳入门案例。

目标:验证CMOS反相器在输出高电平(VOH)时的电压与电流是否符合规格(如VOH ≥ 4.5V @ IOH = -4mA)。

4.2 测试电路与设备配置

电路结构

-

输入信号:方波(0V→5V)

-

输出端口:连接PMU测试通道

-

电源:VDD=5V,VSS=0V

测试设备

| 设备模块 | 功能说明 | 关键参数 |

|---|---|---|

| PMU | 驱动电流并测量电压 | 精度±1mV, 电流范围±20mA |

| DPS | 提供芯片电源 | 电压稳定性≤0.1% |

| Pattern发生器 | 生成输入方波信号 | 频率1kHz, 占空比50% |

4.3 测试步骤详解(附原理分析)

步骤1:设置测试条件

-

电源配置:通过DPS为CMOS反相器提供VDD=5V,确保静态工作点稳定。

-

输入信号:Pattern发生器输出1kHz方波,模拟实际工作场景。

模电知识应用:

-

CMOS结构:PMOS导通时输出高电平,NMOS导通时输出低电平。

-

噪声容限:CMOS的高电平接近VDD,低电平接近VSS,抗干扰能力强。

步骤2:PMU驱动与测量

-

驱动模式:PMU设置为电流驱动模式,输出IOH=-4mA(拉电流)。

-

电压测量:在输出高电平时,测量VOH值。

测试原理:

-

欧姆定律:VOH = VDD - IOH × R_on(R_on为PMOS导通电阻)。

-

规格判定:若VOH ≥ 4.5V,则测试通过;否则判定为缺陷。

数电知识应用:

-

逻辑电平标准:CMOS高电平需满足VOH ≥ 0.7×VDD(即3.5V @ 5V电源)。

-

驱动能力:输出电流IOH反映PMOS管的导通能力,决定带负载能力。

步骤3:数据记录与分析

关键问题排查:

-

电压跌落:若VOH低于4.5V,可能是PMOS导通电阻过大或电源噪声导致。

-

电流泄漏:静态电流超标可能因NMOS未完全关断(需检查阈值电压)。

4.4 测试中涉及的模电与数电知识点总结

| 知识领域 | 具体内容 | 应用场景 |

|---|---|---|

| 模拟电路 | - CMOS管导通特性 - 输出阻抗计算 - 电源稳定性分析 | PMU驱动与电压测量 |

| 数字电路 | - 逻辑电平定义 - 驱动能力指标(IOH/IOL) - 噪声容限与抗干扰设计 | 测试规格判定 |

| 测试方法 | - 开尔文四线法(消除线阻影响) - 钳制电流保护电路 | PMU精确测量 |

4.5 实际工程中的常见问题与解决策略

-

输入悬空导致CMOS损坏

-

现象:输入引脚未接上拉/下拉电阻,导致栅极电压漂移。

-

解决:遵循“所有输入引脚必须确定电平”原则。

-

-

测试夹具引入噪声

-

现象:VOH测量值波动大。

-

解决:使用屏蔽双绞线连接PMU,并增加RC滤波电路。

-

-

温度对阈值电压的影响

-

现象:高温下NMOS阈值电压降低,导致漏电流增加。

-

解决:多温度点测试(-40℃/25℃/85℃)。

-

4.6 拓展实验:用TTL逻辑驱动CMOS电路

问题:TTL输出高电平(典型3.5V)无法直接驱动5V CMOS电路。

解决方案:

-

电平转换电路:使用上拉电阻(10kΩ)将TTL输出高电平拉至5V。

-

专用芯片:采用74HCT系列(兼容TTL输入电平的CMOS器件)。

模电分析:

-

上拉电阻值需满足:R ≤ (VDD - VOH_TTL) / IOH_TTL(避免电压分压过大)。

本章总结

通过CMOS反相器测试案例,初学者可掌握:

-

测试设备联动:PMU、DPS、Pattern发生器的协同工作逻辑。

-

故障诊断思维:从电压异常反推工艺缺陷(如氧化层厚度偏差)。

-

跨学科知识融合:模电(晶体管特性)与数电(逻辑电平)的交叉验证。

动手实验建议:

-

在Multisim中搭建CMOS反相器电路,模拟PMU测试流程。

-

尝试修改PMOS/NMOS的宽长比(W/L),观察VOH与驱动能力的变化。

讨论话题:

如果你设计的CMOS反相器VOH始终低于4V,可能有哪些原因?如何通过测试数据定位问题?欢迎在评论区分享你的推理过程! 💡

参考资料:本章内容综合自《The Fundamentals Of Digital Semiconductor Testing》第3-4章、行业测试手册及模拟电路设计原理

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?