一 关于arm

1 arm的三种含义

(1) 一个公司的名称 Advanced RISC Machine

(2) 一类处理器的统称

(3) 一种技术的名称 (RISC)

ARM是以一家设计处理器的公司,这家公司设计的处理器统称为ARM,它们使用的指令集是RISC(精简指令集)

2 两种指令集

2.1 CISC

复杂指令集(汇编指令)指令数量多、设计复杂、能耗高,比如intel的处理器(电脑)

2.2 RISC

精简指令集,指令数量少,设计相对简单,能耗较低,更多的应用在各种移动终端

3 arm公司

只负责设计芯片(设计处理器的架构+总线),而不生产芯片,将设计版权授权全球各大半导体厂商,让它们去生产

4 arm型号

比如有一块开发板的型号:fs4412,由fs公司设计制造和命名;

开发板的核心板板载了一个soc芯片:exynos4412,这个芯片由三星设计制作和命名;

soc上的cpu内核的型号是:A9(cortex-a9),这个型号的架构是armv7;由arm公司设计和命名;

4.1 什么是soc

system on chip片上系统;狭义的讲就是一个芯片上集成了处理器、存储器、各种接口模块等组成了一个完整的硬件系统。

4.2 cortex-a/m/r

从armv6架构之后,内核的型号命名变化为cortex

(1) cortex-a:高端应用,手机、平板等;

(2) cortex-m:低功耗,单片机;

(3) cortex-r:实时处理器:实时操作系统RTOS;

5 arm数据与指令类型

(1) ARMv7:

ARM采用32位架构;

· Byte:8bits

· Halfword :16bits

· Word:32bits

· Doubleword:64bits(cortex-a处理器)

大部分的arm core提供:

· arm指令集(32bits)

· thumb指令集(16bits)

(2) ARMv8是64位的

二 cortex-A9处理器

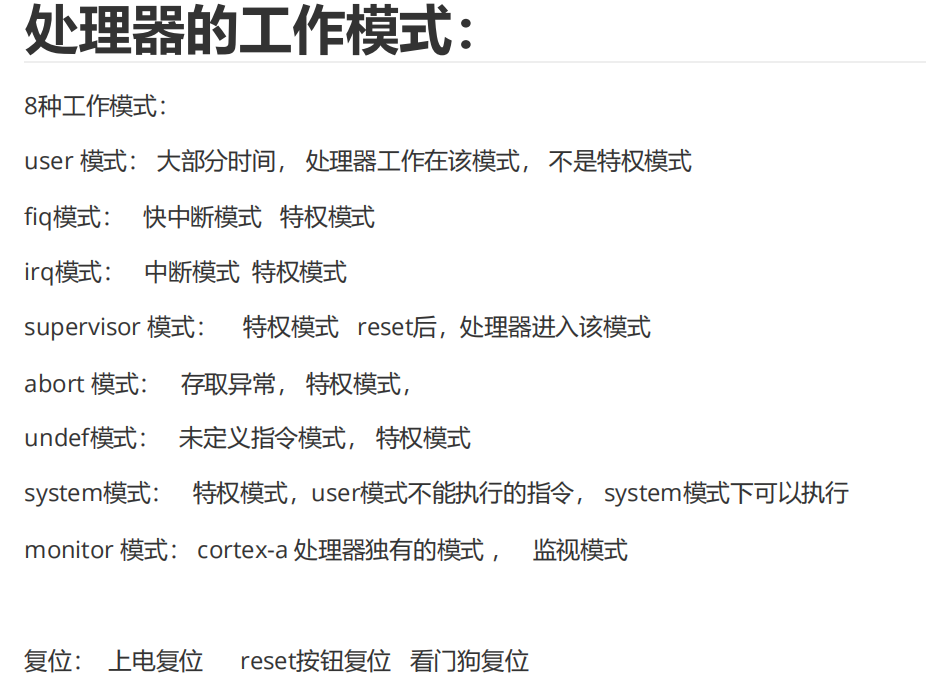

1 arm的工作模式

2 cortex-a的寄存器组织概要

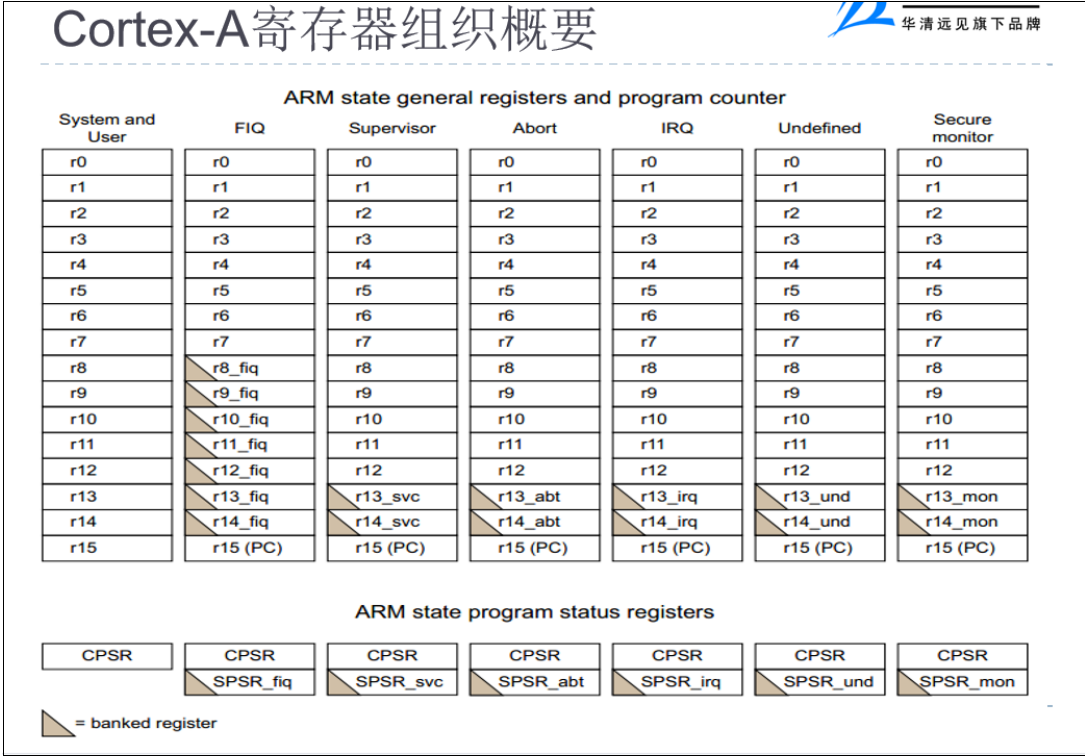

三角标记表示各工作模式下独有的寄存器,不能被其它工作模式访问,未被标记的表示所有工作模式共享,在内核中只有一份;比如r0寄存器在内核中只有一份,所有工作模式下访问到的是同一个寄存器,而对于User模式下能访问到的r8寄存器,在FIQ模式下不能访问,而是去访问r8_fiq是寄存器,同样地User模式下也不能访问r8_fiq寄存器;

观察知:

(1) 先不考虑monitor模式,内核中一共有37个寄存器;

(2) FIQ模式下的私有寄存器最多;

(3) 每个模式都有自己的r13和r14,即sp和lr;

(4) pc只有一个;

(5) 只有User模式没有spsr寄存器;因为大部分情况都在user模式运行,当产生中断或者异常时,为了能够及时响应然后处理异常,会自动从user模式切换到其他模式,但是处理完之后需要手动恢复;

一些补充:

(1) cpsr是当前程序状态寄存器,只有一个;

(2) spsr是保存cpsr的寄存器,当user模式切换到其他模式,需要先将user模式的状态保存在对应模式的spsr中,之后cpsr寄存器中保存其他模式的当前程序状态;异常模式的代码执行完之后需要回到User模式,先从spsr把之前User模式的cpsr恢复,这样就完好得切换回原来的模式和状态;

(3) pc是程序计数器,程序执行到哪里,pc就在哪里;

(4) r13即sp栈顶指针,每种模式都有它自己的栈区;

(5) r14即lr返回地址;

三 计算机系统基本组成

1 总述

硬件部分:输入输出设备、处理器(控制器、运算器、寄存器)、存储器(外存、内存、cache)、总线

2 通过公交车理解总线

公交车有什么特点:有起点站和终点站;中途有数个站点;每个站都可以上下人;可以从起点站坐到终点,也可以在某个站下车;或者从某个站点上车,然后在另一个站点或起点站下车;

总线有什么特点:连接CPU和各个IO,内存等;数据可以从CPU送到内存,各个IO,也可以在IO之间传输;

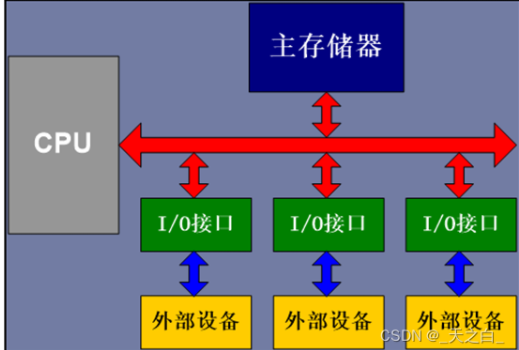

3 两种总线结构

3.1 单总线结构

缺点:

(1) 内存读写的速度一般比IO设备要快,限制了内存的读写速度

(2) 内存和IO设备要进行数据传输必须要经过cpu

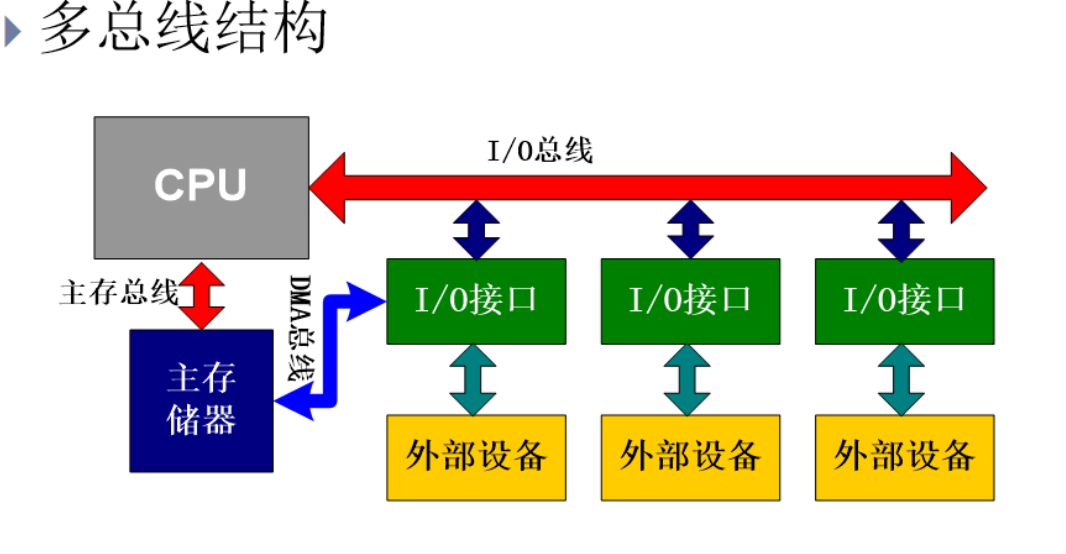

3.2 多总线结构

3.2.1 DMA

Direct memory access直接内存访问,解放了cpu,比如需要大量数据传输的时候就可以使用dma

3.2.2 AHB高速总线 APB(外设)总线

3.2.3 高速缓冲器cache

编译器会对程序其进行优化,使一些经常需要访问的数据在运行时从内存拷贝一份到cache中,之后如果cpu要访问这些数据,直接从cache中取,cache比内存的读写速度快,所以从一定程度上提高了程序运行效率。

但是,如果有一个变量的值需要经常发生改变,而且改变的一定是内存的值,而cpu还是去cache中取数据,若更改的频率大于cache刷新的频率,就会出现内存和cache中数据不同步的问题,所以这种情况不适合使用cache,通过volatile声明变量告诉编译器这个变量的值不优化,也就是每次都去访问内存,而不在cache中备份。

7074

7074

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?