1:门级描述和数据流描述

这两种描述的时候,使用默认的wire即可。

这两种描述方式,本质上都是直接使用逻辑门

门级描述是显式地使用了门级原语

数据流描述其实是隐式地使用门级原语,因为他是直接描述数据在寄存器直接的流动关系,本质上,还是在阐述逻辑门的使用

门级描述与数据流描述,就好比结绳记事和使用符号记事的区别,用一连串的符号标志,代替了绳子,减少了许多麻烦。

门级描述是以门级原语为基石的描述方式,必须使用线网类型

数据流描述是以连续赋值语句为基石的描述方式,其左值必须是线网类型,右值无要求。

以下是四选一数据选择器的端口声明,关注output out语句

module choose_4to1(

input d0,d1,d2,d3,

input add1,add0,

output out // 注意输出端口的设定

);

endmodule

你需要记住Verilog描述形式

需要记住,门级描述的输出和数据流描述的连续赋值语句的左值,必须是线网类型,所以必须使用默认的输出端口

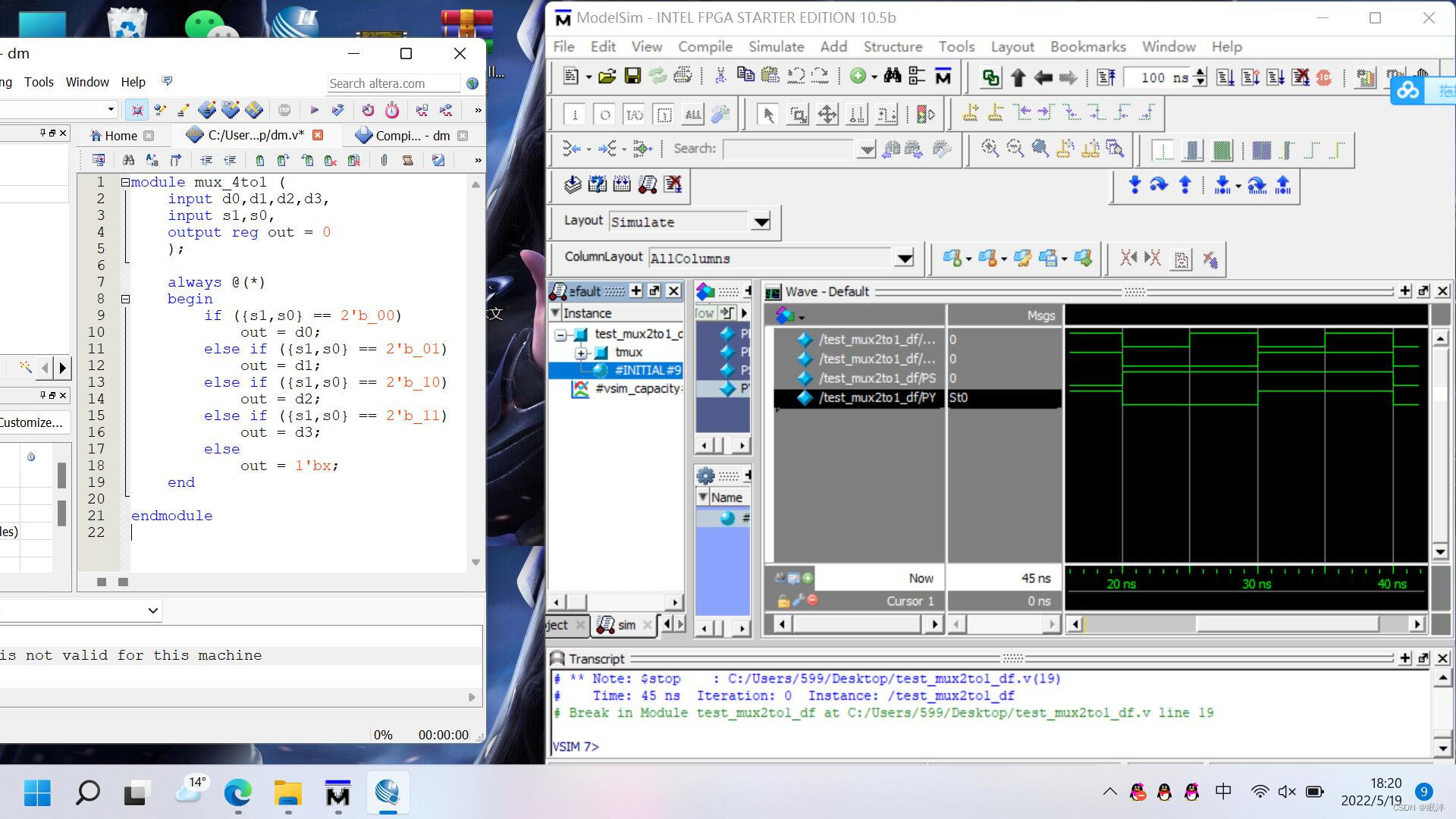

1.2 行为级描述

行为级描述,输出端口类型应该使用output reg OUT,使用reg类型。

因为过程赋值语句的左值必须是寄存器类型

ANSI C风格的描述如下

module choose_4to1(

input d0,d1,d2,d3,

input add1,add0,

output reg out // 注意输出端口的设定

);

endmodule

你也可以将输出端口初始化output reg out = 0

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?