目录

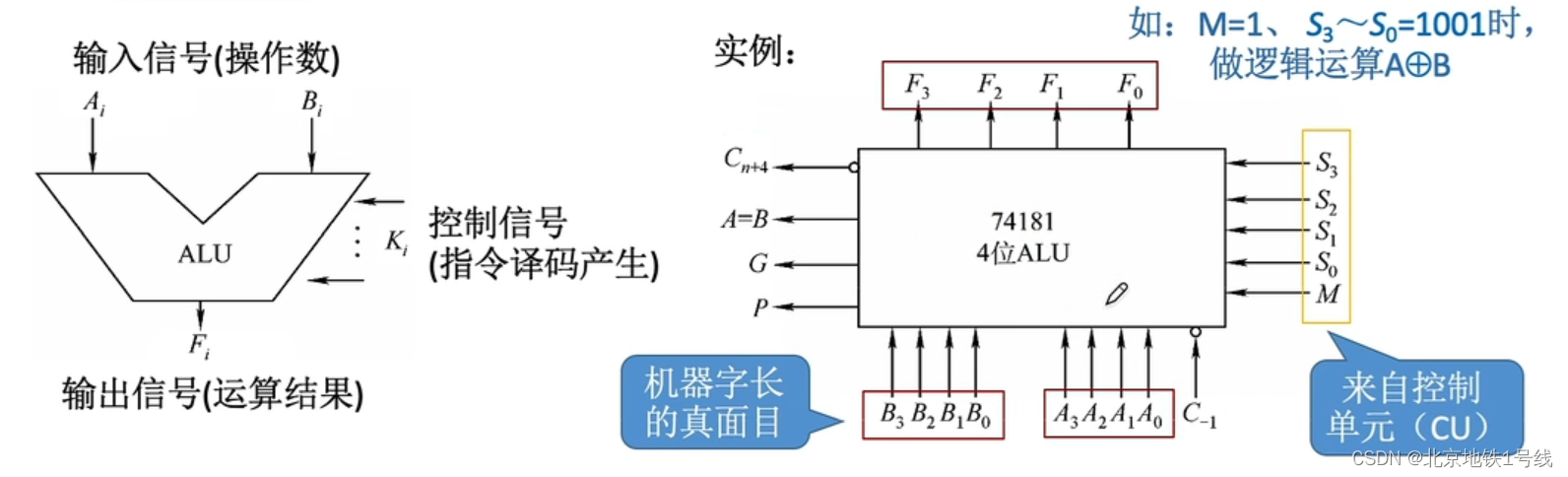

一. 算术逻辑单元,加法器

算术运算:加、减、乘、除等;逻辑运算:与、或、非、异或等;辅助功能:移位、求补等。

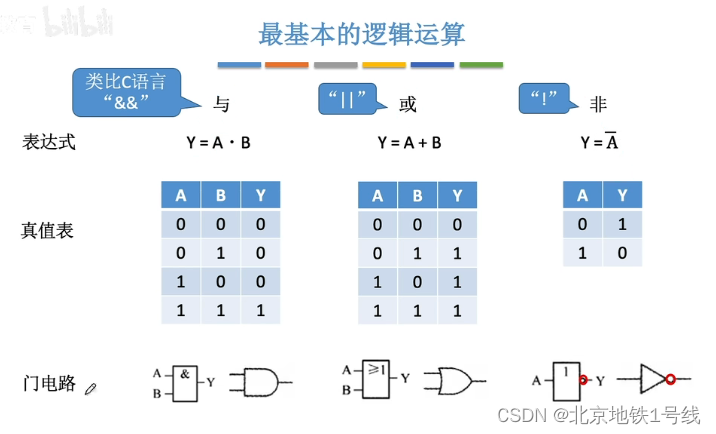

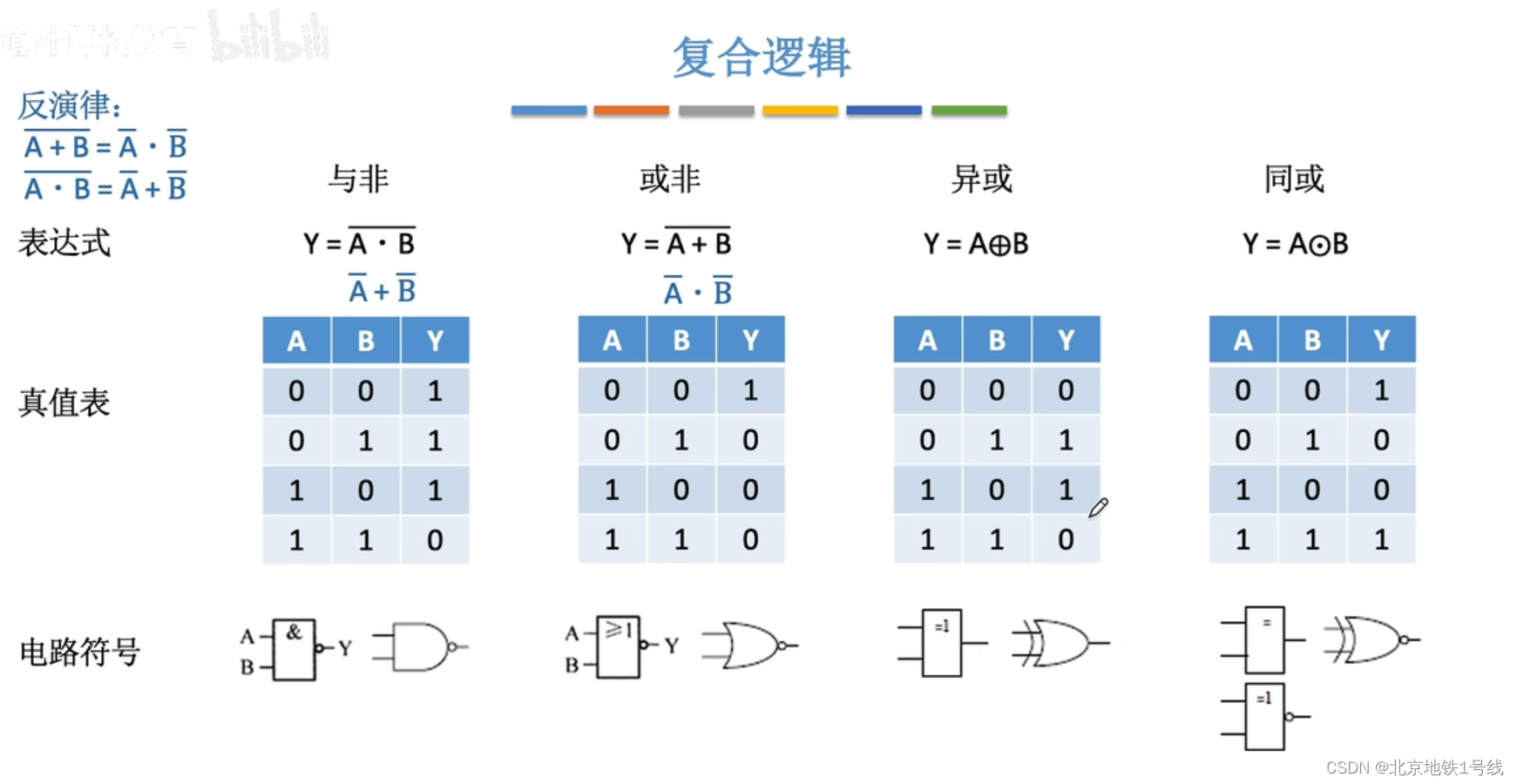

对于逻辑运算,我们可以用门电路实现,输入分别是高低电平:

以上逻辑电路符号必须熟记!优先级:与>或>非。

基于异或运算的天然逻辑:奇偶校验位(即:n个位异或运算,结果为1说明有奇数个1,结果为0说明有偶数个1)。

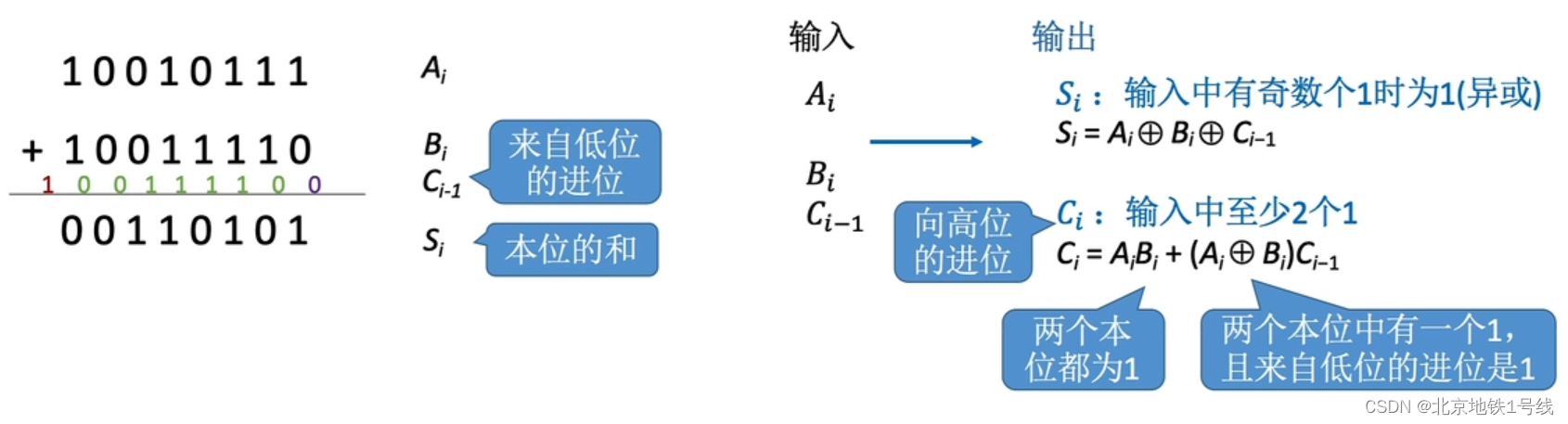

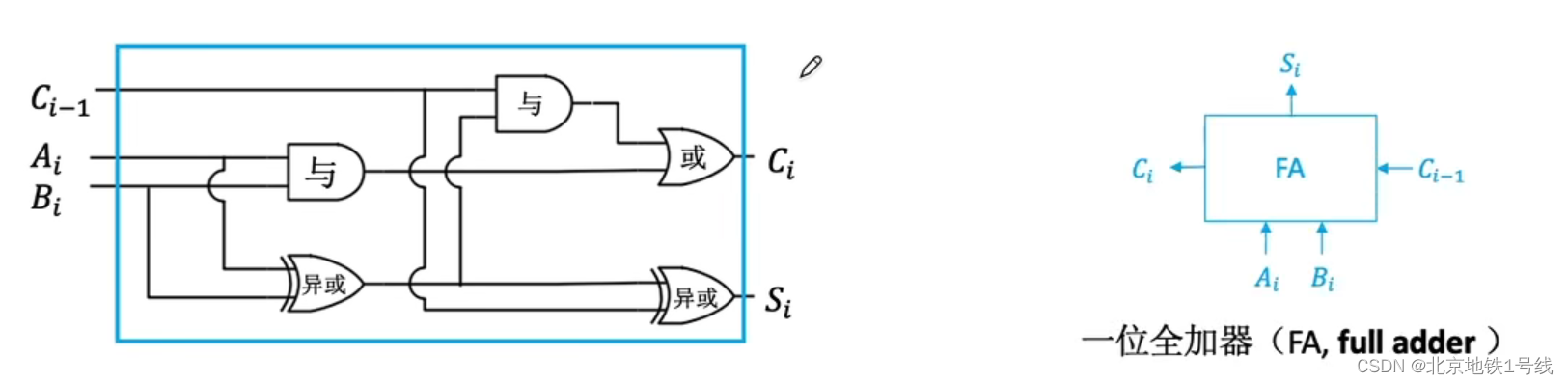

一位全加器(i从1开始,从左往右):

根据逻辑表达式可以画出电路图(右图是简化版本):

二. 串行加法器和并行加法器

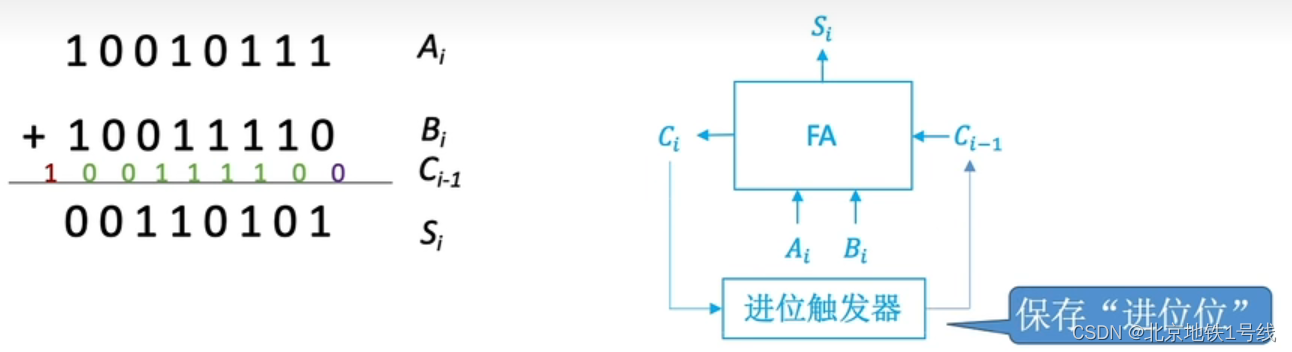

串行加法器:只有一个全加器,数据逐位串行送入加法器中进行运算。进位触发器用来寄存进位信号,以便参与下一次运算。如果操作数长n位,加法就要分n次进行,每次产生一位和,并且串行逐位地送回寄存器。

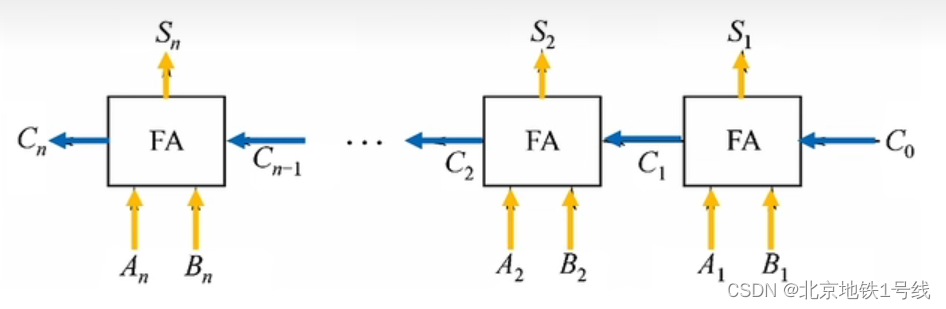

串行进位的并行加法器:把n个全加器串接起来,就可进行两个n位数的相加。

串行进位又称为行波进位,每一级进位直接依赖于前一级的进位,即进位信号是逐级形成的。

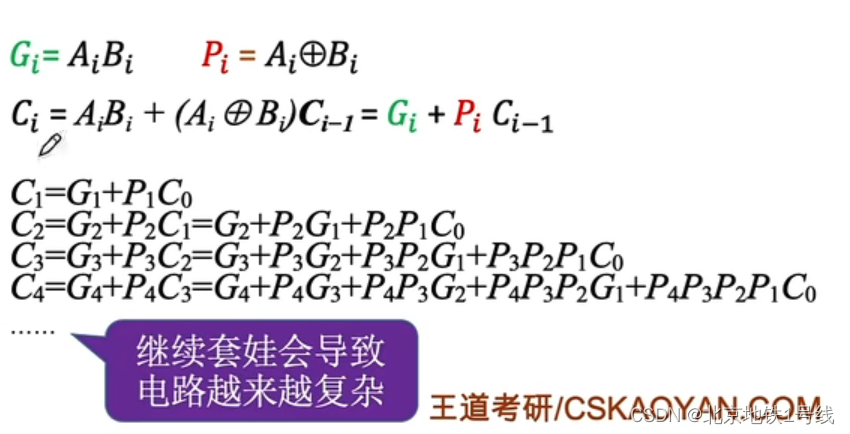

并行进位的并行加法器:各级进位信号同时形成,又称为先行进位、同时进位。

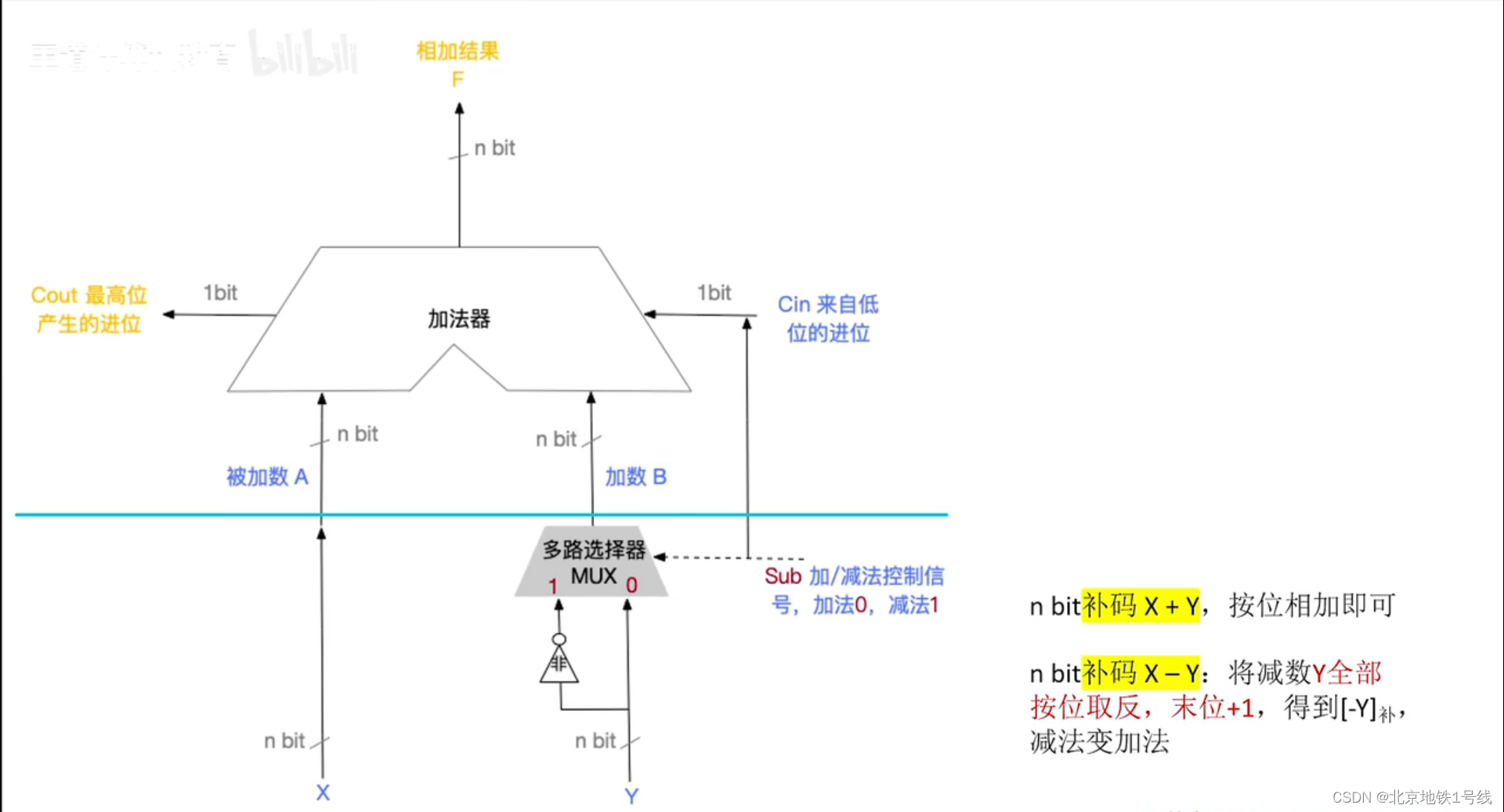

三. 补码加减运算器

在加法器的基础上增加一个多路选择器MUX:

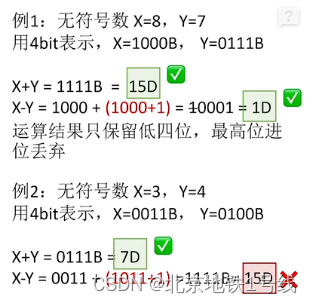

无符号整数的加法/减法也可用该电路实现。

n bit无符号数X+Y,按位相加即可

n bit无符号数X-Y:将减数Y全部按位取反,末位+1,减法变加法。

四. 原码,补码的加减运算

(1)原码的加减法运算

- 正+正→绝对值做加法,结果为正,可能会溢出

- 负+负→绝对值做加法,结果为负,可能会溢出

- 正+负→绝对值大的减绝对值小的,符号同绝对值大的数

- 负+正→绝对值大的减绝对值小的,符号同绝对值大的数

原码的减法运算,“减数”符号取反,转变为加法:

- 正-负→正+正

- 负-正→负+负

- 正-正→正+负

- 负+正→负-负

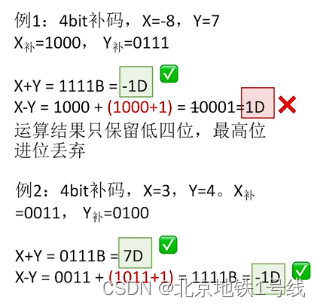

(2)补码的加减法运算

对于补码来说,无论加法还是减法,最后都会转变成加法,由加法器实现运算,符号位也参与运算。

五. 溢出判断

基本判断逻辑:只有“正数+正数”才会上溢――正+正=负;只有“负数+负数”才会下溢――负+负=正。

(1)采用一位符号位

设A的符号为As,B的符号为Bs,运算结果的符号为Ss;则溢出逻辑表达式为

若v=0,表示无溢出;若v=1,表示有溢出。第一项代表正+正=负,第二项代表负+负=正。

(2)采用一位符号位

根据数据位进位情况判断溢出。

| 符号位的进位 | 最高数值位的进位 | |

| 上溢 | 0 | 1 |

| 下溢 | 1 | 0 |

判断时采用异或运算即可:

(3)采用两位符号位

正数的符号位:00,负数的符号位:11.

如果运算完两位符号位不相同则可以知道发生了溢出错误。

双符号位补码又称模4补码;单符号位补码又称模2补码。实际存储时只存储1个符号位,运算时会复制一个符号位。

六. 符号扩展

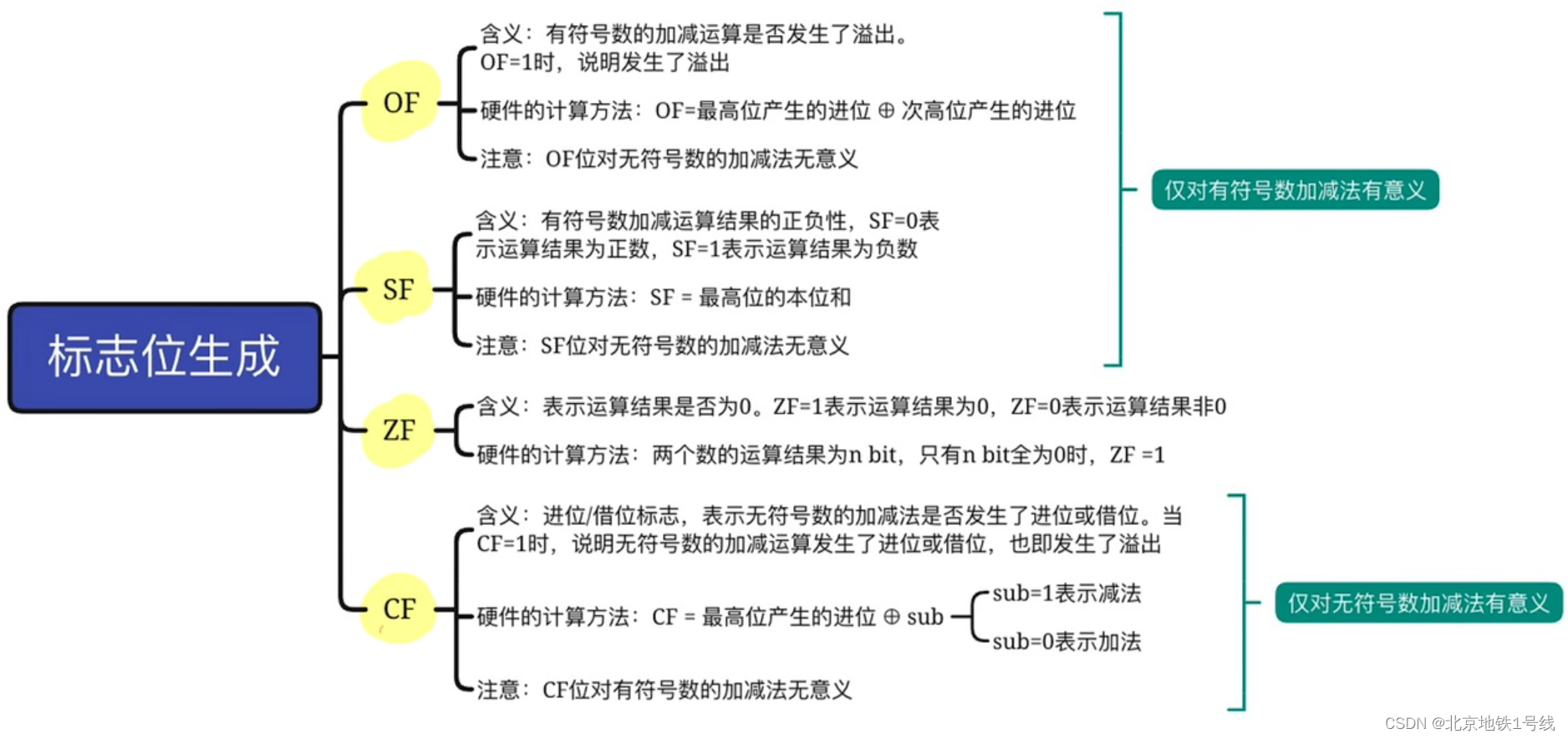

七. 标志位的生成

- OF (Overflow Flag)溢出标志。溢出时为1,否则置0。

- SF (Sign Flag)符号标志。结果为负时置1,否则置0.

- ZF (Zero Flag)零标志,运算结果为0时ZF位置1,否则置0.

- CF (Carry Flag)进位/借位标志,进位/借位时置1,否则置0.

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?