2.数据的表示和运算

2.3运算部件

门电路

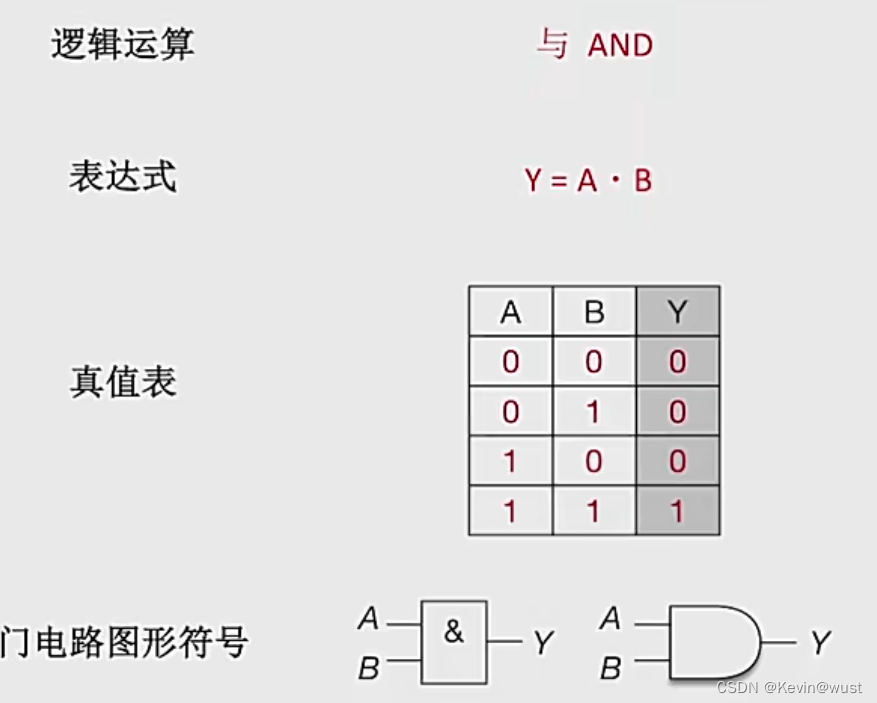

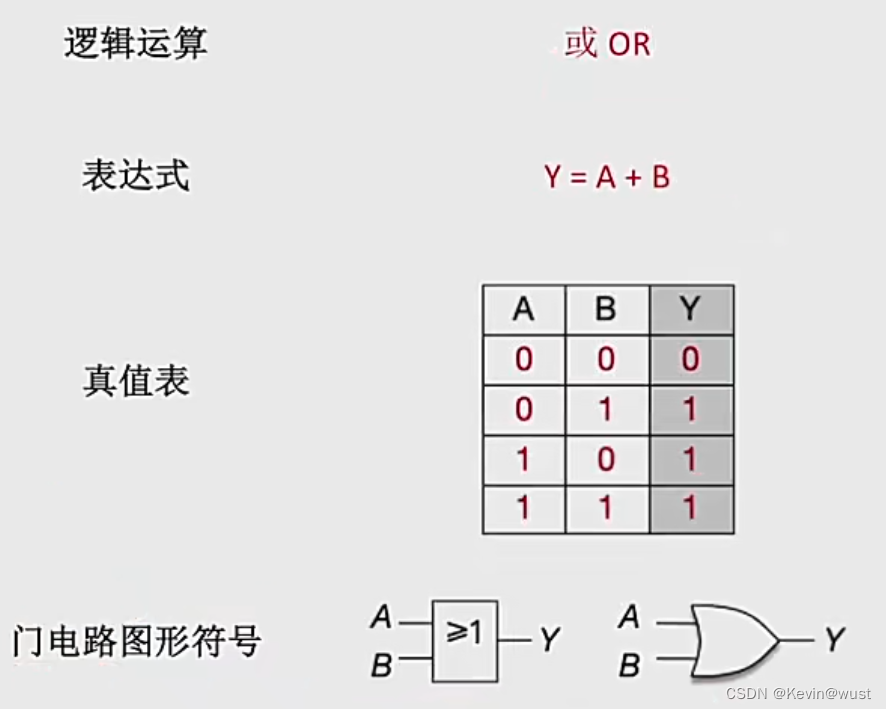

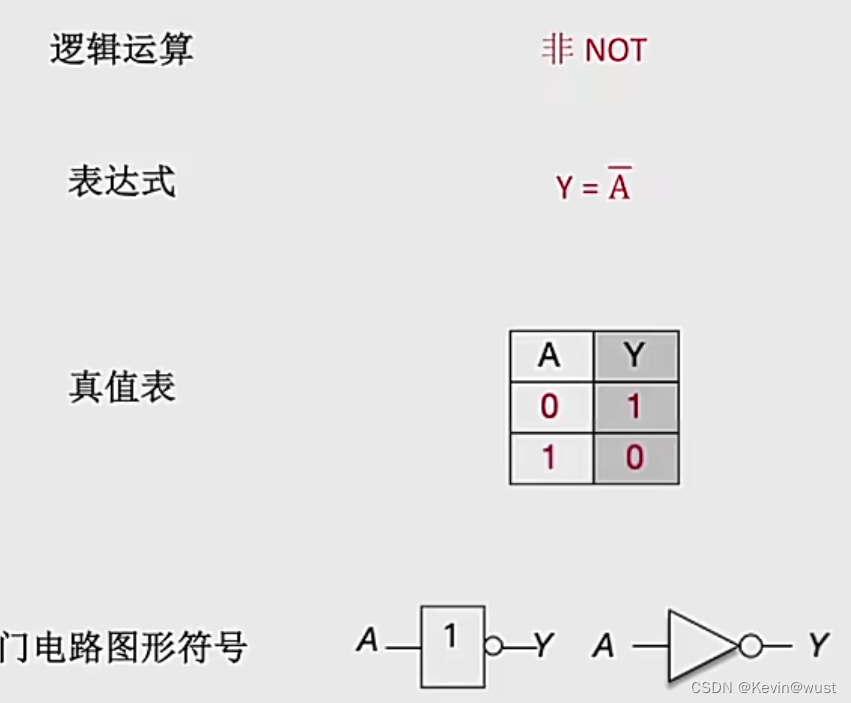

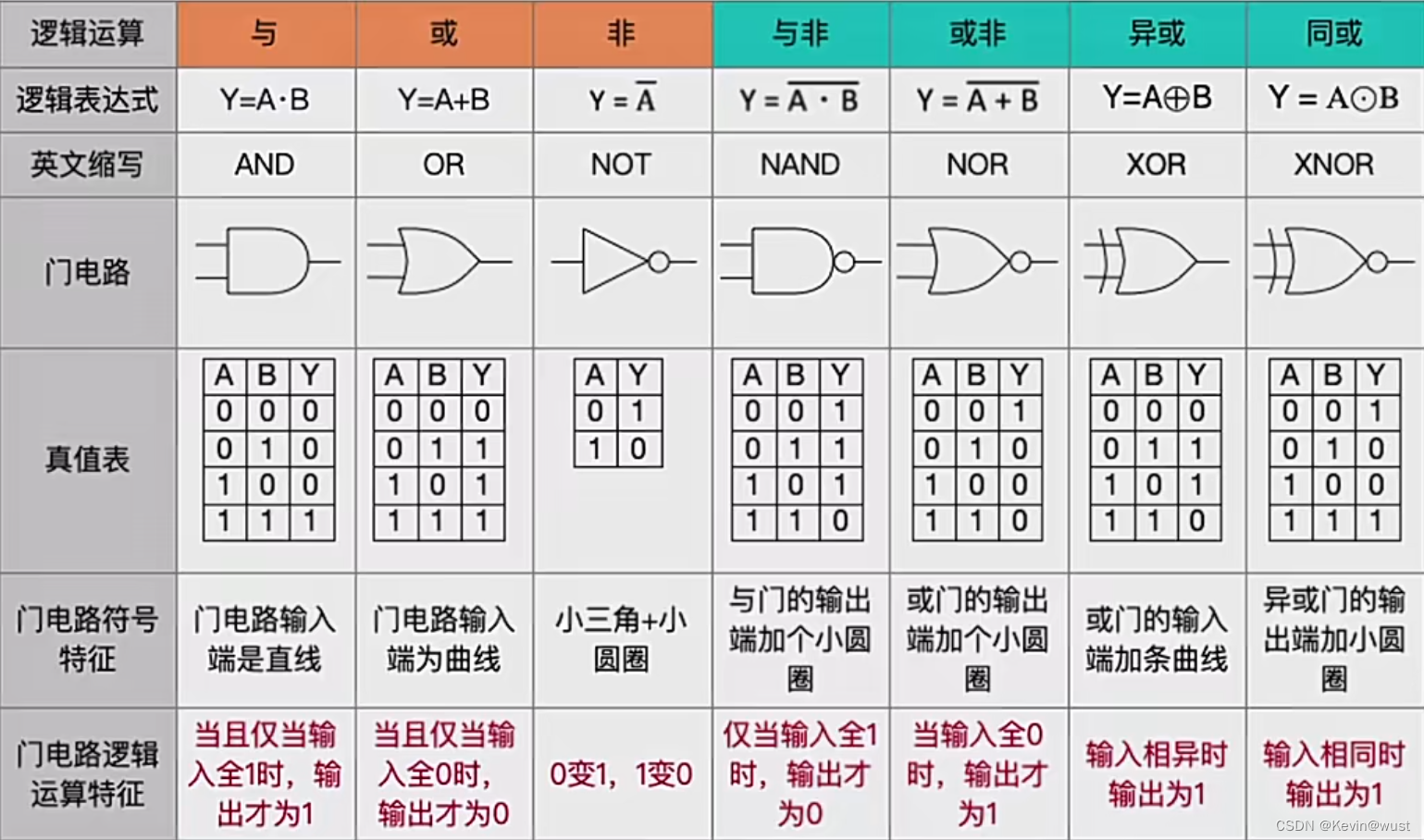

基本的门电路包括与门、或门、非门三种。

与

或

非

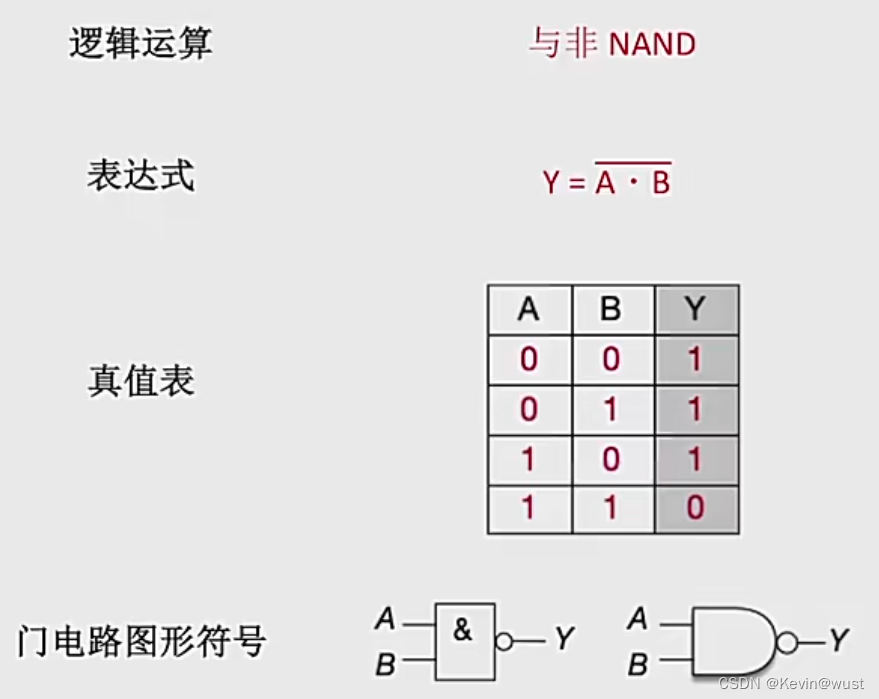

将三种基本的门电路进行组合可以得到与非门、或非门、异或门(重点)、同或门。

与非

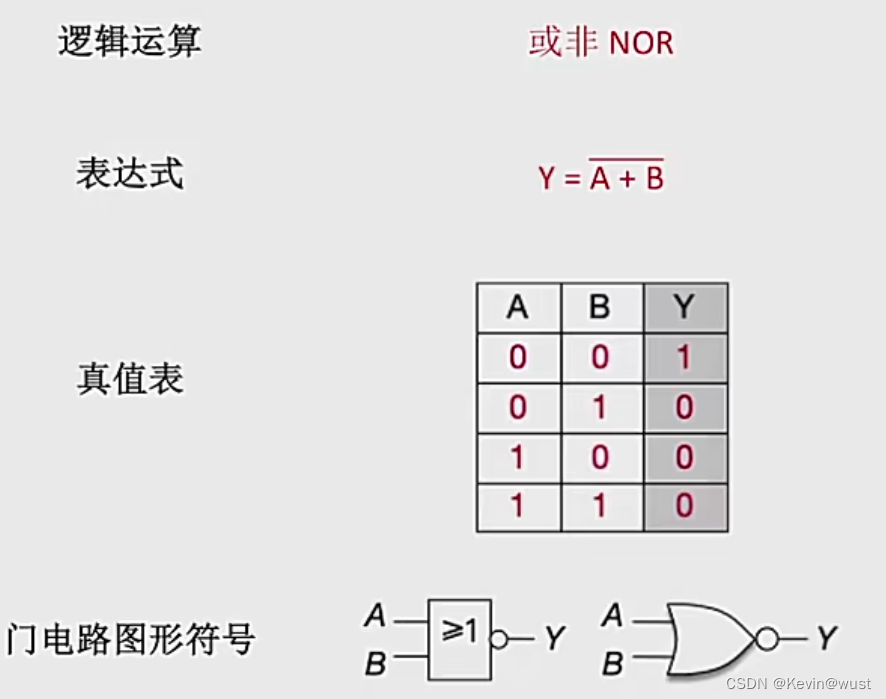

或非

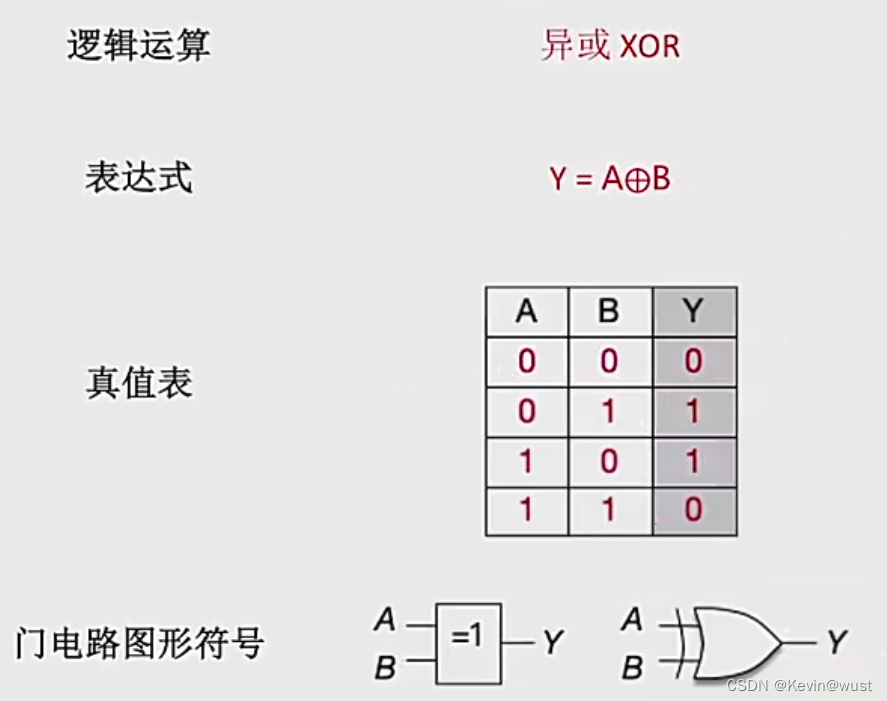

异或(重点)

可以将异或运算看作是没有进位的加法运算。

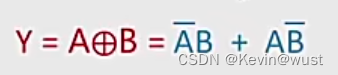

公式为:

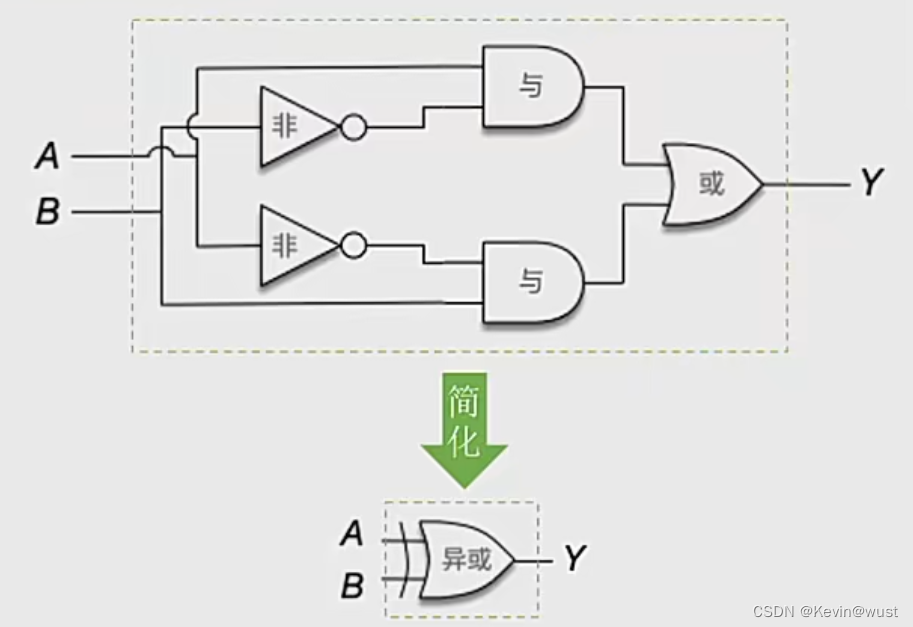

将逻辑电路“封装”简化得到下图异或门:

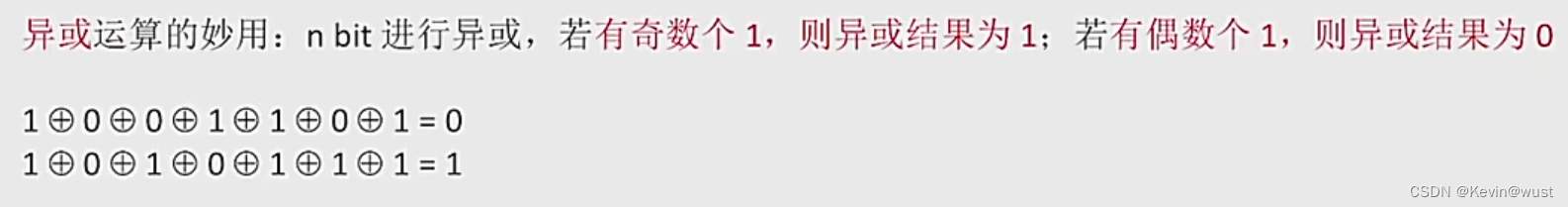

异或的妙用:

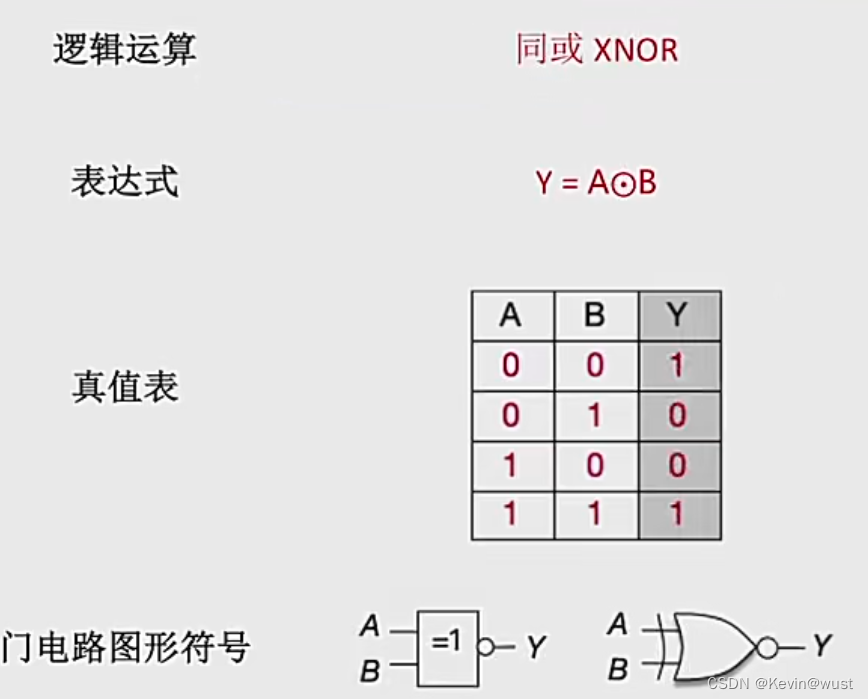

同或

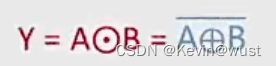

公式为:

总结

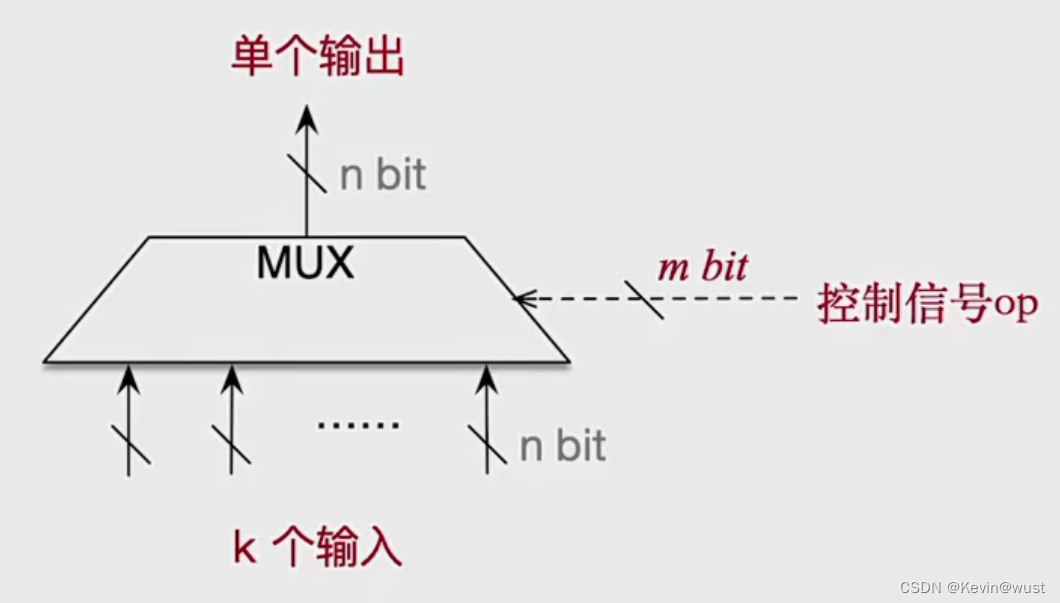

多路选择器MUX

有多个输入端,一个输出端,根据控制信号op的值,在多个输入数据种选择一个通过。

控制信号的位数与输入个数的关系:

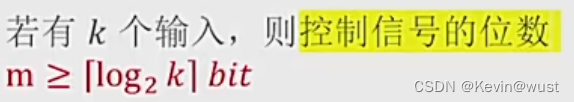

三态门

一个输入端,一个输出端,根据控制信号op的值,决定是否通过输入。

op = 0 不可通过

op = 1 可通过

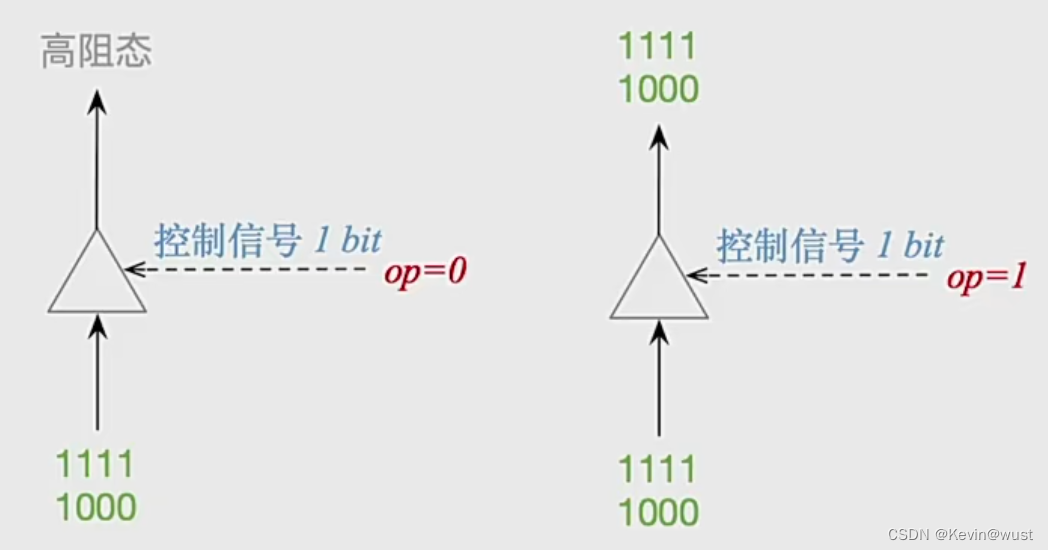

一位全加器

将逻辑电路“封装”简化得到下图一位全加器:

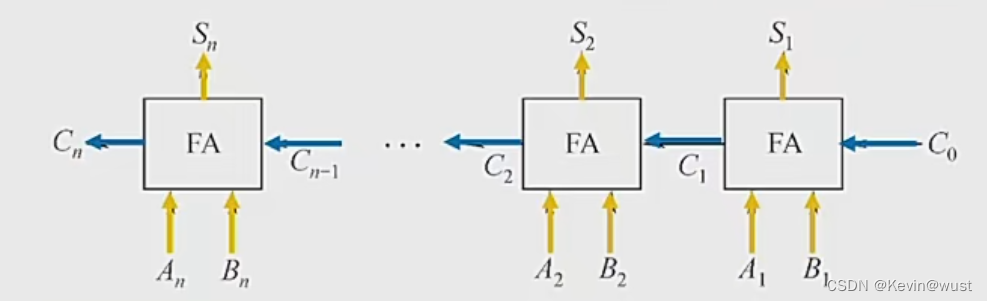

串行进位的并行加法器

每一级的进位的产生都要依赖前一级的进位,因此运算速度慢。

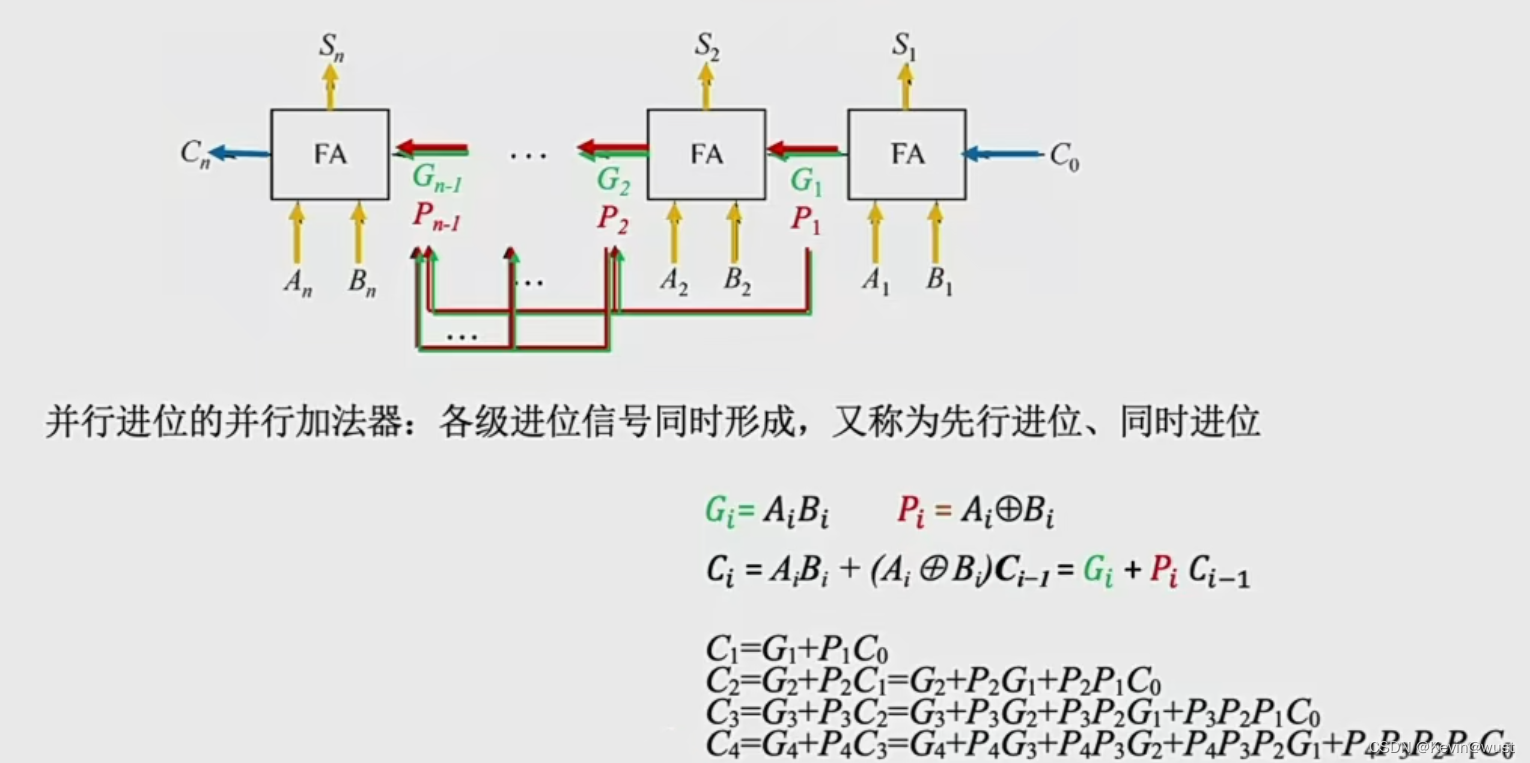

并行进位的并行加法器(了解)

简单来说,就是串行进位加法器是等前一个进位信号输入了之后再计算当前的进位,一直要“等”,即Ci需要依赖Ci-1,我们可以把公式写开,然后Ci只依赖低位的G和P,G和P是AB运算的结果,各个1位全加器的AB是可以同时输入的,所以我们能同时得到,低位的G和P,从而可以实现并行进位加法器。

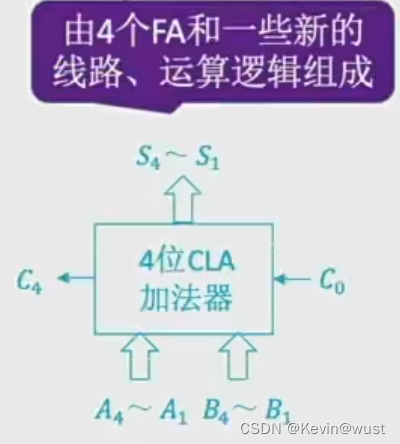

并行进位加法器相当于速度变快了,但是线变多了,可以将两者结合起来,用4位并行进位加法器,连接起来,达到一个适中的效果。

经典做法:

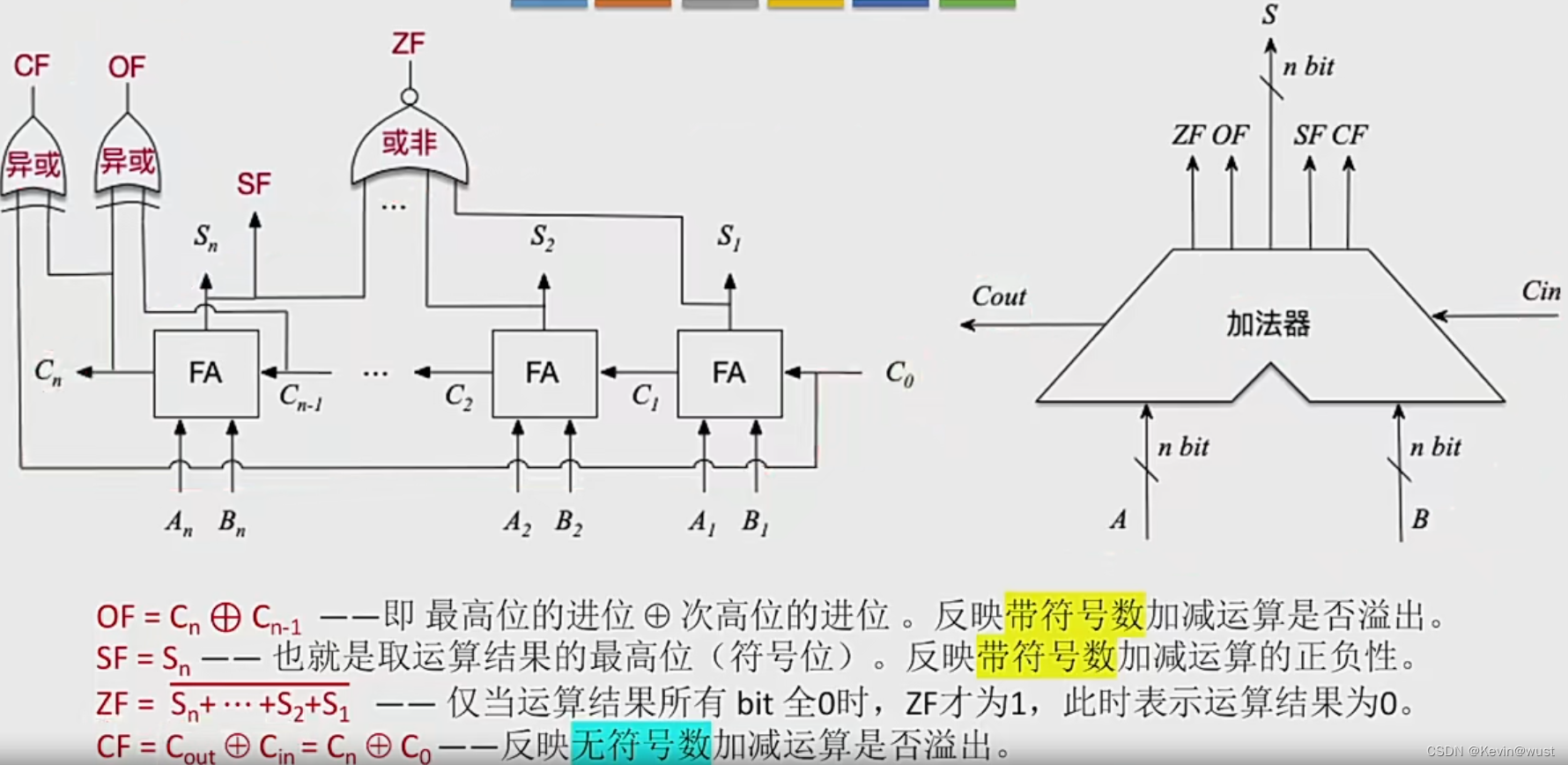

带标志位的加法器

说明:图中的Cin即C0、Cout即Cn。

将逻辑电路“封装”简化得到下图带标志位的加法器:

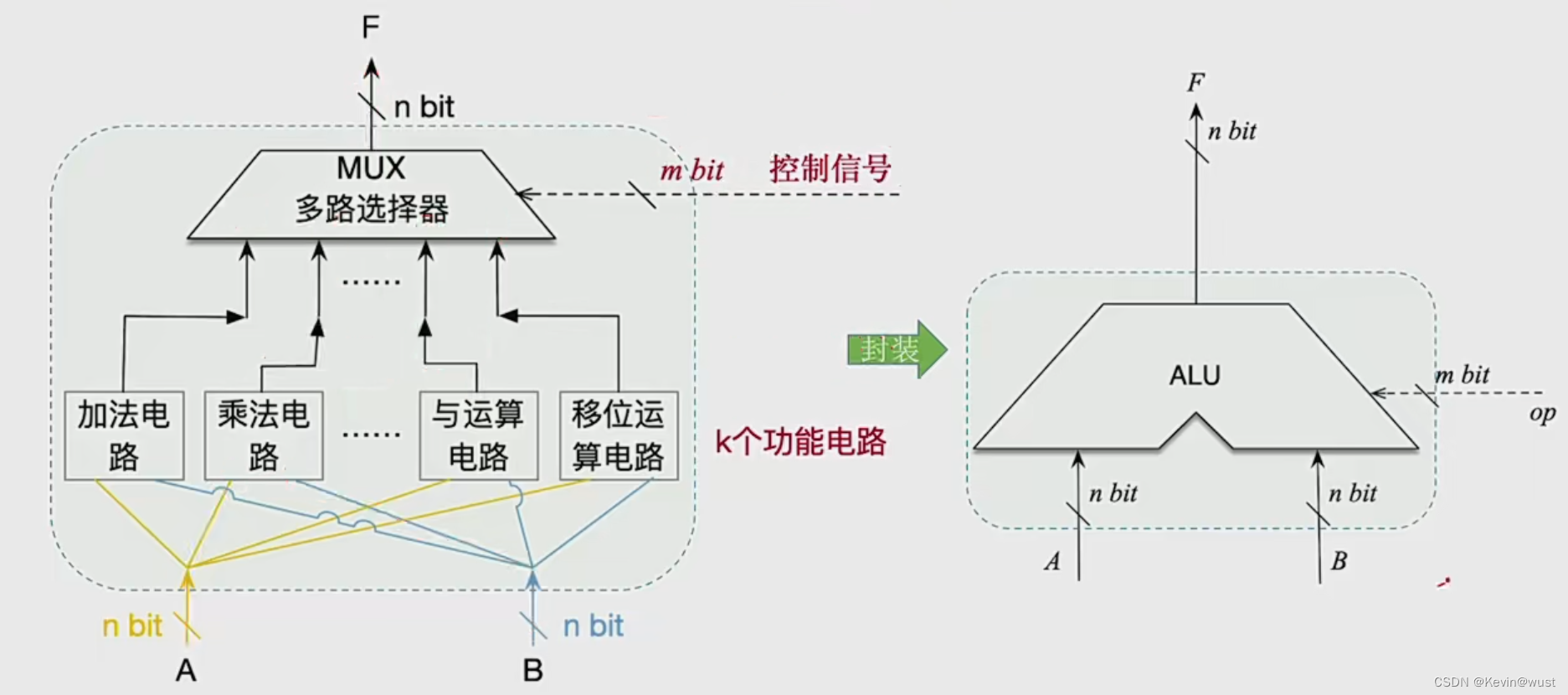

算术逻辑单元(ALU)

控制信号位数由功能电路的个数确定。

将逻辑电路“封装”简化得到下图算术逻辑单元(ALU):

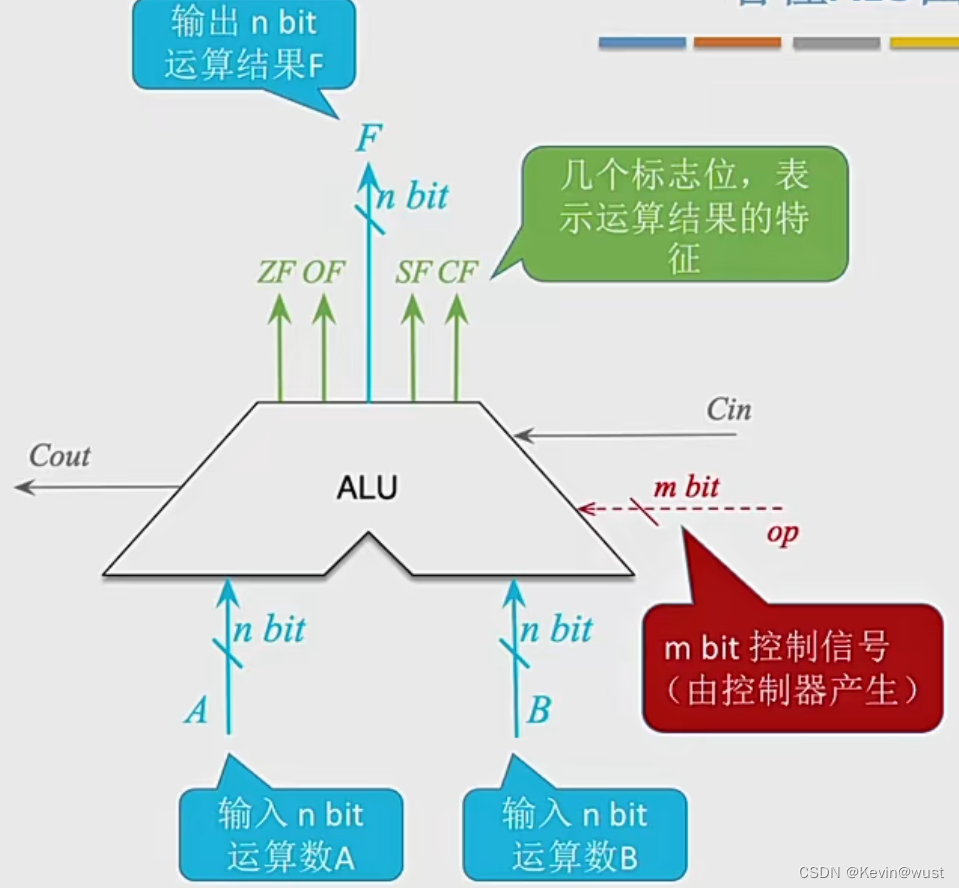

加上标志位,得到最终版本:

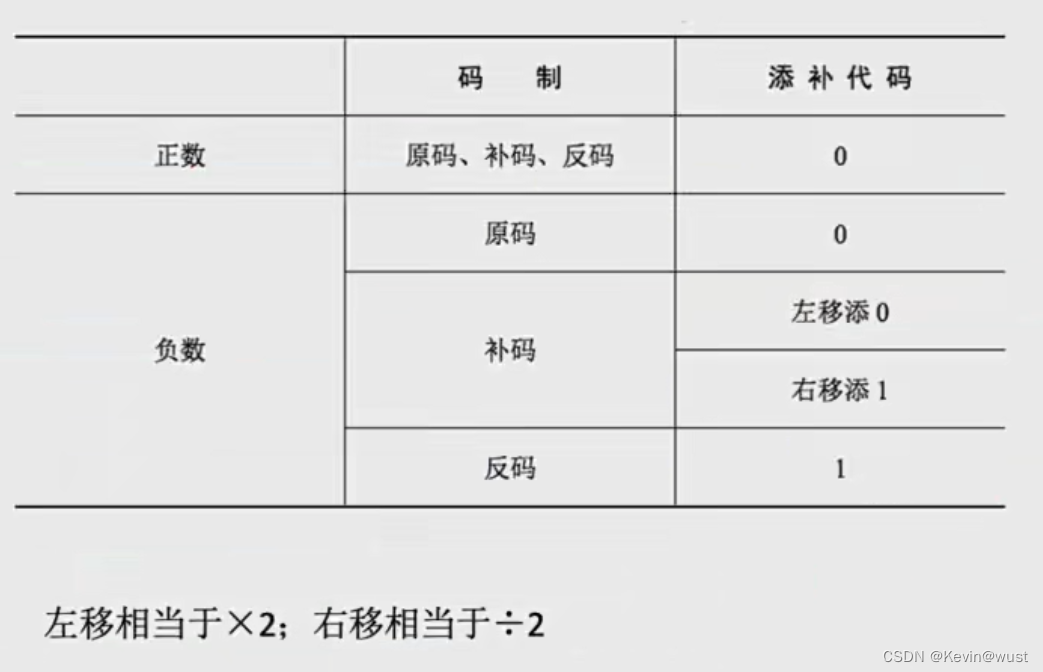

移位操作

逻辑移位:补0

算术移位:

455

455

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?