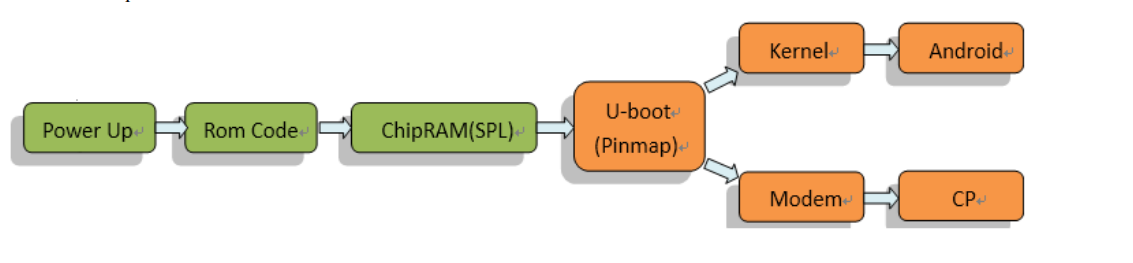

Pinmap 与 Boot 流程

Pinmap 是用软件控制寄存器的方式来配置 PAD 脚状态。在开机的初始阶段,芯片得到供电但还未加

载 pinmap.c 文件的时候,PAD 脚的状态是芯片内部固定好的,具体请参见 BB 芯片规格书或 GPIO

SPEC 文档。

EXT_RST_B 信号是 PMIC 对 BB 的复位信号,拉低复位。开机上电时,当 PMIC 芯片完成关键供电

输出后,会将 EXT_RST_B 信号拉高,接着 BB 掌控开机流程。在 EXT_RST_B 未拉高之前,称之为

BB 的 At Reset 阶段;从 EXT_RST_B 拉高到 BB 加载 pinmap.c 文件这一阶段,称之为 BB 的 After

Reset 阶段。接下来 BB 芯片 PAD 脚的状态便由 Pinmap 控制。

PAD 脚在 At Reset 和 After Reset 阶段的状态可在芯片规格书或 GPIO SPEC 中查到。在 At Reset 和After Reset 阶段,一些 PAD 状态可能为输出高电平或内部上拉等,外接电路选择不当(控制 LED/背光/SPK 等)可能会造成开机时不可控的闪烁、爆破音等。

Pinmap 从 U-boot 阶段开始起作用,如图所示:

pinmap关键字段介绍

pinmap文件存放路径:bsp/bootloader/u-boot15/board/spreadtrum/[实际使用的 Board]/pinmap.c

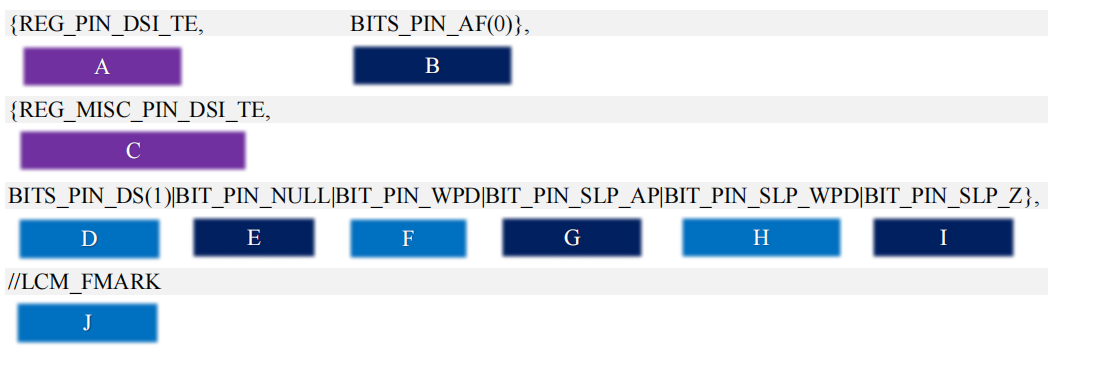

Pinmap.c 文件中对 BB 每个 PAD 的配置都分为两行,第一行配置 PAD 的“Central 寄存器”,第二行配置PAD 的“Side Band(MISC)寄存器”。下面以 DSI_TE 为例,对关键字段进行解释说明。

A:PAD 脚的“Central 寄存器”名称。“DSI_TE”为 PAD 的 Ball Name。

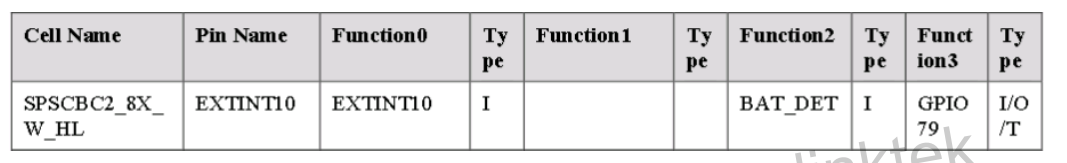

B:“Central 寄存器”的控制内容,控制 PAD 的功能。AF0~3 对应 BB 芯片规格书和 GPIO SPEC 中的 Function 0~3。

BITS_PIN_AF(3); 如果配置为 3,通过表格可以看到对应的是 GPIO79。如果配置为0,即 Function0 为 EXTINT10,在 EIC Source List 中,可以查询到对应的 EIC 控制器,说明可以作 EIC 中断使用。

C:PAD 脚的“Side Band(MISC)寄存器”名称。“DSI_TE”为 PAD 的 Ball Name。

D:“Side Band 寄存器”的控制内容,PAD 驱动强度(Drive Strength)选择。调整输出信号的驱动能力(提供对输出信号电流的控制),默认与平台版本保持一致,驱动强度过大会造成高频分量过多。输出信号时序有问题时才做调整。

E/F:“Side Band 寄存器”的控制内容,唤醒状态下 PAD 内部上下拉状态控制。

两个关键字共同控制上下拉状态,所有组合如下:

BIT_PIN_NULL|BIT_PIN_NUL 表示内部无上下拉。

BIT_PIN_NULL|BIT_PIN_WPU 表示 20 kΩ 电阻上拉。

BIT_PIN_WPUS|BIT_PIN_NUL 表示 4.7 kΩ 电阻上拉。

BIT_PIN_WPUS|BIT_PIN_WPU 表示 1.8 kΩ 电阻上拉。

BIT_PIN_NULL|BIT_PIN_WPD 表示 50 kΩ 电阻下拉。

说明:除 I2C 接口和 SIM 卡接口之外,一般不需要开启强上拉(4.7 kΩ/1.8 kΩ),保持与平台一致即可。IO口只有作为输入时才配置上下拉,主要是为了钳制电位;作信号输出时,高低电位由软件决定,无需配置上下拉。

WPU(Weak Pull Up):是弱上拉。

WPUS(Weak Pull Up Selection):上拉强度选择。

WPD(Weak Pull Down):弱下拉。

G:“Side Band 寄存器”的控制内容,PAD 休眠控制选择。PAD 在唤醒时,其状态动态可变;休眠后只能静态保持一种状态。具体的对外表现状态由关键字 H和 I 决定。PAD 的休眠选择:PAD 应与其信号 Controller 所在的子系统一起休眠。C 文件在开头对一些子系统的集合作出了定义[1],也可以直接将多个子系统并列写,作“与”逻辑。如 BIT_PIN_SLP_AP|BIT_PIN_SLP_AUDCP,表示在 AP 和 AUDCP 都休眠时(“与”),信号才进入休眠。休眠状态相关的关键字只有在休眠状态下才会生效,如休眠项配置为 BIT_PIN_SLP_NONE,则 PAD不会休眠,关键字 H 和 I 一直不会生效。

H:“Side Band 寄存器”的控制内容,休眠后 PAD 内部上下拉状态控制[2]。

BIT_PIN_SLP_WPU 表示弱上拉

BIT_PIN_SLP_WPD 表示弱下拉

BIT_PIN_SLP_NUL 表示无上下拉

此处的状态是为了控制信号在休眠后的内部上下拉,此时上拉电阻固定为 20K。

I:“Side Band 寄存器”的控制内容,休眠后 PAD 的输入输出状态[2]。

BIT_PIN_SLP_IE 表示输入

BIT_PIN_SLP_OE 表示输出

BIT_PIN_SLP_Z 表示高阻

PAD 未休眠时,其信号的输入/输出方向由内部 Controller 决定;PAD 休眠后,其信号方向将为单一

固定方向,由此关键字控制。

说明:

IE(Input Enable,输入使能)使能时为输入,PAD 与内部输入门电路连接。

OE(Output Enable,输出使能)使能时为输出,PAD 与内部输出门电路连接。

IE/OE 都不使能时为高阻,PAD 与内部输入/输出门电路都断开。

J:注释网络名等信息,增加可读性。

注:PAD 休眠后,可以通过关键字 H 和 I 配置 PAD 此时的状态:

BIT_PIN_SLP_WPU|BIT_PIN_SLP_Z

表示 PAD 休眠后与内部输入/输出门电路都断开,内部上拉,对外表现高电平。

用于子系统休眠后 BB 端无需收发数据,但外设端需要高电平的信号,如 I2C 信号等。

BIT_PIN_SLP_WPD|BIT_PIN_SLP_Z

表示 PAD 休眠后与内部输入/输出门电路都断开,内部下拉,对外表现低电平。

用于子系统休眠后 BB 端无需收发数据,但外设端需要低电平的信号。

BIT_PIN_SLP_NUL|BIT_PIN_SLP_Z

表示 PAD 休眠后与内部输入/输出门电路都断开,内部无上下拉,对外表现悬空。

用于子系统休眠后 BB 端无需收发数据,外设端对电平也没有要求的信号(PAD 悬空时会耦合相

邻 PAD 的跳变电平,因此尽量不要配置此状态)。

BIT_PIN_SLP_NUL|BIT_PIN_SLP_OE

表示 PAD 休眠后保持与内部输出门电路的连接,输出电平由内部寄存器决定,无须配置上下拉。

用于子系统休眠后,BB 端需要保持输出的信号,如复位信号等。

BIT_PIN_SLP_XXX|BIT_PIN_SLP_IE

表示 PAD 休眠后保持与内部输入门电路连接,内部上下拉的选择与工作状态下的一致。

用于子系统休眠后,BB 端仍需保持接受状态的信号,如中断信号等。

2377

2377

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?