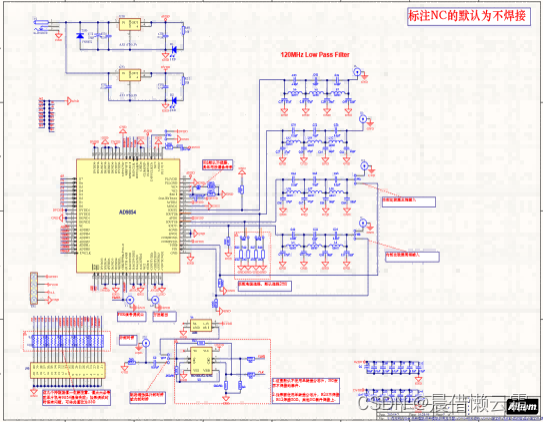

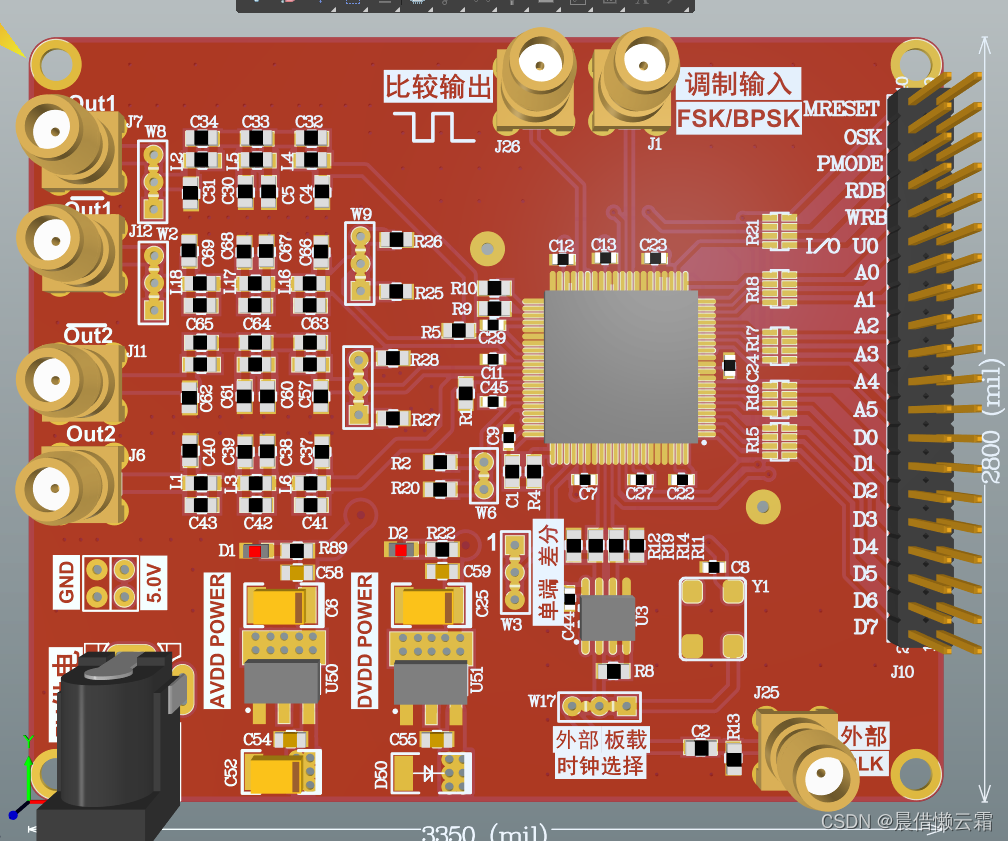

AD9854的原理图、PCB源文件(AD软件格式),包含两个版本

原理图上注明了详细的原理说明以及注意事项;考虑周全的设计,

将各种接口均有留出,在一些的地方留有排针可供切换不同模式,充足的电

源滤波电容等; 优秀合理的PCB布局布线,PCB上标有相关丝印注明,同时

采用3D封装以方便配合结构设计

获取链接:

【闲鱼】https://m.tb.cn/h.g6FDtkV?tk=s2nY30aFutt CZ0012 「我在闲鱼发布了【AD9854 原理图pcb高速DDS信号发生器模块 高频信号】」

点击链接直接打开

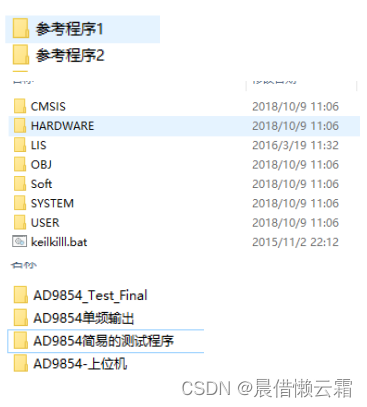

部分驱动程序

//====================================================================================

//函数名称:void AD9854_Init(void)

//函数功能:AD9854初始化

//入口参数:无

//出口参数:无

//====================================================================================

void AD9854_Init(void)

{

AD9854_IO_Init();

AD9854_WR=1;//将读、写控制端口设为无效

AD9854_RD=1;

AD9854_UDCLK=0;

AD9854_RST=1; //复位AD9854

AD9854_RST=0;

AD9854_WR_Byte(0x1d,0x00); //关闭比较器

AD9854_WR_Byte(0x1e,CLK_Set); //设置系统时钟倍频

AD9854_WR_Byte(0x1f,0x00); //设置系统为模式0,由外部更新

AD9854_WR_Byte(0x20,0x60); //设置为可调节幅度,取消插值补偿

AD9854_UDCLK=1; //更新AD9854输出

AD9854_UDCLK=0;

}

//====================================================================================

//函数名称:void Freq_convert(long Freq)

//函数功能:正弦信号频率数据转换

//入口参数:Freq 需要转换的频率,取值从0~SYSCLK/2

//出口参数:无 但是影响全局变量FreqWord[6]的值

//说明: 该算法位多字节相乘算法,有公式FTW = (Desired Output Frequency × 2N)/SYSCLK

// 得到该算法,其中N=48,Desired Output Frequency 为所需要的频率,即Freq,SYSCLK

// 为可编程的系统时钟,FTW为48Bit的频率控制字,即FreqWord[6]

//====================================================================================

void Freq_convert(long Freq)

{

ulong FreqBuf;

ulong Temp=Freq_mult_ulong;

uchar Array_Freq[4]; //将输入频率因子分为四个字节

Array_Freq[0]=(uchar)Freq;

Array_Freq[1]=(uchar)(Freq>>8);

Array_Freq[2]=(uchar)(Freq>>16);

Array_Freq[3]=(uchar)(Freq>>24);

FreqBuf=Temp*Array_Freq[0];

FreqWord[0]=FreqBuf;

FreqBuf>>=8;

FreqBuf+=(Temp*Array_Freq[1]);

FreqWord[1]=FreqBuf;

FreqBuf>>=8;

FreqBuf+=(Temp*Array_Freq[2]);

FreqWord[2]=FreqBuf;

FreqBuf>>=8;

FreqBuf+=(Temp*Array_Freq[3]);

FreqWord[3]=FreqBuf;

FreqBuf>>=8;

FreqWord[4]=FreqBuf;

FreqWord[5]=FreqBuf>>8;

}

//====================================================================================

//函数名称:void AD9854_SetSine(ulong Freq,uint Shape)

//函数功能:AD9854正弦波产生程序

//入口参数:Freq 频率设置,取值范围为0~(1/2)*SYSCLK

// Shape 幅度设置. 为12 Bit,取值范围为(0~4095) ,取值越大,幅度越大

//出口参数:无

//====================================================================================

void AD9854_SetSine(ulong Freq,uint Shape)

{

uchar count;

uchar Adress;

Adress = 0x04; //选择频率控制字地址的初值

Freq_convert(Freq); //频率转换

for(count=6;count>0;) //写入6字节的频率控制字

{

AD9854_WR_Byte(Adress++,FreqWord[--count]);

}

AD9854_WR_Byte(0x21,Shape>>8); //设置I通道幅度

AD9854_WR_Byte(0x22,(uchar)(Shape&0xff));

AD9854_WR_Byte(0x23,Shape>>8); //设置Q通道幅度

AD9854_WR_Byte(0x24,(uchar)(Shape&0xff));

AD9854_UDCLK=1; //更新AD9854输出

AD9854_UDCLK=0;

}

7854

7854

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?