首先,我们先要回顾了解一下CPU(中央处理器)的功能。

CPU执行指令的过程:

- 取指令

- PC+“1”送PC (程序计数器,存下面要取指令的地址,默认是紧挨着的下一条指令,这里的“1”指的是一条指令,有的会写PC+“4”,这里的4指的是4个字节,其实还是一条指令,功能是一样的)

- 指令译码(解析指令,指令的格式很明确的规定好了,先取出操作码(最高的六位),就可以知道这是哪一种指令,还可以知道操作数的地址,去寄存器里面取操作数)

- 进行主存地址运算

- 取操作数(参加运算的数,一般会放到寄存器里面)

- 进行算术/逻辑运算(ALU)

- 存结果(可能会是寄存器(最常见),有的运算结果不需要存,仅仅需要标志位)

- 以上每一步都需要检测异常,若有则自动切换到异常处理程序(虽然会得到一个不正确的结果,但不要想着如何去修复,直接送到异常处理程序,不用管这错误)

- 检测是否有“外部中断”,若有则转中断处理(其实就是强行终止任务,比如你做PPT呢,突然有人给你QQ发消息,那么你就先需要中止做PPT这个工作,来捕获别人发给你的消息,然后再去做PPT,这个过程就是外部中断)(指令执行完进行检测,非常复杂,需要专门的硬件才能实现8259)

指令的四种基本操作:

- 主存->寄存器(取指,取数)

- 寄存器->主存(存结果)

- 寄存器->寄存器或者ALU(取数,存结果)

- 算数或逻辑运算(运算,计算地址,PC计算)

操作功能用RTL描述

- 用R[r]表示寄存器r的内容

- 用M[addr]表示贮存单元addr的内容

- 传送方向用"<-"表示

- 直接用PC表示其内容(PC本身就是一个寄存器,PC本身没有意义,直接用PC来表示里面的内容)

例如:R[$8]<-M[R[$9]+4]的含义是:将寄存器$9的内容加4作为地址,读取该地址的内存单元的内容送寄存器$8(是不是很好理解)

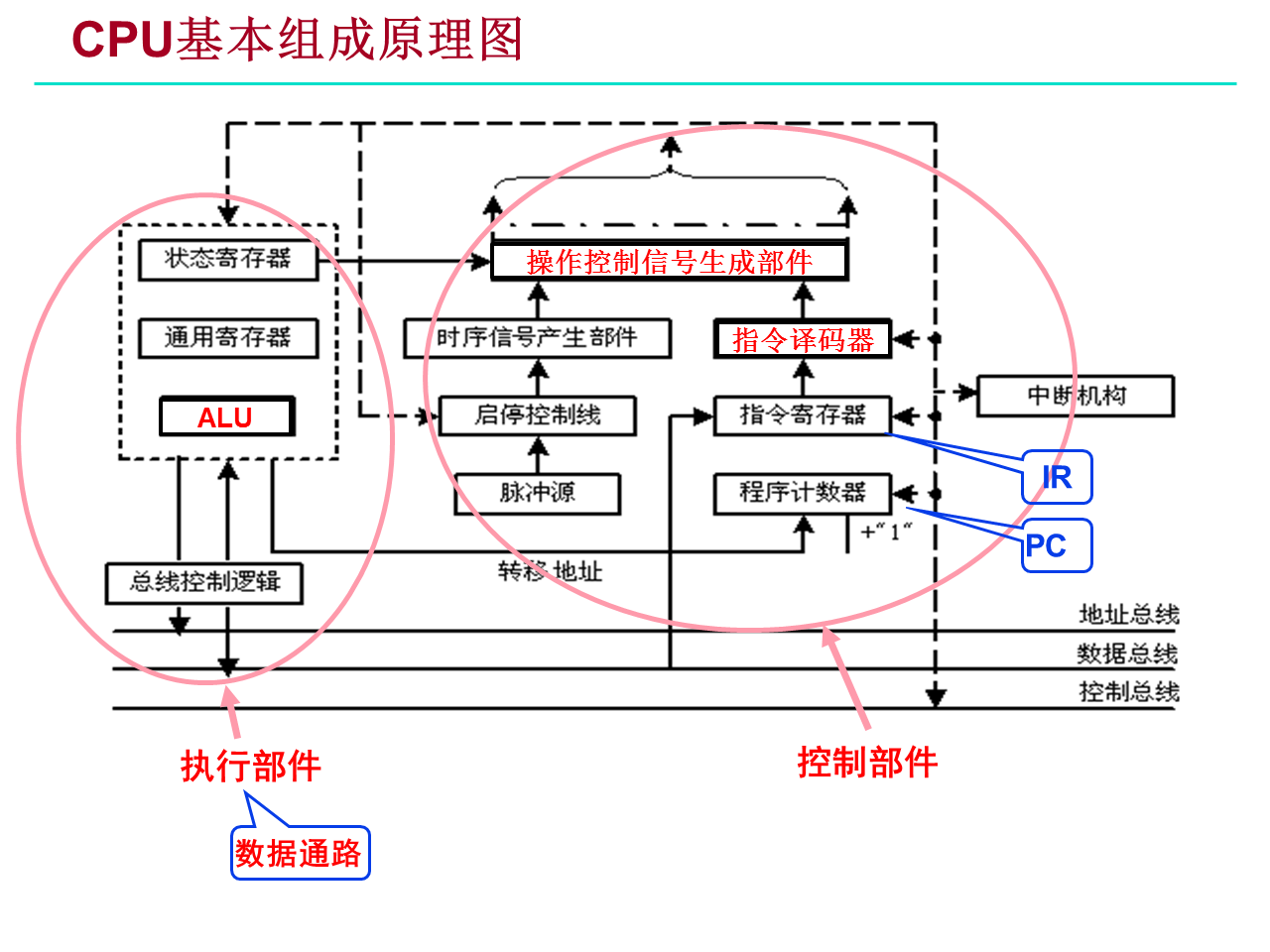

CPU基本组成原理图:

主存和CPU都挂到总线上去,说明是联通的。程序技术器存着指令的地址,然后根据这个从总线上读取在哪个存储单元,将其存到指令寄存器中,再送到指令译码器。再到操作控制信号生成部件(指令产生的控制信号),将指令和操作数放到执行部件,根据指令进行相应的操作。(控制部件读指令存储控制信号,执行部件根据控制信号进行相应的操作),执行部件-->执行部件。

什么是数据通路呢?

- 指令执行过程中数据经过的路径,包括路径中的部件,是执行部件。

控制器的功能是什么?

- 指令译码,生成控制信号,控制数据通路的动作,是控制部件。

数据通路的基本结构:进行数据传送、运算、存储。

数据通路由两类元件组成:组合逻辑原件和时序逻辑元件

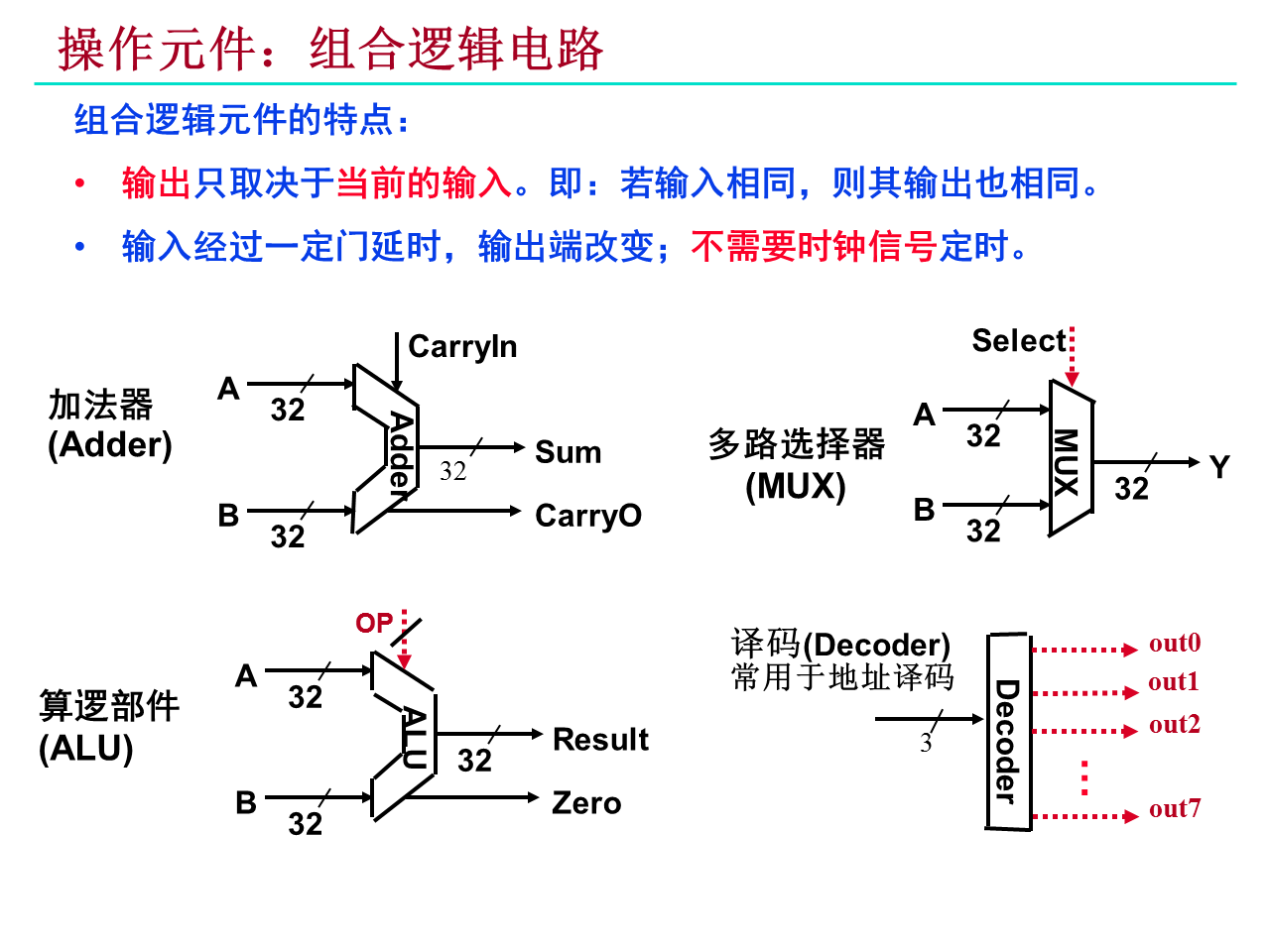

操作元件:组合逻辑电路

- 输出只取决于当前的输入,即:若输入相同,则其输出也相同。

- 输入经过一定门延迟,输出端改变;不需要时钟信号定时。

常用译码器:4选1,8选1,16选1

如8选1:那就需要三根线来实现,如000对应out0,即74138译码器,利用这个方法可以唯一的选中一个。

以上所有元件都不需要时钟!!!

存储元件:时序逻辑电路

- 特点:

- 具有存储功能,时钟控制下输入被写入到电路,输出不需要时钟,输入需要时钟来控制。

- 时钟决定何时将输入端状态写入元件,输出端状态随时可以读出

- 触发:状态单元中的值在时钟边沿改变

- 上升沿触发 下降沿触发

最简单的状态单元:D触发器

一个时钟输入 一个状态输入 一个状态输出

存储元件:寄存器和寄存器组(可以用D触发器拼在一起,一个D触发器为1位)

寄存器:

- 时钟clk,写入

- 写使能信号(WE信号),允不允许将输入线上的信号写入寄存器中(低有效:WE上画一条横线)绝大多数为低有效

寄存器组:

- 一个写口(时序逻辑操作):

- 写使能且时钟来时,busW的值写入RW指定的寄存器中。RW本质上是地址。

- 两个读口(便于三总线,组合逻辑操作):

- RA和RB给出地址,经过延迟后busA和busB有效

存储器模型(主存):

理想存储器:

- Data In:32位写入

- Data Out:32位读出

- Address:读写公用32位地址

- 写操作(时序逻辑):WE=1时,Clk边沿到来时,Data In写入Address指定的存储单元

- 读操作(组合逻辑):Address有效后,经一个取数时间,DataOut上数据有效

数据通路(状态元件+操作元件)与时序控制

组成:...+状态元件+操作元件(组合电路)+状态元件+...

时钟到来时,前一个时钟生成的数据被写入状态元件,然后输出到操作元件,经过若干们延迟后输出,下一个时钟到来时写入状态元件。各级有延迟。

时钟周期=Latch Prop + Longest Delay Path + Setup + Clock Skew(时钟偏斜)

3003

3003

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?