目录

看完有收获给我点个赞这对我很重要🌹🌹🌹🌹

你的点赞让我的创作更有动力⭐⭐⭐⭐⭐

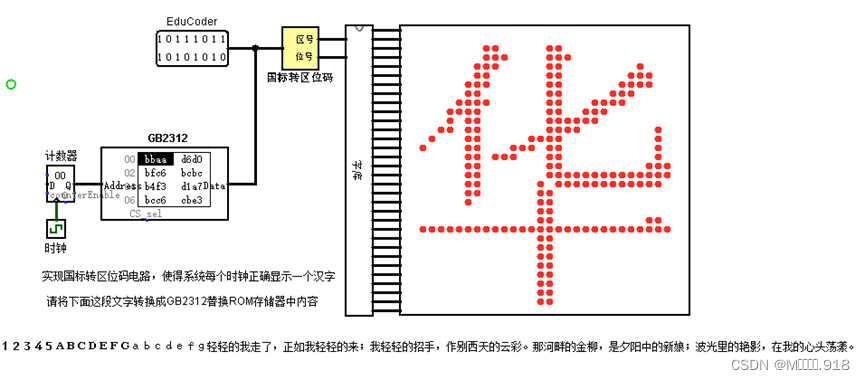

第1关:汉字国标码转区位码实验

国标码与区位码的定义

- 国标码是二字节码,用两个七位二进制数编码表示一个汉字。

- 为了使每一个汉字有一个全国统一的代码,区位码是国家规定的94×94的一个方阵,其中每行叫做一个区,每列叫做一个位,组合起来就组成了区位码。

⭐国标码与区位码转换:

国标码=区位码(十六进制)+2020H

区位码=国标码+FFFF-2020H+0001H=国标码+dfe0

由于采用加法器,所以用补码的形式表示,-2020H的补码为def0

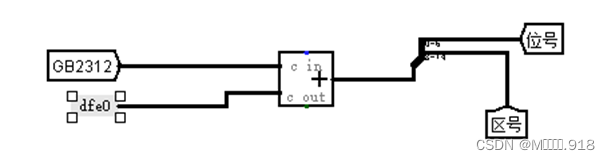

引入一个常量,把数据位宽设置位16位,并且复制为def0,把常量和GB2312连接到加法器上,加法器的另一端连接到集线器上,连线方式如图1.1所示:

图1.1:国标转区位码电路

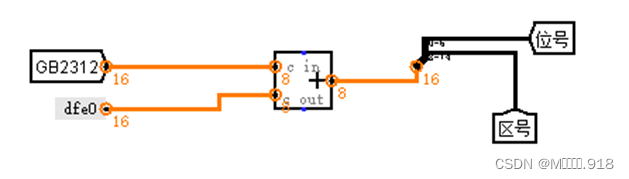

可能会遇到的问题,问题电路如图1.2所示:

图1.2:国标转区位码电路报错

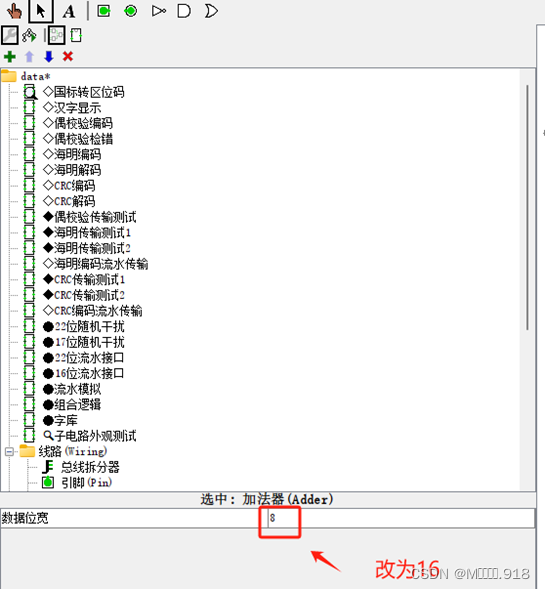

上图的问题导致的原因是因为,加法器的数据带宽和常量国标码的位数不一致导致的,我们可以点击加法器,然后在最下角的数据位宽改为16即可,如图1.3所示:

图1.3:设置数据位宽

第2关:汉字机内码获取实验

第一步:点击到汉字显示电路可以观察到如图1.4显示的结果:

图1.4:汉字显示电路

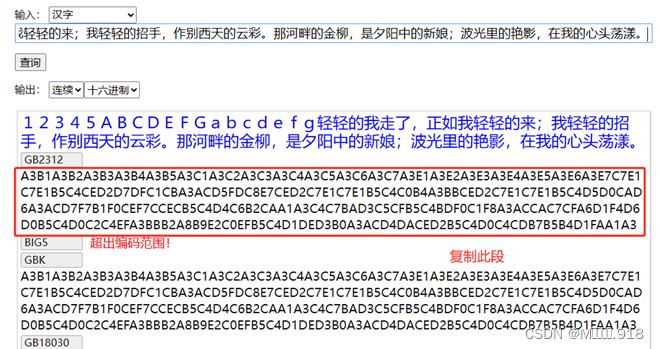

第二步:要把下面一段文字替换为GB2312,我们可以访问网站 汉字字符集编码查询;中文字符集编码:GB2312、BIG5、GBK、GB18030、Unicode (qqxiuzi.cn),查看这段文字对应的GB2312(GBK)的值,如图1.5所示:

图1.5:文字转化GB2312结果

但是我们需要把上面文本调整为4个一行的格式才可以直接粘贴到编辑器中

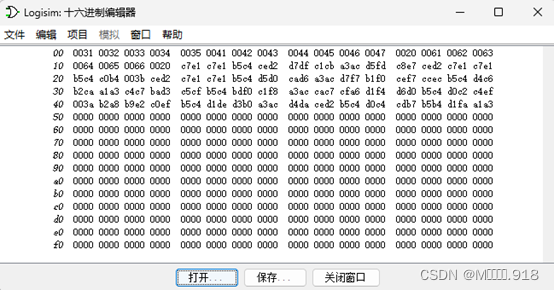

第三步:把刚刚获取到的GBK的值编辑到logisim十六进制编辑器中,删除之前的,粘贴进去即可,如图1.6所示:

图1.6:编辑器内容

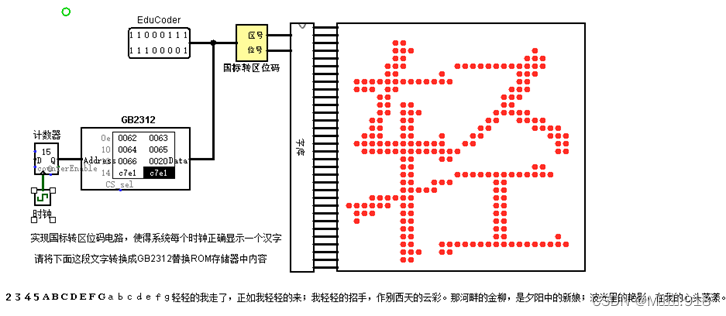

第四步:退出编辑器,在logisim的绘图区按CTRL+K自动运行时钟,会得到如图1.7所示结果:

图1.7:汉字电路显示结果

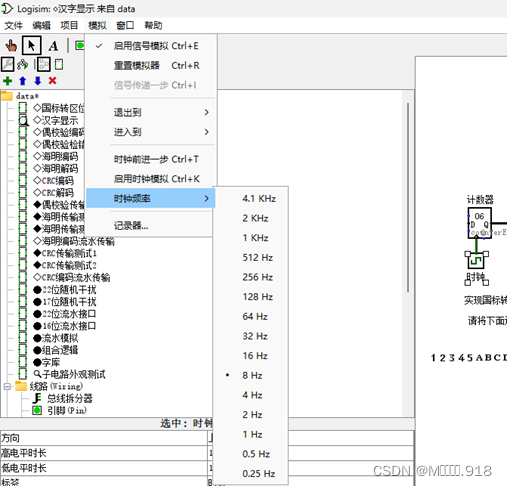

❗注意:关于如何调整时钟频率,以及如何重新启动模拟器

点击模拟->重启模拟器就可以实现重启模拟器

点击时钟频率我们可以把时钟频率切换为视频中推荐的频率8Hz,具体如图1.8所示:

图1.8:时钟频率设置

第3关:偶校验编码设计

- 奇校验:编码中有奇数个1,发送给接收方,接收方收到后,会计算收到的编码有多少个1,如果是奇数个,则无误,是偶数个,则有误

- 偶校验:编码中有偶数个1

- 奇偶校验:只能检测1位错,无法检查出偶数个错误,并且无法纠错

- 假设计算机规定好的是奇校验,发送方发送的编码是01101 0,而接收方收到的是11111 0,但是奇数个1,符合奇校验,但有两个0变成了1,所以奇偶校验只能检测出1位错误,且没法纠错。

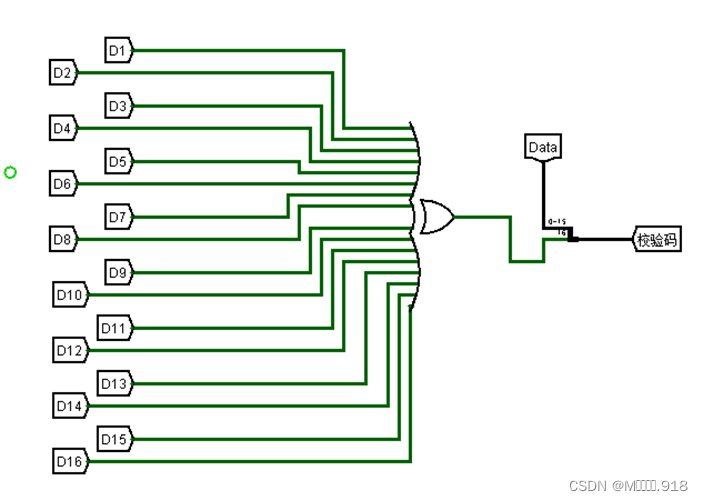

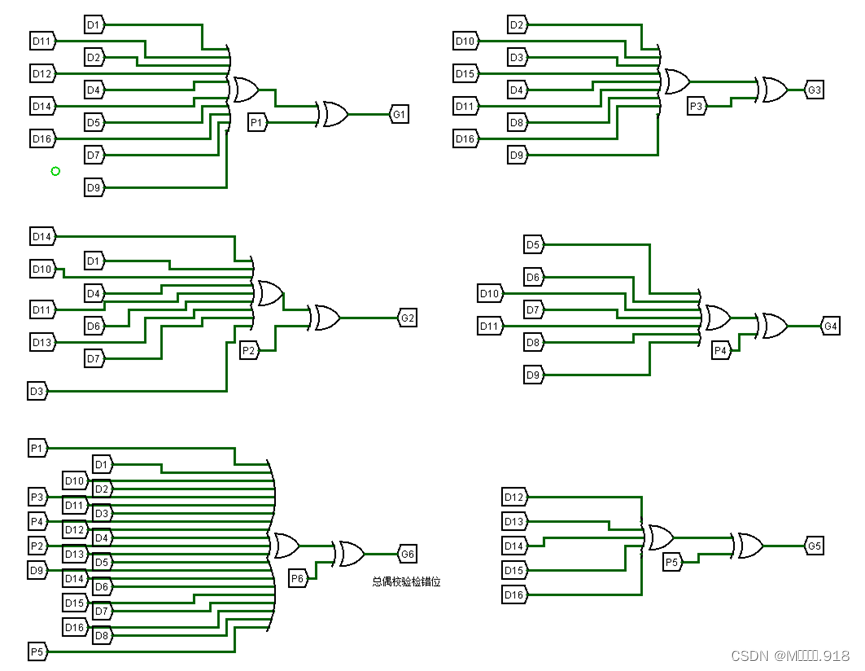

第一步:那一个异或门到绘图区,并且设置异或门的输入引脚位数为16位,如图1.9所示:

图1.9:16引脚异或门

第二步:把每一位数据对应连接到异或门的引脚上,一个引脚直连一位数据,不可以有交叉,然后把异或门的输出端连接到分线器的16号端口上,结果如图1.10所示:

图1.10:偶校验电路图

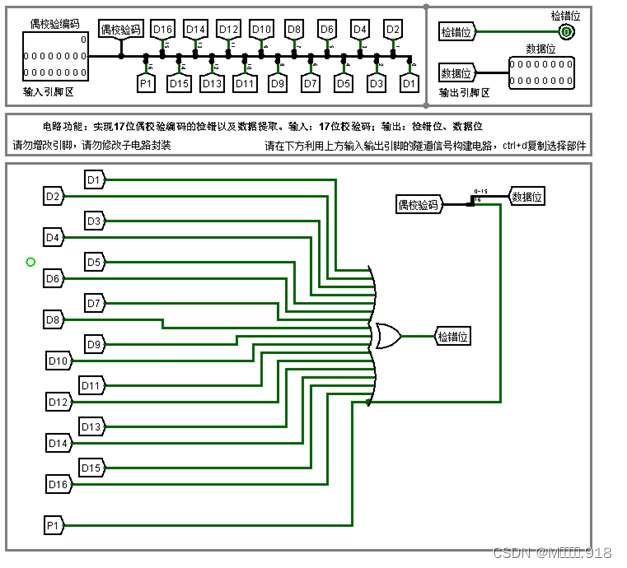

第4关:偶校验解码电路设计

也就是把偶校验位,送去与数据位的数据去做异或运算,如果检错位为奇数,说明有错误发生;如果检错位为偶数,说明数据是正确的。

所以只需要按照图1.11连线即可:

图1.11偶校验解码

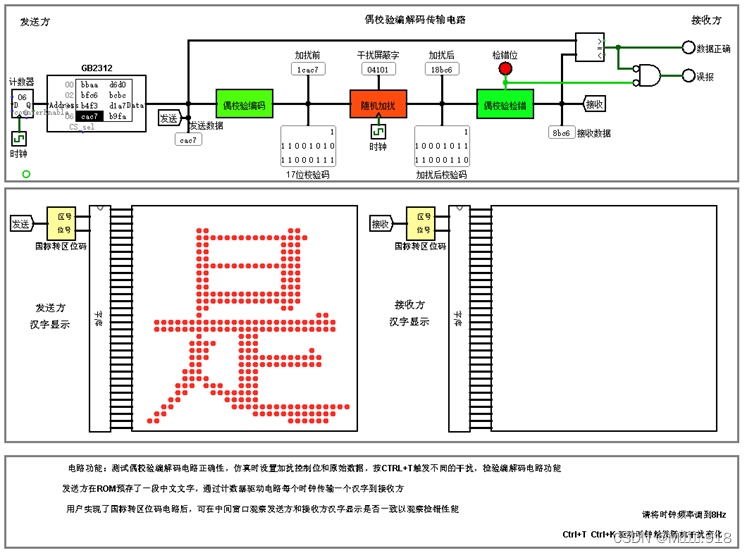

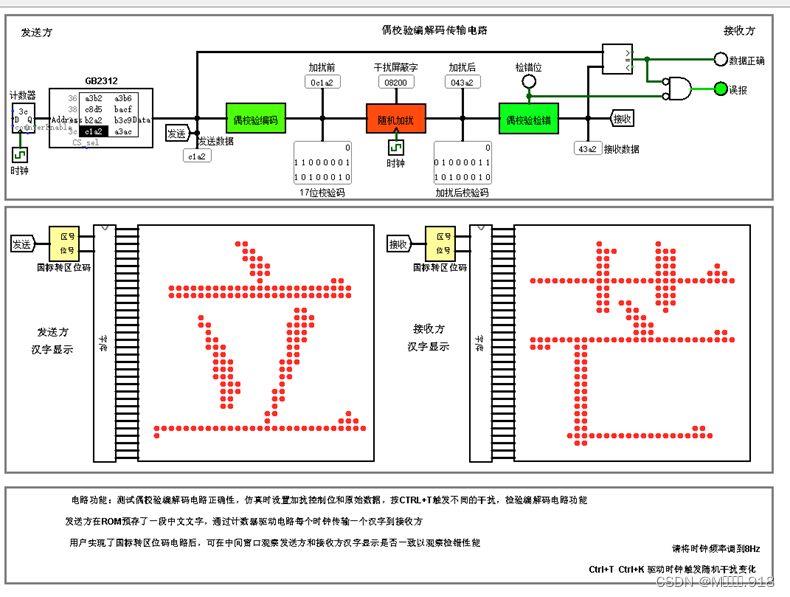

第5关:偶检验传输测试

(1)传输过程中没有错误,左右两边的字相同,“检错位”不亮灯,“数据正确”亮绿灯。

(2)有奇数个错误,“检错位”亮红灯,结果如图1.12所示:

图1.12奇数个错误

(3)有偶数个错误,偶校验无法检测出偶数个错误,“误报”亮绿灯,如图1.13所示:

图1.13:偶数个错误报错

第6关:海明编码

我们首先要理解海明编码的原理。海明编码是设置多个奇偶校验位来实现纠错能力的。

每一个检验位都在特点的位置上。

一般有一个公式来算我们需要多少个检验位。

K+r <= 2^r - 1

k是多少位信息,r是需要的检验位.

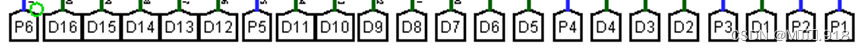

这道题目k=16,所以我们需要5位检验位+1位总检验位。所以一共是22位海明编码。

而且检验位的位置一般是2^i-1(1,2,4,8,……)

p1,p2,p3……都是检验位,而D1,D2,D3……都是数据位.

每一个数据位都由最少两位检验位检验。

例如

D1:P1,P2(3=1+2 这里的1、2是第几位)

D2:P1,P3(5=1+4)

D3:P2,P3

D4:P1,P2,P3

D5:P1,P4

D6:P2,P4

D7:P1,P2,P4

D8:P3,P4

D9:P1,P3,P4

D10:P2,P3,P4

D11:P1,P2,P3,P4

D12:P1,P5

D13:P2,P5

D14:P1,P2,P5

D15:P3,P5

D16:P1,P3,P5

所以我们可以知道P1~P6分别检验的是什么数据位,如下表内容所示:

| P1 | B1,B2,B4,B5,B7,B9,B11,B12,B14,B16 |

| P2 | B1,B3,B4,B6,B7,B10,B11,B13,B14 |

| P3 | B2,B3,B4,B8,B9,B10,B11,B15,B16 |

| P4 | B5,B6,B7,B8,B9,B10,B11 |

| P5 | B12,B13,B14,B15,B16 |

| P6 | 全部数据异或 |

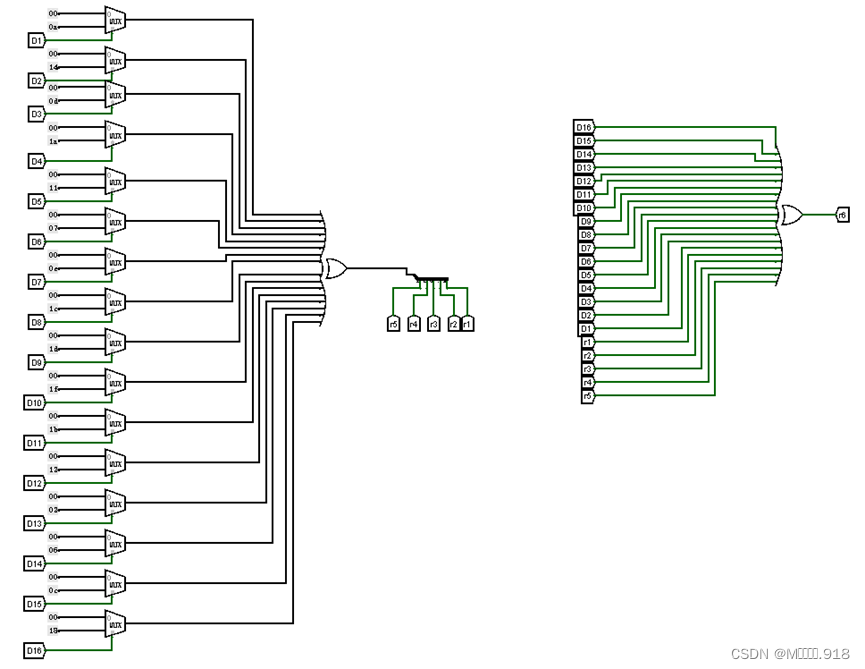

所以根据以上表格我们可以构建电路图1.14如下所示:

图1.14:海明码编码电路图

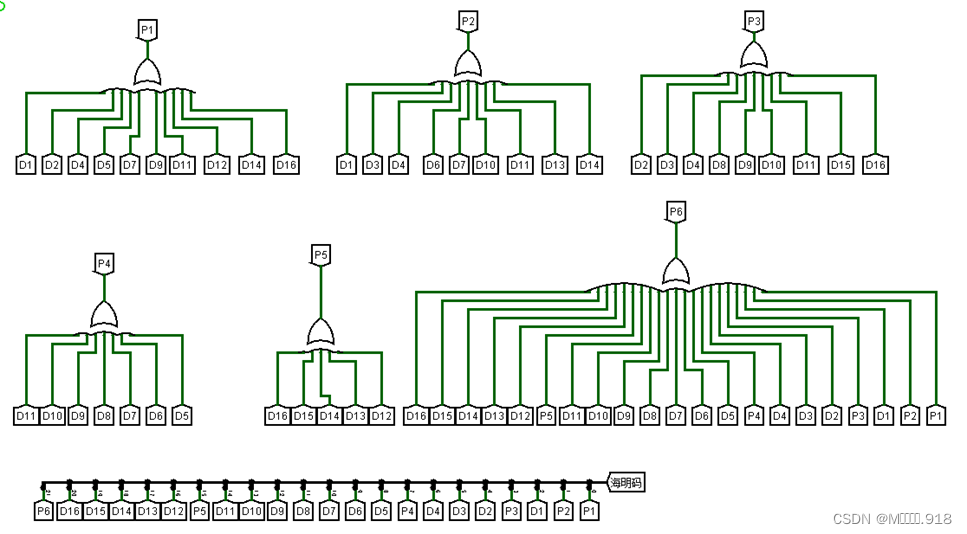

第7关:16位海明解码电路设计

检错原理:

当G5G4G3G2G1=0时,表示数据无传输错误,否则,表示出错。当发生一位数据错误时,G5G4G3G2G1所指示的数据,表示那位数据出错(例如G5G4G3G2G1=00101,则表示第5位数据出错)。若发生两位错时,G5G4G3G2G1仍不为0,由于只能纠正1位错误,故该海明编码是尽努力去纠正。

因此,增加一位总的奇偶校验位G6,进行判断是一位错,还是两位错。

①当G5G4G3G2G1=0,G6=0,表示数据无出错;

②G5G4G3G2G1 !=0,G6=1,表示发生一位数据出错;

③G5G4G3G2GG1=0,G6=1,表示该奇偶校验位出错,即发生一位出错;

④G5G4G3G2G1 !=0,G6=0,表示发生两位数据出错。

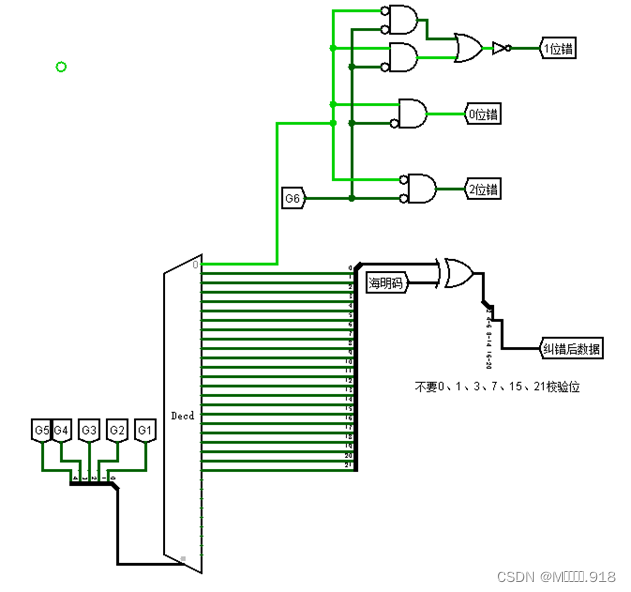

通过上一个实验我们可以通过对各个检验位和使用了检验位的数据进行异或操作拿到指错字,电路图如图1.15所示:

图1.15 指错字电路图

3.纠正数据

在纠正数据,得到原始16位数据这块设计上,可采用解码器对出错位进行输出,再与原来的数据进行异或,即可得纠正后的数据。解码器也就是你输入的数据对应输出的哪一位是1,如果是5位2进制的话就是00000,对应解码器0端口输出1,如果二进制是00101的话,对应解码器5端口输出1,所以就纠正数据只需要把对应位的错误异或过了就可以了,然后有几位错就有上面提到过的逻辑去完成电路设计就好,电路设计如下图1.16所示:

图1.16:纠正电路

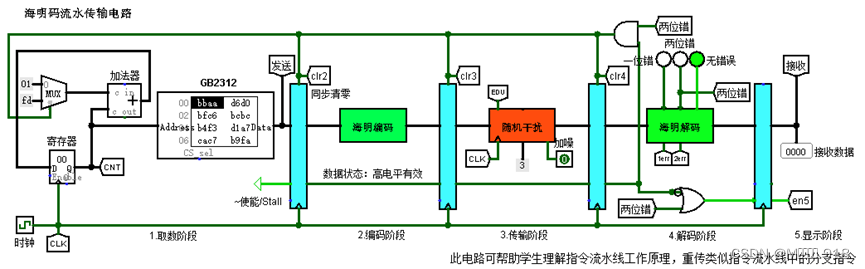

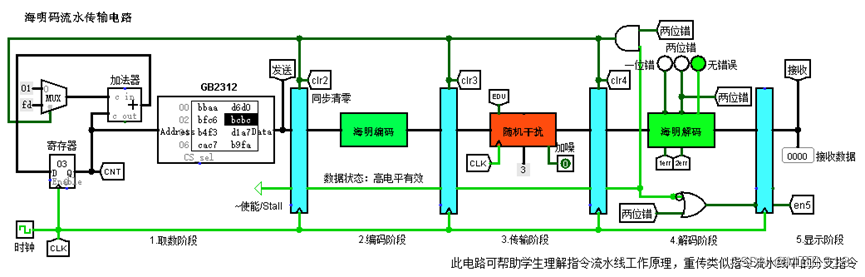

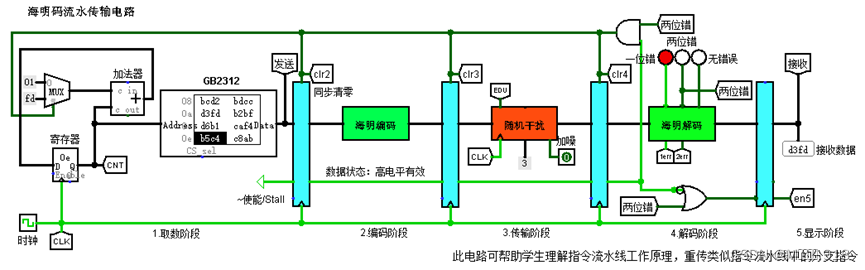

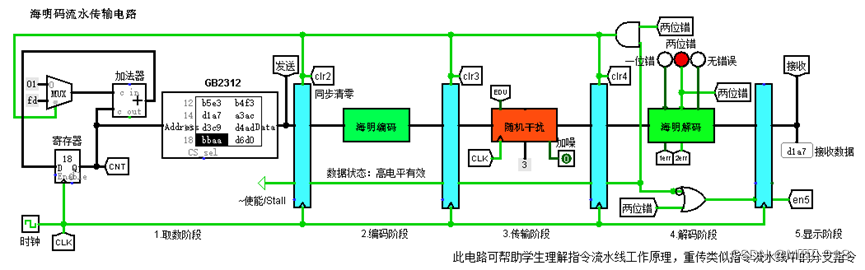

第7关:海明编码流水传输实验

实验要求我们做的是一位错就纠正两位错就退回重传,那也就是我们需要控制当报错是两位的时候把寄存器中的数需要减3,因为在整个运行的过程中当数到待了解码器找到错误的时已经走了3步了,减3的功能规定我们使用加法器去完成所以我们可以加上fdH来完成减3 的操作,然后我们还需要控制这个时候不会把结果送入接收端所以我们要把接收端的使能端设置为0,电路图如图1.17所示:

图1.17 海明编码流水传输电路图

当没有错误时候,结果如图1.18所示显示没有错误:

图1.18 没有错误情况

当出现一位错误时候,结果如图1.19所示:

图1.19 一位错误情况

当出现二位错误时候,数据选择器选择的是fdH结果如图1.20所示:

图1.20 两位错误情况

第8关:16位CRC并行编解码电路设计

一、CRC编码电路

首先我们需要了解的是CRC编码是一个上面东西,CRC编码是循环冗余校验,CRC编码基于多项式除法,通过在数据后面添加一些额外的校验位,使得整个数据(包括校验位)可以被一个预定的生成多项式整除。

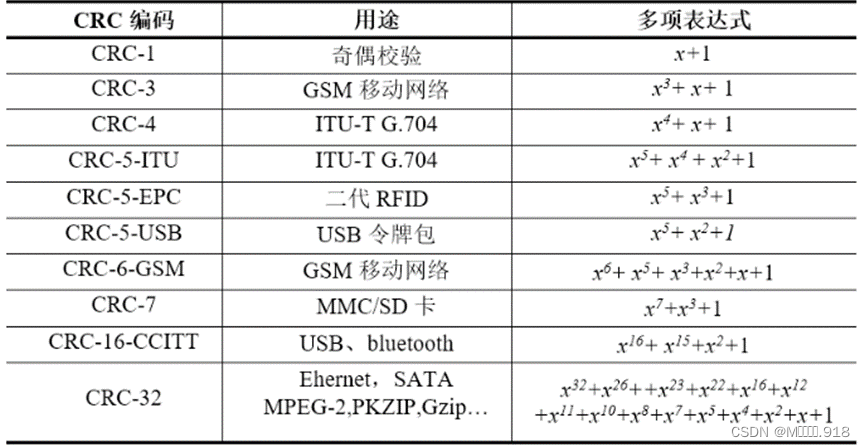

第一步:选取生成多项式,常用的CRC生成如图1.21所示,这里我选择的是G(x)=100101

图1.21 CRC常用生成式

第二步:由于本实验要采取的是并行编码,所以可以得到如下的公式,公式可以让我们知道,可先对该16位数据按位与多项式进行模2除运算,再根据其实际数据进行异或操作。

第三步:我们现在就需要通过选择器,当某一位的数据为1的时候,就选择它与多项式进行模2除运算的结果,否则就选择0,所以每一位进行模2除运算(手算就好)的结果如下所示:

1000000 0a

10000000 14

100000000 0d

1000000000 1a

10000000000 11

100000000000 07

1000000000000 0e

10000000000000 1c

100000000000000 1d

1000000000000000 1f

10000000000000000 1b

100000000000000000 13

1000000000000000000 03

10000000000000000000 06

100000000000000000000 0c

1000000000000000000000 18

第四步:设计电路图,电路图如图1.22所示:

图1.22 CRC编码电路图

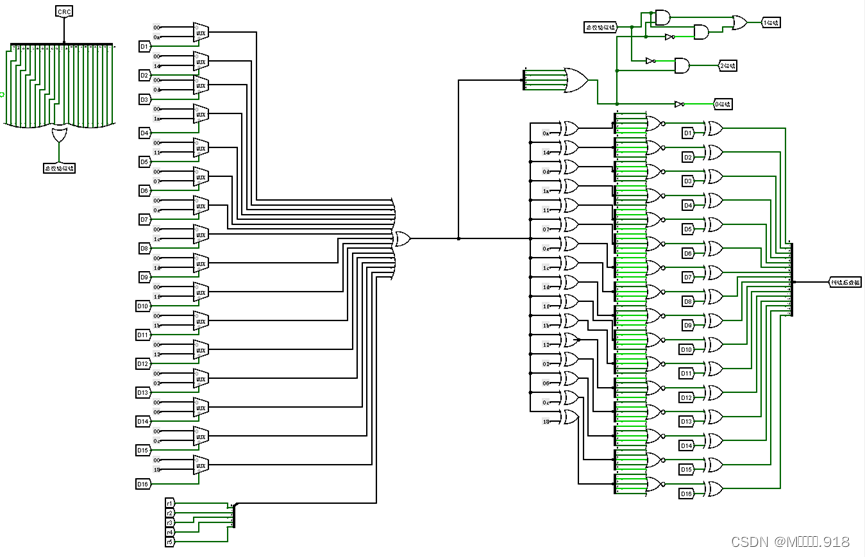

二、CRC解码电路

检错原理

1、接收方在接受到CRC编码后,将该编码与多项式进行模2除运算,得到余数r,再根据q(假设q为总的奇偶检验位,将所有数据进行异或可得)的值进行判断数据是否产生错误,及产生错误后是一位错还是两位错。其检查原理同海明码的检错原理相同。

有以下情况:

①当r=0,q=0,表示数据无出错;

②r!=0,q=1,表示发生一位数据出错;

③r=0,q=1,表示该奇偶校验位出错,即发生一位出错;

④r!=0,q=0,表示发生两位数据出错。

2、求余数时,可参照设计CRC编码时求余数的方法,也就是把各位的模二运算的结果和余数做异或运算得到最终的余数。

电路图如图1.24所示:

图1.24 CRC解码

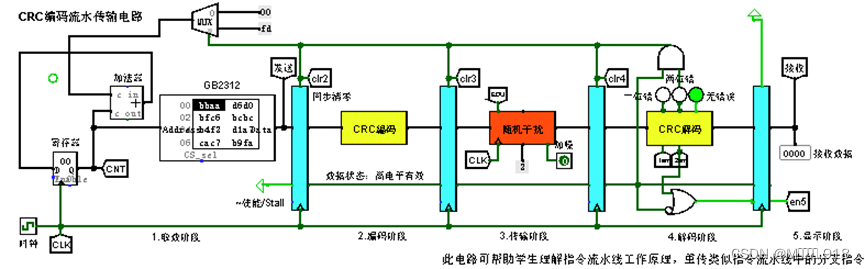

第9关:CRC编码流水传输实验

电路图如图1.25所示:

图1.25 CRC编码流水传输电路图

cric文件的下载地址如下:有需要的自行下载噢!🌹🌹🌹🌹

858

858

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?