双端口RAM

优化多核CPU访问一根内存条的速度

需要有两组完全独立的数据线,地址线,控制线。cpu,RAM中也要有更复杂的控制电路。

两CPU读写一主存必然存在一下四种情况:

1.两CPU同时读写不同的地质单元。🆗

2.两CPU同时读取同一地质单元数据。🆗

3.两CPU同时对同一地址单元写数据。❌

4.两CPU对同一地址单元,一个读,一个写。❌

这里3和4就需要引入锁的机制了,保证同一时间,同一地址单元只能有一个cpu进行写数据,并且写的时候不能读。

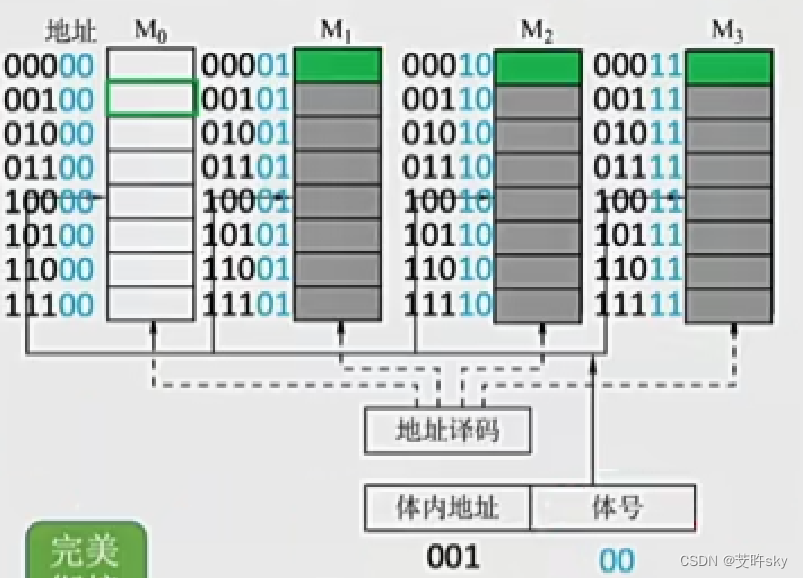

多体并行存储器

引入此方法的原因:

当只有一个存储体时,cpu要连续的读取这个存储体中的存储单元中的信息,但是存储体的存储周期=存取时间+恢复时间,而且这个恢复时间比存取时间还要长很多,就导致了如果只有单个存储体,cpu要连续读取时,就需要浪费很长的时间去用来恢复。本来cpu就很快,和主存的速度不匹配。所以就需要引出减少恢复时间的方法,来解决这个问题。

这里还分为了高位交叉的多体存储器和低位交叉的多体存储器,两者的作用使不同的.

高位交叉:相当于单纯的扩容。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7万+

7万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?