DRAM,dynamic random access memory,即动态RAM,用于主存。

SRAM,static random access memory,即静态RAM,用于Cache。

此为高频考点:DRAM和SRAM的对比。

之前文章存储器芯片原理中就是以DRAM来学习的,可以看看之前的文章详细了解DRAM芯片原理。

两芯片的核心区别就是存储元不同。

DRAM芯片

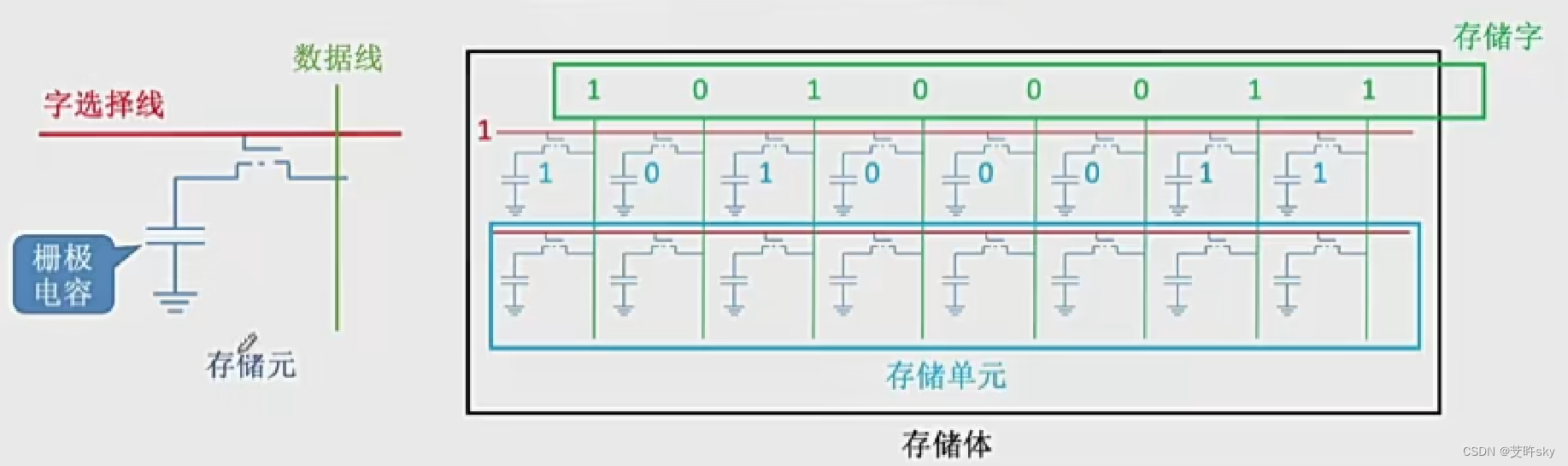

使用栅极电容来存储信息

读出1:MOS管接通,电容放电,数据线上产生电流

读出0:MOS管接通后,数据线上无电流

破坏性读出特点

说到这里,你应该也想到了一点,用栅极电容存储电荷,接通电路后看是否有电流来确定0和1,这样的读取数据操作是一次性的,存一次,读一次,存储元中存储的数据便被破坏了。所以对于DRAM读出后应有重写操作。

因此DRAM读写速度相对SRAM较慢。

但是制造成本更低,集成度更高,功耗也低。

DRAM刷新

因为使用电容储存电荷,但是电容中的电荷会流失,只能维持 2ms 即2ms后存储的信息就会消失。所以2ms之内为了保存数据,就要给电容充一次电。

这里就会引出一个新的概念:

行地址译码器和列地址译码器

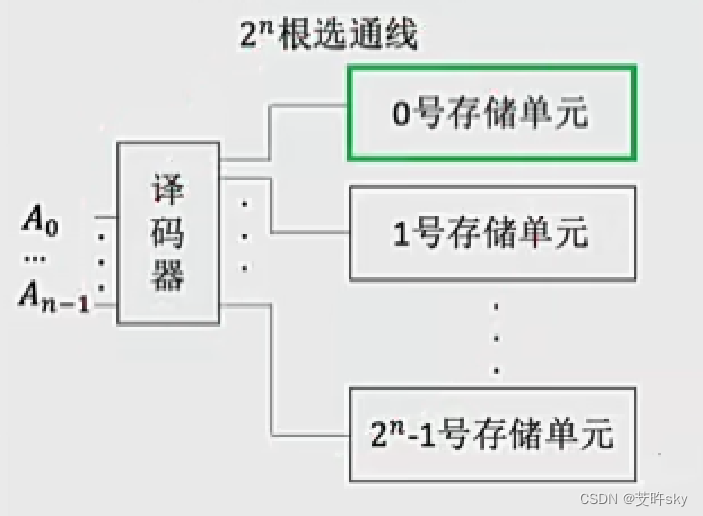

之前的学习中DRAM逻辑图就是直接一个译码器连接着一排排的存储单元。

但是你有没有想过一个问题,当存储单元很多,但是译码器就那么大,译码器上就需要连出很多条线路来连接一个个的存储单元。

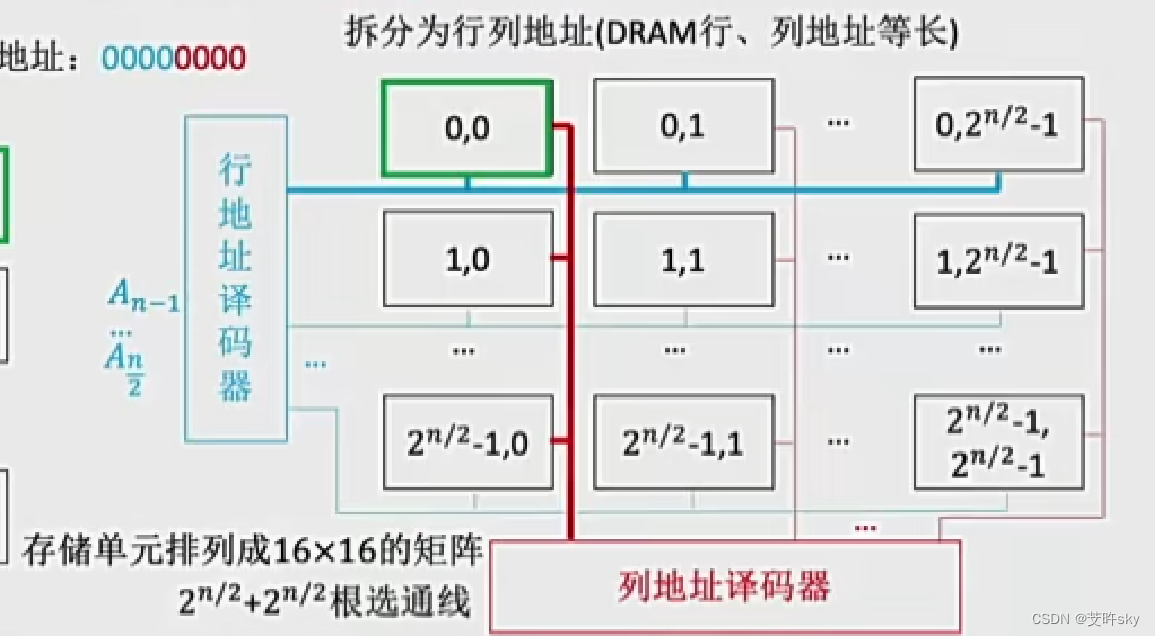

举个例子:一个几毫米的译码器上连出几万条线路,这明显不现实。所以就引出了行地址译码器和列地址译码器。将原本一维排解的存储单元改为二维排列。就可以减少选通线的数量。

将原本的地址查分为两部分,分别对应行和列,通过行列地址译码器,译码出目标存储单元所在的行和列,行列皆连通时就是要找的存储单元。

例如:

8位地址:如果是原本得到一维排列,就需要2^8=256根选通线,而换成2维排列,并拆分8位地址为4+4,那么只需用2^4+2^4=32根选通线。大幅度减少了选通线的数量。

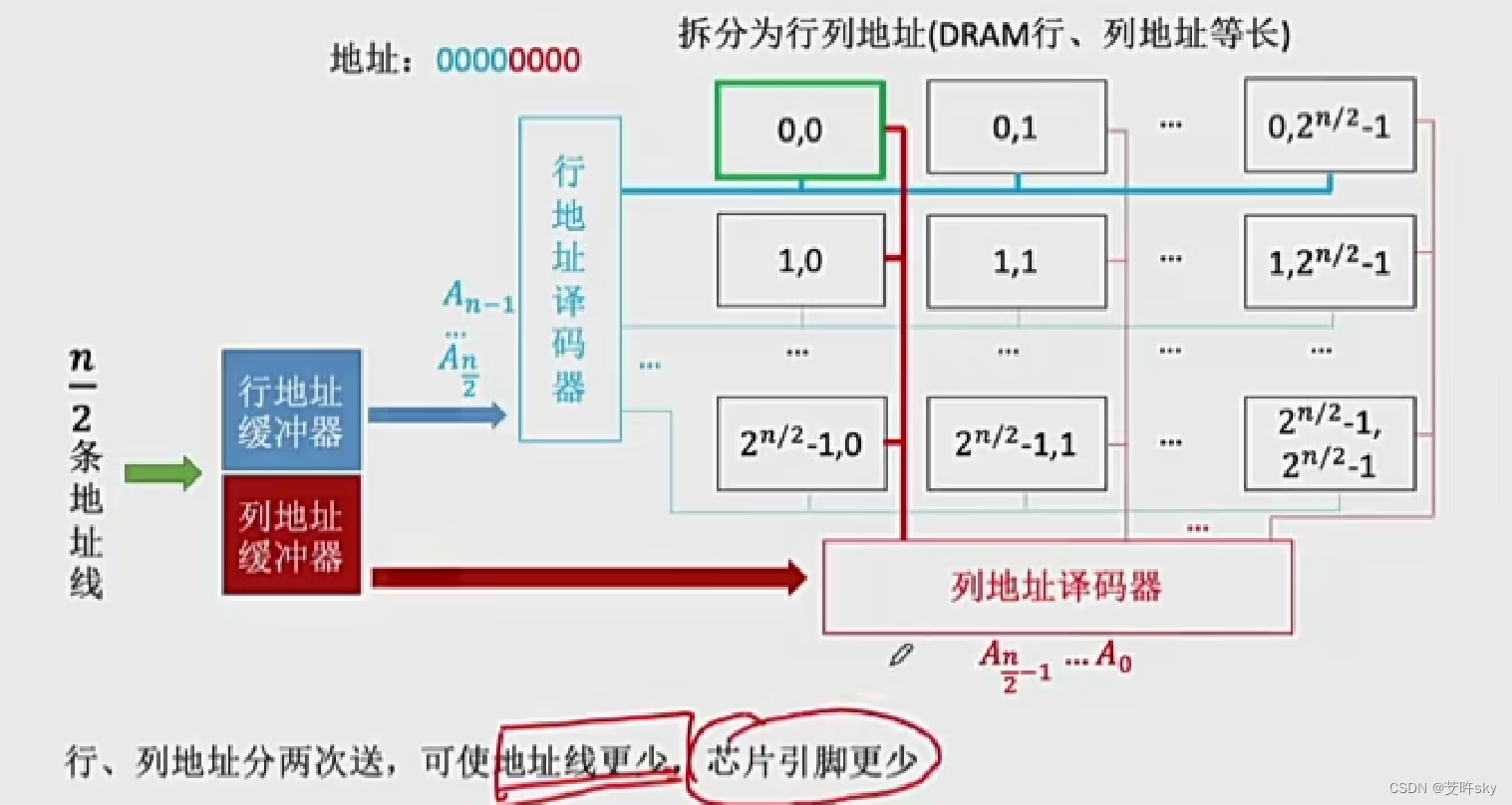

DRAM地址线复用

当然上述说的DRAM的破坏性读写明显是会被技术进步而淘汰的,现在的主存通常采用SDRAM芯片。

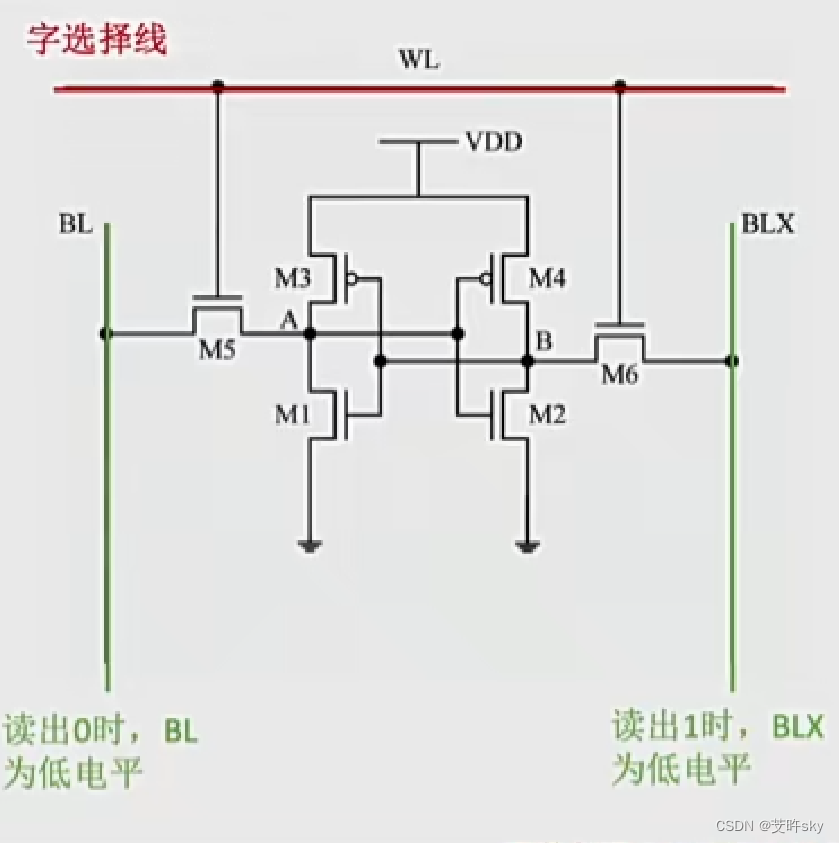

SRAM芯片

使用双稳态触发器存储信息

读取1:A高B低

读取0:A低B高

既然这个叫做双稳态触发器,那么也能推断出,SRAM是非破坏性读出,读出数据后,不会破坏存储的数据,无需重写。

因此SRAM读写速度更快。

但是双稳态触发器由6个MOS管构成,显然制造成本更大,而且集成度较低,功耗大。

在下图中总结两者对比区别:

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?