湖虫学院 2023—2024 学年度第二学期

《计算机组成原理》 期中考试参考答案

- 选择题(共 10 小题,每题 2 分,共计 20 分)

1.冯诺依曼机的重要特点是( C )

- 5 大部件组成 B.指令和数据同等地位存于存储器

C.存储程序思想 D.以运算器为中心

2.计算机硬件系统包括( A )

A.主机与外设 B.运算器、控制器、存储器

C.主机和实用程序 D.输入设备和输出设备

3.计算机系统中采用补码预算的目的是为了( C )

A.与手工运算方式一致 B.提高运算速度

C.简化计算机的设计 D.提高运算的精度

4.某计算机字长 32 位,其存储容量为 4MB,若按字编址,它的寻址范围是( A )

A.0-1M B.0-2M

C.0-3M D.0-4M

5.计算机的存储系统是指( D )

A.RAM B.ROM

C.主存储器 D.Cache、主存储器、辅存储器

6.下列因素中,与Cache的命中率无关的是( A )

A.主存的存取时间 B.块的大小

C.Cache的组织方式 D.Cache的容量

7.主存和CPU之间增加高速缓冲存储器的目的是( A )

A.解决CPU和主存之间的速度不匹配问题 B.扩大主存容量

C.既扩大主存容量,又提高主存速度 D.扩大存储器的寻址空间

8.CACHE采用的存储器是( A )

A.SRAM B.ROM

C.EPROM D.DRAM

9.某字长为8位的计算机中,已知整型变量X,Y的机器数分别为[x]补=1111 0100,[Y]补=1011 0000.若整型变量Z=2*X+y/2,则Z的机器数为( A )

A.11000000 B.00100010

C.10101010 D.溢出

10.微型计算机的发展以( B )技术为标志。

A.操作系统 B.微处理器

C.磁盘 D.软件

- 填空题(共 10 小题,每题 2 分,共计 20 分)(每小题错一个扣1分!)

- 计算机系统的软件可分为( 系统软件 )和( 应用软件 )。

- MIPS是用来表示计算机( 运算速度 )的单位,其含义是( 每秒执行多少百万条数据 )。

- 存储程序按( 地址 )顺序执行,这是( 冯诺依曼 )型计算机的工作原理。

- 在16位微机系统中,一个存储字占用两个连续的8位字节单元,字的低8位存放在( 低地址单元 ),高8位存放在( 高地址单元 )。

- Cache是一种( 高速缓冲 )存储器,是为了解决CPU和主存之间( 速度不匹配 )而采用的一项重要的硬件技术。

- 主存与Cache的地址映射有全相联、( 直接相联 )和( 组相联 )方式。

- 存储系统的CACHE—主存和主存—辅存都用到了( 局部性 )原理。

- 堆栈是一种特殊的( 数据 )寻址方式,它采用( 先进后出 )原理。

- 一台计算机中( 所有机器指令 )的集合,称为这台计算机的指令系统;指令格式通常由( 操作码 )字段和地址码字段组成。

- 指令字长度有( 单字长指令 ),( 半字长指令 ),( 双字长指令 )。

- 简答题(共 5 小题,每题 5 分,共计 25 分)

- 冯诺依曼计算机体系结构的基本思想是什么?按此思想设计的计算机硬件系统应由那些部件组成?(此题共两小问,每错一个扣3分!)

答案:

冯诺依曼计算机体系的基本思想是存储程序,也就是将用指令序列描述的解题程序与原始数据一起存储到计算机中。计算机只要一启动,就能自动地取出一条条指令并加以执行,直至程序执行完毕,得到计算结果为止。

按此思想设计的计算机硬件系统包含运算器、控制器、存储器、输入设备和输出设备五个基本部件。

- 解释主机、主存、存储字长、机器字长、指令字长。

(每个名词解释1分!)

答案:

将CPU和主存合在一起称为主机,主机内数据直接传送,不需要使用接口转换;主存是存放正在执行的程序和数据;存储字长是指主存一个存储单元可存储的二进制位数;机器字长是CPU一次可以处理的二进制位数;指令字长是机器语言指令操作码和地址码的总位数。

- 提高访存速度可采取哪些措施?(共三种方法,少写一种扣2分!)

答案:

(1)采用高速器件;

(2)采用CACHE;

(3)调整主存结构(单体多字、低位多体交叉、多端口存储器)。

- 说明SRAM的组成结构,与SRAM相比,DRAM在电路组成上有什么不同?

(如果回答出SRAM是静态随机存储器,DRAM是动态随机存储器 得2分;回答出SRAM由6个MOS管组成 得2分;回答出DRAM需要刷新得1分)

答案:SRAM是静态随机存储器,其基本单元电路是由6个MOS管组成的触发器基本电路,3个MOS管受行地址选择控制,3个MOS管受列地址选择控制,电路有两种稳定状态,分别来记录0和1;DRAM是动态随机存储器,常用的是单管式;靠电容存储电荷的原理来寄存信息,若电容上有足够多的电荷表示存1,无电荷表示存0.但是电容不稳定,只能维持1-2MS,为此,必须在2MS内对其所有存储单元恢复一次原状态,即刷新。

- 某机器指令码长度16位,地址码长度都为6位,包含单地址指令,双地址指令和零地址指令,请问单地址指令最多能有多少条,此时双地址指令和零地址指令各位多少条?(此题共三小问,少回答一问扣2分!)

答案:

单地址指令最多能有(24-1)*2的6次方-1=959条,

此时双地址指令只有1条,

零地址指令最多可有2的6次方=64条。

- 计算题(共 3 小题,前两题每题 6 分,第三题 8 分,共计 20 分)

1、两台计算机A和B采用不同主频的CPU,而片内逻辑电路相同。

(1)若A机的主频为8MHz,B机为12MHz,则两机的CPU时钟周期各是多少?

(2)如果A机的平均指令执行速度为0.4MIPS,那个A机的平均指令执行时间是多少?

(3)B机的平均指令执行速度MIPS是多少?

(共3小问,每小问2分!)

答案:

(1)A机的CPU时钟周期=1/主频=1/8=0.125us,B机的CPU时钟周期=1/主频=1/12=0.083us

(2)这里指定MIPS=0.4,即每秒执行0.4百万条指令,所以平均指令执行时间为1/MIPS=1/0.4=2.5us

(3)A机的MIPS=0.4,所以其CPI=主频/MIPS=8/0.4=20,由于A机和B机的片内逻辑电路完全相同,所以两者的CPI也相同,即B机的CPI=20。因此B机的MIPS=主频/CPI=12/20=0.6MIPS

2.求下列各种码对应的真值 (错一个扣1分!)

[x]原 = 10001101 [x]原 = 00001101

[x]反 = 10001101 [x]反 = 00001101

[x]补 = 10001101 [x]补 = 00001101

[x]移 = 10001101 [x]移 = 00001101

答案:

[x]原 = -13 [x]原 = 13

[x]反 = -114 [x]反 = 13

[x]补 = -115 [x]补 = 13

[x]移 = 13 [x]移 = -115

- CPU执行一段程序时,cache完成存取的次数为5000次,主存完成存取的次数为200次。已知cache存取周期为40ns,主存存取周期为160ns。求:(1)Cache 命中率H;(2)Cache/主存系统的访问效率e;(3)平均访问时间Ta。

(共3小问,错一个扣3分!)

答案:

① 命中率 H = Nc/(Nc+Nm) = 5000/(5000+2000)=5000/5200=0.96

② 主存慢于cache的倍率 R = Tm/Tc=160ns/40ns=4

访问效率:e= 1/[r+(1-r)H]=1/[4+(1-4)×0.96]=89.3℅

③ 平均访问时间 Ta=Tc/e=40/0.893=45ns

- 设计题(共1小题,共计 15 分)

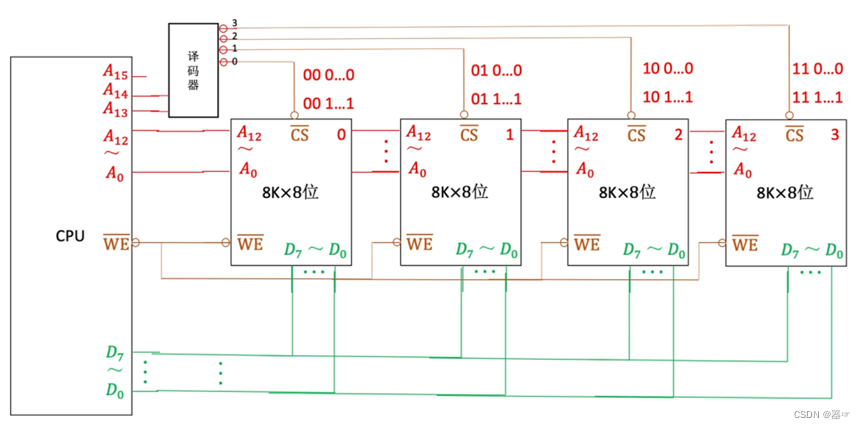

1.某机器字长为8位,试用如下所给芯片设计一个存储器来增加主存的存储字数,(芯片类型为:8K×8位)。

(参考答案是4个芯片,如果画出2个芯片及译码器则可以得15分!)

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?