计组期末复习

🥗简答+填空

1、计算机系统中采用补码预算的目的为了简化计算机的设计

2、程序计数器PC在控制器中

3、计算机主频的周期是指时钟周期

4、I/O接口中数据缓冲器的作用是解决CPU与外设之间的速度不匹配问题

5、直接转移指令的功能是将指令中的地址代码送入PC

6、计算机系统的软件可分为系统软件和应用软件

7、微程序设计技术是利用软件方法设计硬件的一门技术、特点是规整性、可维护性、灵活性

8、存储系统的 Cache一主存和主存一辅存都用到了局部性原理

9、完整的指令周期包括取址周期、间址周期、执行周期和中断周期

10、DMA技术的出现使得外围设备可通过DMA控制器直接访问内存

解释时钟周期、 机器周期、指令周期、主机、主存、存储字长、机器字长、指令字长

- 时钟周期,也称为节拍脉冲,是CPU最小的时间单位

- 机器周期,又称CPU周期,是CPU访问一次内存所花的时间较长,因此用从内存读取一条指令字的最短时间来定义

- 指令周期是CPU从主存中取出并执行一条指令的时间

- 主机通常指的是计算机系统的中央处理单元(CPU)及其相关的控制电路,它负责执行程序指令和处理数据

- 主存,也称为主存储器,是计算机系统中用于暂时存储数据和指令的部件

- 存储字长是指一个存储单元中的二进制代码位数,通常与MDR(存储器数据寄存器)的位数相同

- 机器字长是指CPU进行一次整数运算时能处理的二进制数据的位数

- 指令字长是指一条指令的总长度

具体期中考试类似解答🌈

下面给出期中考试部分解答:

总线仲裁是指在多个主设备同时竞争总线控制权时,通过某种方式选择一个主设备优先获得总线控制权的过程

集中式仲裁的方法:1、链式查询方式 2、计数器定时查询方式 3、独立请求方式

提高访存速度可采取哪些措施?

- 采用高速器件:选择存取周期短的芯片,这样可以直接提高存储器的速度。

- 采用层次结构Cache:Cache位于存储器和CPU之间,如果CPU需要的数据已经存在于Cache中,那么访问速度将大大提高。

- 调整主存结构:例如,采用单体多字系统,在一个存取周期内可以取出多个存储字,这样可以增加存储器的带宽。

- 使用大容量内存:大容量内存可以更好地容纳数据,减少内存碎片,从而提高访存速度。

- 使用虚拟内存:虚拟内存可以将物理内存与硬盘空间结合起来,模拟更大的内存容量,从而提高访存速度。

- 优化内存管理:合理的内存管理可以有效地提高访存速度,例如通过减少内存碎片和优化内存分配策略。

可写红色字体及下划线

❤️❍🧡❍💛❍💚❍💙❍💜

简述CPU访问IO端口的过程。

- CPU通过地址总线发送I/O端口的地址。

- 系统中的译码器接收到地址信号后,确定具体的I/O端口地址。

- CPU通过数据总线将数据发送到选定的I/O端口。

- I/O设备接收到数据后,根据指令进行相应的操作。

老师说必须要有译码器、数据总线、地址总线

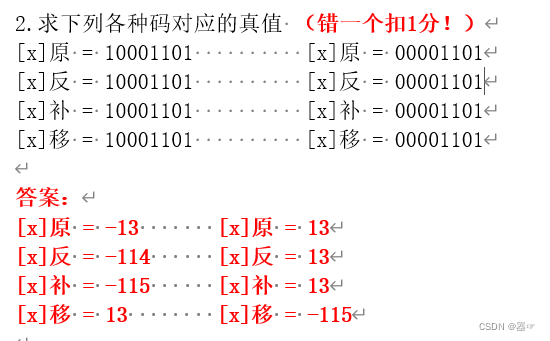

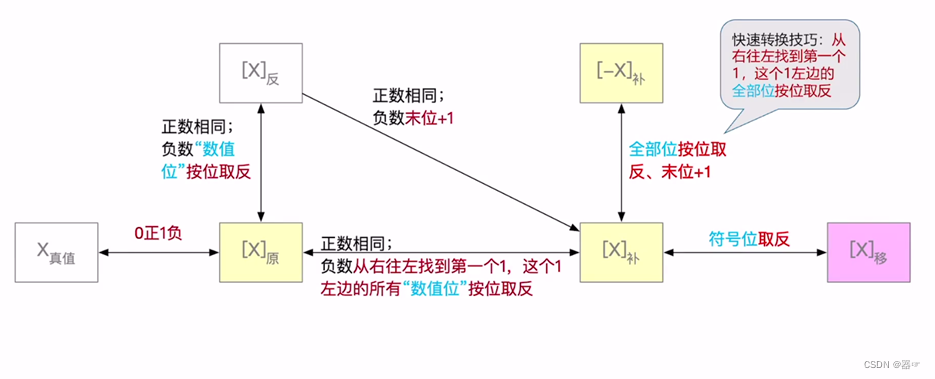

求下列各种码对应的真值

这个题不是具体的答案,所以这题给具体的方法,下面附上其中部分题和解题方法

ɢᵒᵒᵈ ɴⁱᵍʰᵗ ✩🌕ིྀ

近期生活碎片已发送 ´͈ ᵕ `͈

大题🌈ℍ𝕒𝕡𝕡𝕪𝕨𝕖𝕖𝕜

具某同学(虎同学)透露大题有设计题、计算题、指令流、还有0.4和0.6的。猜出大半,可信度0.9,另外0.1找虎同学要

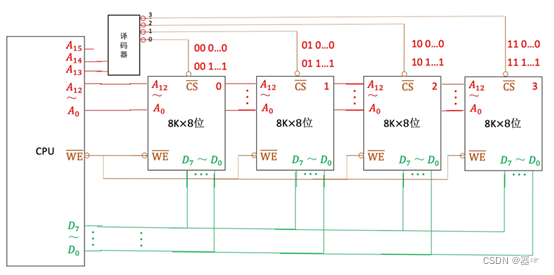

设计题

1.某机器字长为8位,试用如下所给芯片设计一个存储器来增加主存的存储字数,(芯片类型为:8K×8位)。

(参考答案是4个芯片,如果画出2个芯片及译码器则可以得15分!)

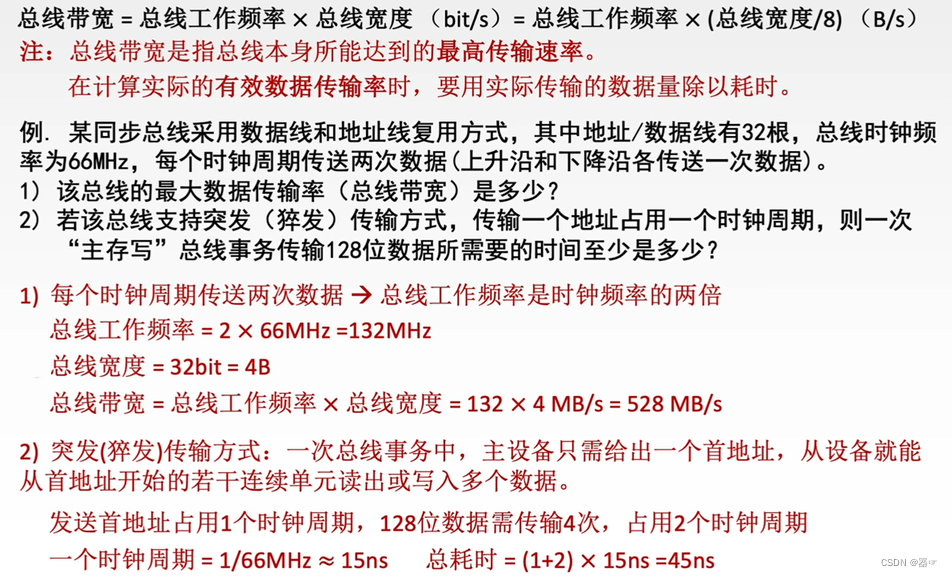

计算题

指令流

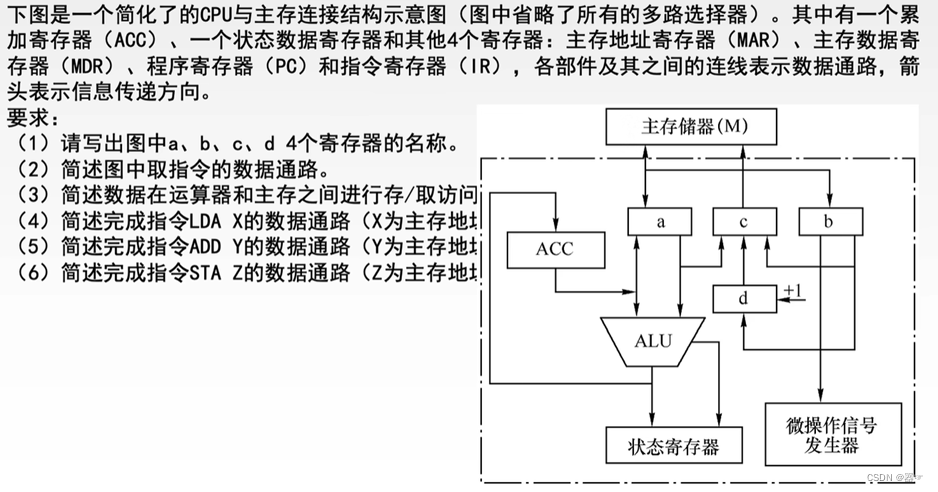

解答:

(1)d能自动“+1”,是PC

PC内容是地址,送MAR,故c是MAR

b与微操作信号发生器相连,是IR

与主存相连的寄存器是MAR和MDR,c是MAR,则a是MDR(2)(PC)→ MAR

M(MAR)→ MDR

(MDR)→IR

(3)存/取的数据放到ACC中

设数据地址已放入MAR

取:

M(MAR)→MDR (MDR)→ALU→ ACC

存:

(ACC)→ MDR (MDR)→ M(MAR)

(4)X→MAR

M(MAR) → MDR (MDR)→ALU →ACC

(5)Y →MAR

M(MAR) → MDR

(MDR)→ ALU,(ACC) →ALU ALU→ ACC

(6)Z→MAR

(ACC)→ MDR (MDR)→>M(MAR)

0.4和0.6附上期中考试部分题

1、两台计算机A和B采用不同主频的CPU,而片内逻辑电路相同。

(1)若A机的主频为8MHz,B机为12MHz,则两机的CPU时钟周期各是多少?

(2)如果A机的平均指令执行速度为0.4MIPS,那个A机的平均指令执行时间是多少?

(3)B机的平均指令执行速度MIPS是多少?

(共3小问,每小问2分!)

答案:

(1)A机的CPU时钟周期=1/主频=1/8=0.125us,B机的CPU时钟周期=1/主频=1/12=0.083us

(2)这里指定MIPS=0.4,即每秒执行0.4百万条指令,所以平均指令执行时间为1/MIPS=1/0.4=2.5us

(3)A机的MIPS=0.4,所以其CPI=主频/MIPS=8/0.4=20,由于A机和B机的片内逻辑电路完全相同,所以两者的CPI也相同,即B机的CPI=20。因此B机的MIPS=主频/CPI=12/20=0.6MIPS

冲同学提醒另加题

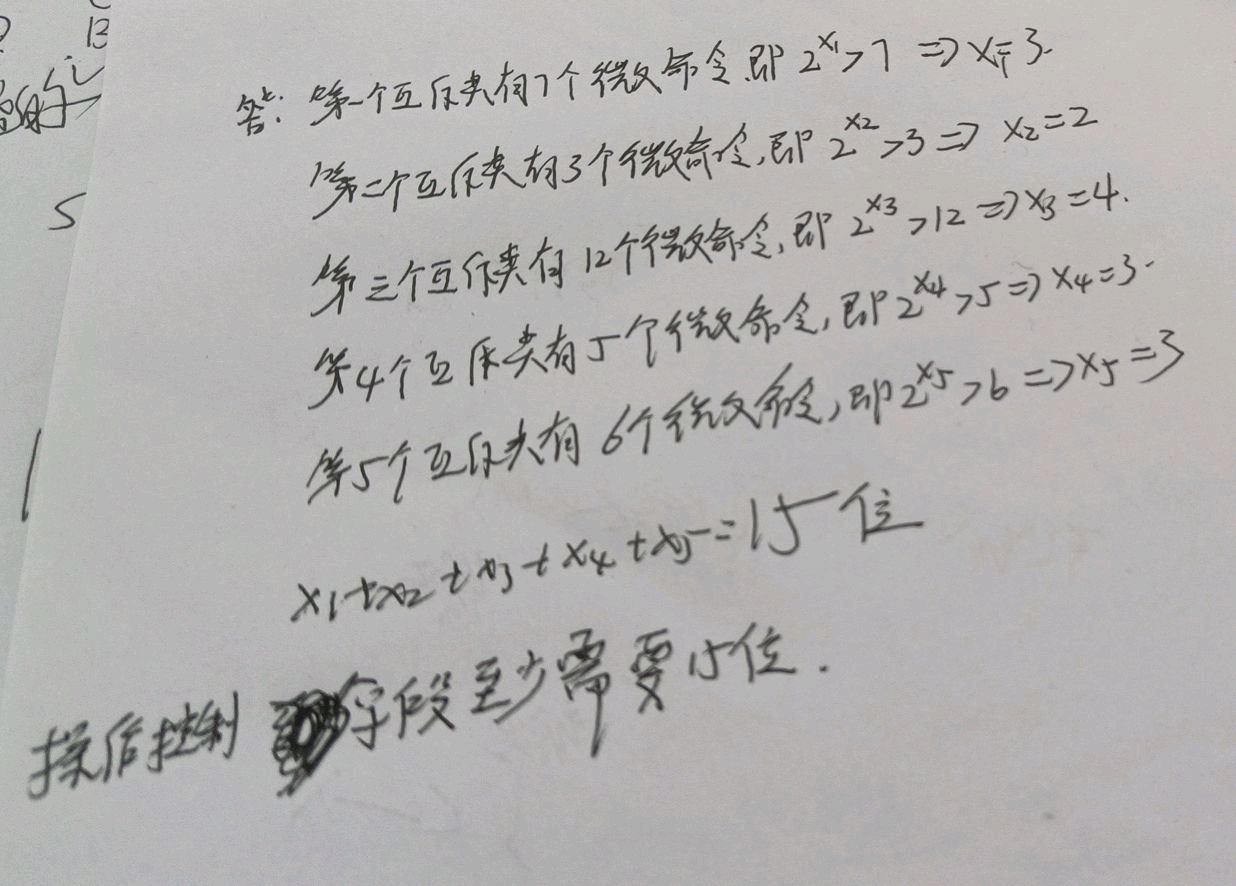

某计算机的控制器采用微程序控制方式,微指令中的操作控制字段采用字段直接编码,共有33个微命令,构成5个互斥类,分别包含:7、3、12、5、6个微命令,则操作控制字段至少有多少位?

上面的内容可能有遗漏,需要反复观看,重复记忆,下面给出期中试卷及答案

期中卷子点击打开

4922

4922

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?