实验一 简单电路

一、实验目的

- 熟悉和掌握Quartus II集成开发环境及使用方法;

- 掌握基于图编辑器的顶层实体设计;

- 掌握从设计输入到硬件配置的完整设计流程;

- 掌握Cyclone V实验箱组成;

- 熟悉使用VHDL硬件描述语言。

二、实验环境

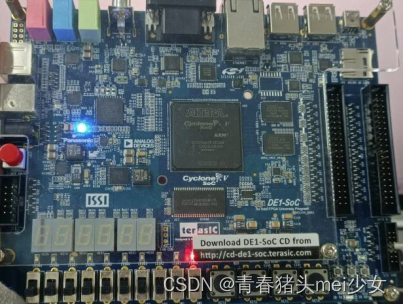

本实验的实验环境为Altera Quartus II 软件和Altera Cyclone V Starter 工具箱。实验平台要点如下:

- Cyclone V是Altera FPGAs家族的一类,它面向低功耗应用。Cyclone V GX 5CGXFC5C6F27C7N 芯片有不同的转换器,按钮,LED灯,七段显示器,HDMI接口,SD卡读卡器以及其他链接等。Cyclone V GX 5CGXFC5C6F27C7N是Starter工具箱的重要组件。

- 测试台包含在测试设备(DUT)和用于仿真的模拟输入。这可以用于测试功能行为和计时行为。我们还可以采用测试台来分配Starter工具箱上相关信号的引脚名称,用force文件来包含仿真模拟输入。

三、实验内容

采用图编辑器设计实体:

在此过程中,你可以将各组件放在一张纸上,并将它们与虚拟电线连接起来以创建一个简单的数字电路。你可以仿真此电路来验证其行为是否正确。然后你可以在Starter工具箱上给Cyclone V FPGA板编程,最后演示电路的正确操作。

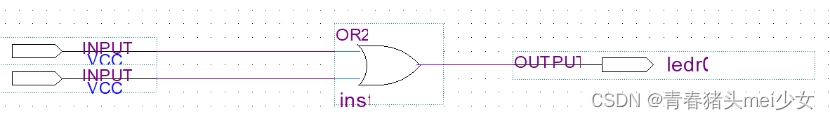

- 完成以下功能:ledr0 = sw0 OR sw1

- 创建一个工程

选择File>New Project Wizard….创建工程,然后选择Next> 。

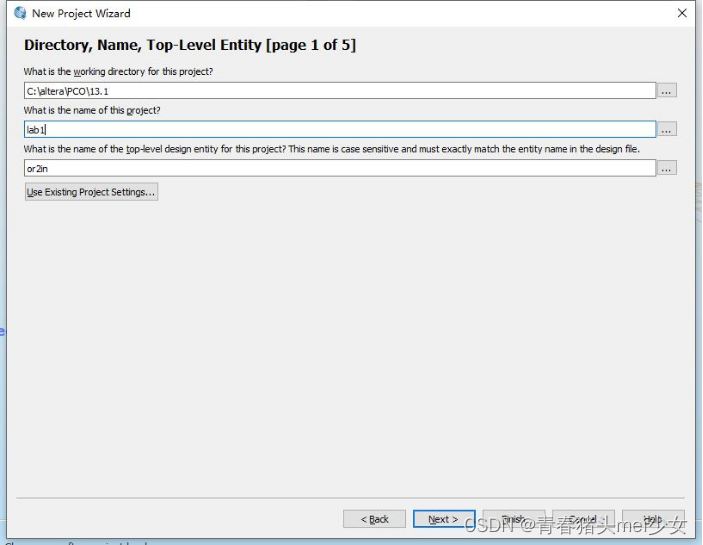

这个工程的工作目录是什么? C:\altera\PCO\lab1(注意:只能是英文)

这个工程的名称是什么?lab1

这个工程的顶层实体的名称是什么?or2in

-

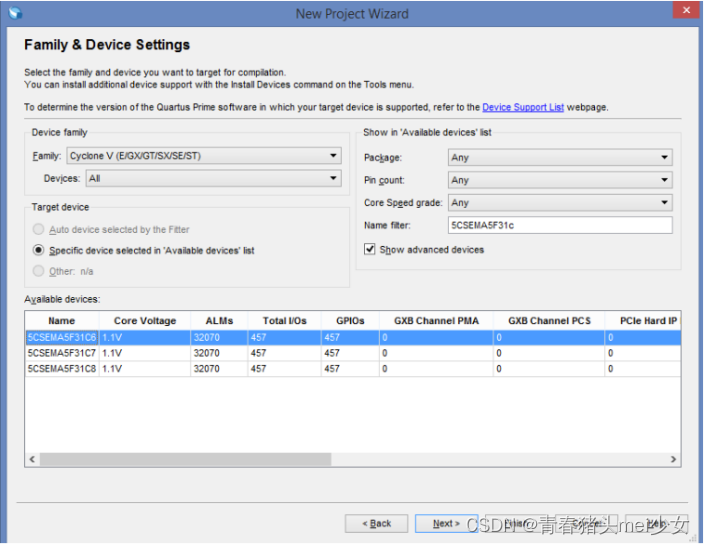

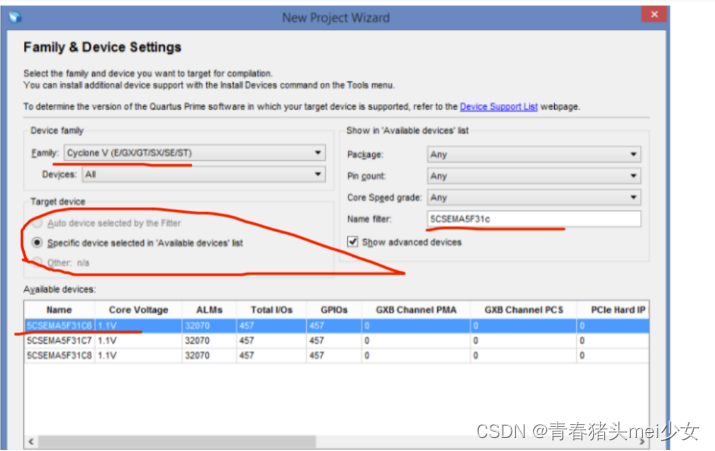

- 双击Next进入设备选择界面。在左边组件的组合框中,选择Cyclone V,并在Name filter框的右侧填写你的FPGA板的正确设备名,即5CSEMA5F31C6,再点击Next。

-

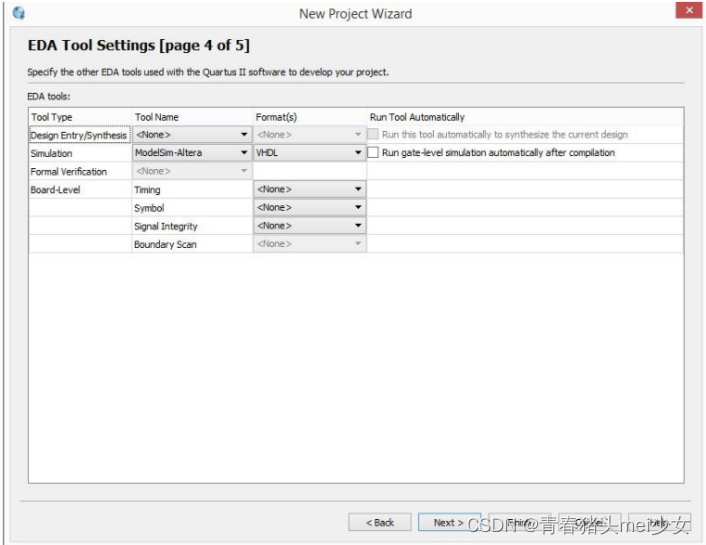

- 指定你要使用的ModelSim仿真器。在下一个窗口中,仿真器可以读取Modelsim-Altera和VHDL。

- 进行设计

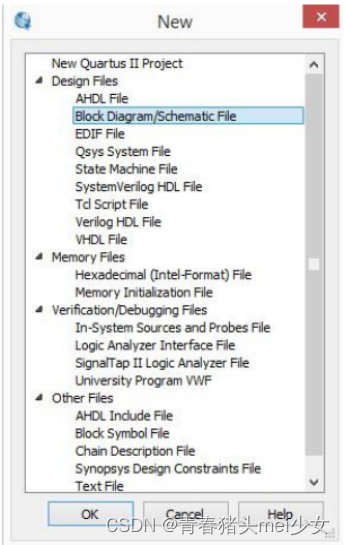

- 选择File>New>Block Diagram/Schematic File来创建一个新的Block Diagram/Schematic文件。

-

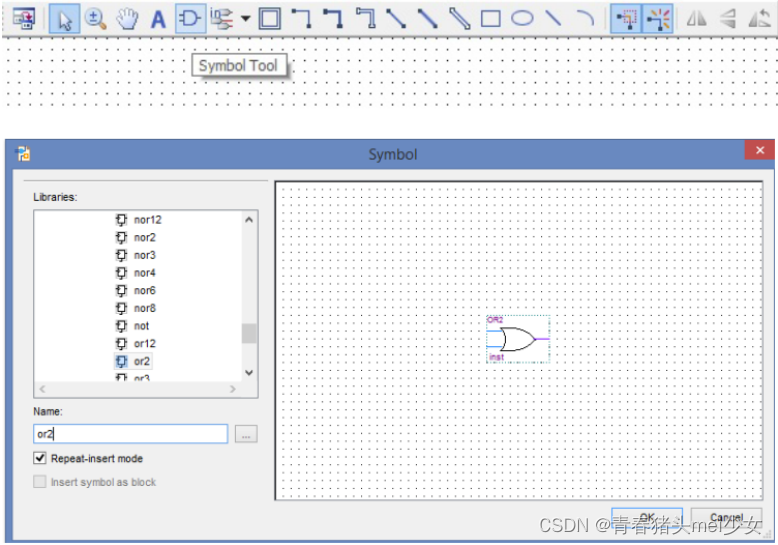

- 点击工作区左边的工具条上的添加符号图标添加一个新的门。你也可以在绘图区上通过双击来添加。在Libraries:下的列表框中,点击C:/altera/quartus/libraries/左边的扩展符号(+)来展示可用库。先点开原始库,再点开逻辑库。

-

- 在逻辑库列表中选择or2符号,即可查看到2输入OR门,点击OK。现在可以放置你的or2门。在工作区中点击某处来为你示意图中的or2门创建一个实例。

- 为输入输出引脚命名

- 再次选择添加符号图标。打开primitives/pin库选择输出符号并点击OK。将输出引脚放置到or2门的正确位置上。断开输出引脚的连接。重复上述步骤添加另外两个引脚。

- 为了在or2符号上连接引脚符号,将鼠标放置到符号中某条电线的末尾,当光标变为+符号时,表明在光标的右下角有一个“+”。当光标显示为“+”时,点击并拖拽到你想连接的电线上。当你连接一条电线后,将会在电线的末尾显示一个小框。将光标放到小框中并释放鼠标按钮。采用这种方式,依次连接逻辑符号中的各个输入输出引脚。

- 为了给引脚命名,右键点击引脚并选择Properties。此时出现一个标记为Pin name(s):的文本框,你可以在此处输入引脚的名称。输入引脚名称后,点击OK。

- 当switch0,switch1某个或者都处于on位置时,你可以创建一个电路用于打开第一个红色发光二极管ledr0。因此,将两个输入引脚的名称分别设置为sw0和sw1,输出引脚设置为ledr0。至此,你已完成了示意图的创建,将其保存为or2in.bdf。下一步是将原理图中的引脚分配给FPGA上的对应物理引脚。

- 编译设计

- 在编译之前,通过以下步骤“File→Create/update→Create HDL Design File from Current File”将bdf文件转换为VHDL文件。然后通过“Project→Add/remove files in project”来删除列表中的or2in.bdf文件,并添加生成的or2in.vhd文件。

- 保存你的设计,然后使用Processing>Start Compilation命令将其编译。编译过程会花一些时间。你可以在左侧的状态窗口观察编译过程。当编译结束时会弹出对话框。此时可以无视一切警告。

- 硬件引脚分配

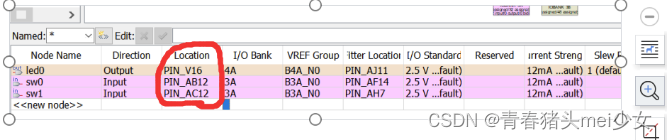

- 在菜单中选择Assignments>Pin planner打开引脚分配对话框。将引脚PIN_AB12和PIN_AC12分别分配给sw0和sw1,PIN_V16分配给ledr0。分配过程如下:在列表中查找预先定义的符号引脚名(在Node Name列),双击各个引脚的Location列以打开可用的物理引脚下拉框。选择一个引脚会把它分配给它的右边的网。你也可以键入引脚名。现在关闭Pin Planner面板。

-

- 注意:在BBLearn 界面中的文件DE1-SoC_User_manual.pdf中可查看引脚分配详细列表。

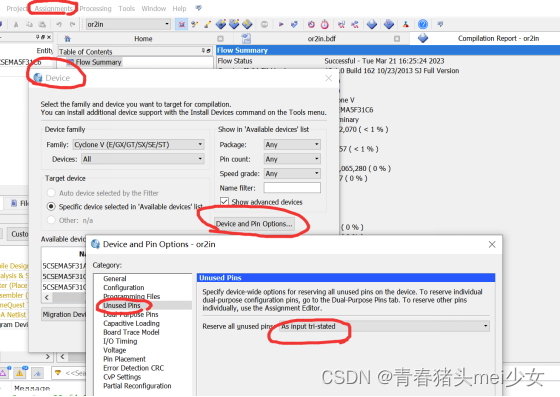

- 要点:在为各个节点设置恰当的物理引脚后,应该将其他所有引脚都设置为输入,这样它们就不会与板上的任何其他设备发生冲突。操作如下:选择Assignments>Device…,然后点击Device和Pin Options….选择Unused Pins选项卡。在组合框Reserve all unused pins中选择As input,tri-stated。点击两次OK即可。

-

- 保存并再次编译。此时如无错误,有一个警告“\Warning: Found 1 output pins without pin load capacitance assignment”(在编译完成后,你可以点击警告选项卡来检查),表明编译成功。下一步是仿真设计以验证设计的正确性。

- 仿真设计

- 点击“Tools→Run simulation tool→RTL simulation”打开ModelSim。在ModelSim主窗口,点击“File→Change directory”将目录切换到工程文件夹下,然后选择路径“C:\altera\PCO\lab1\simulation\modelsim”并点击OK。

- 点击“Compile→Compile”,在ModelSim文件夹下选择or2in.vhd(从Quartus目录复制过来,就是当前工作目录,即C:\altera\PCO\lab1)进行编译。

- 运行电路仿真时,需要为输入信号指定波形。该过程涉及以下简单命令:

-

- # force file for two-input logic gate

- # comment: need a # followed by a space

- force sw0 0;# comment: after a command, need a semicolon

- force sw1 0

- run 100ns

- force sw0 1

- run 100ns

- force sw1 1

- run 100ns

- force sw0 0

- run 100ns

- force sw1 0

- run 100ns

-

- 在simulation\modelsim目录下的文本文件or2in.do(自己新建文本文档,修改扩展名为do)中输入上述命令。输入过程中请注意代码中注释的格式。

-

- 通过Simulation>Start Simulation进入仿真模式。在设计选项卡中,展开work扩展项下面的or2in实体下的architecture structure项,点击OK。

-

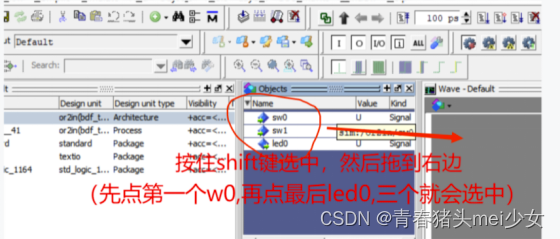

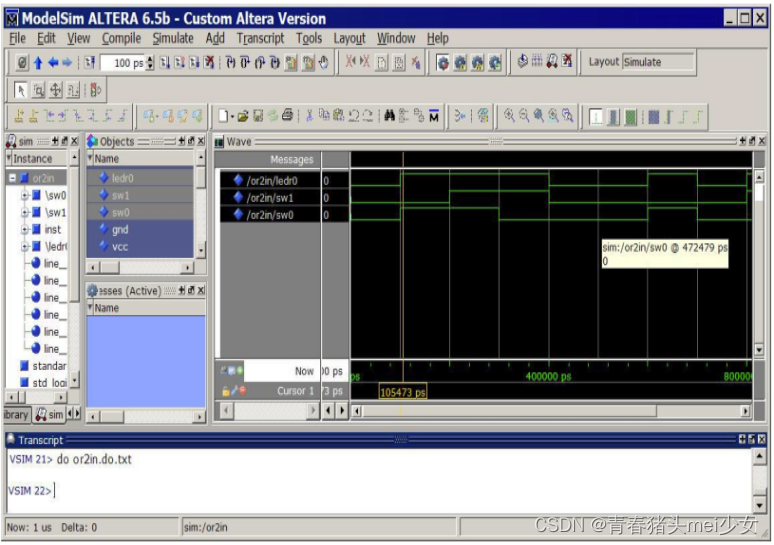

- 在Objects窗口中,选择3个引脚(ledr0,sw0和sw1)并拖拽到Wave窗口中。在命令窗中输入do或者or2in.do命令强制运行文件,即可在Wave窗口中看到波形。若wave窗口没出现,点击“view”菜单中勾选”wave”选项。

-

- 注意:如果无法看到正确波形,右键点击波形窗口选择“Zoom full”or按“F”键。

- 注意整个过程应无延迟,输入一变化输出就响应。这就是逻辑门被假定为理想的零延迟的函数仿真。

-

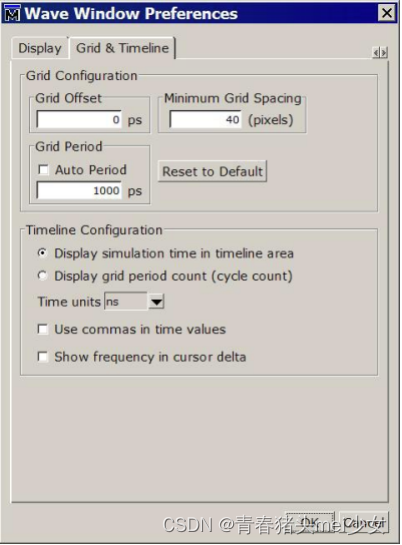

- 可以在Wave窗口中修改时间刻度。激活Wave框(在菜单项中),选择Wave>Wave preferences…并选择Grid&Timeline选项卡,将时间单位变为ns(纳秒)。点击OK。

-

- 在Wave窗口中保存波形(就是存盘,文件名自动为wave.do),关闭ModelSim。

- 编程FPGA板

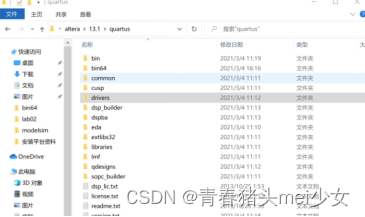

- 最后,采用在下拉菜单Tools下的Programmer工具对FPGA板进行编程。在编程过程中,请务必接入你的FPGA板并开启电源。(请安装驱动程序,我的电脑-)属性-》设备管理-)未知设备-》右键-》 更新驱动程序-》(浏览我的计算机以搜索驱动程序)手动搜索-》quartus文件夹中driver文件夹-》ok-》安装)。路径如下图:

-

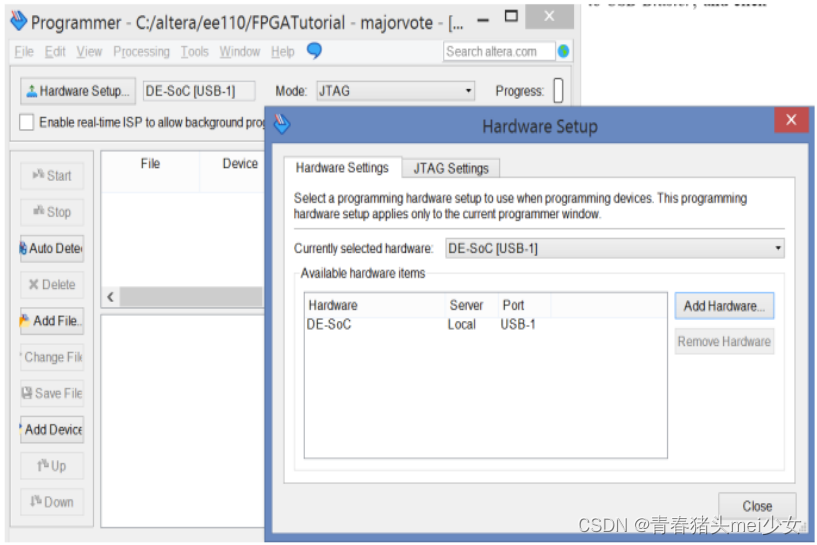

- 弹出Programmer窗口后,点击左上角的Hardware Setup按钮。然后将“Currently selected hardware”改变为USB-Blaster,点击关闭。

-

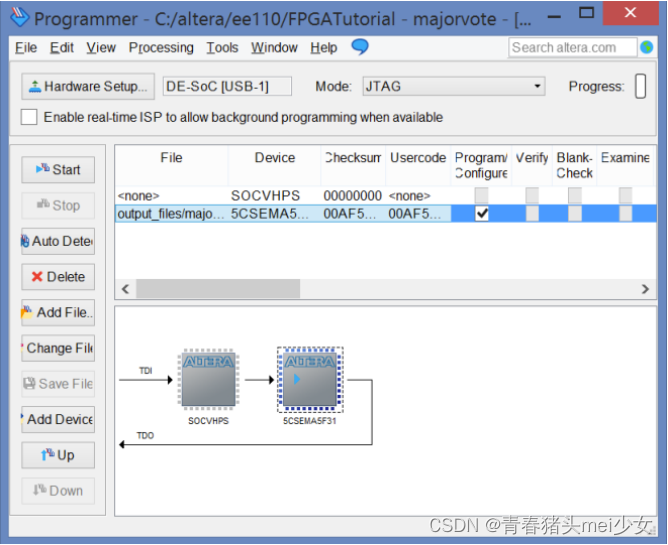

- 点击工具条左侧的Auto Detect,选择5CSEMA5并点击OK。右键点击5CSEMA5,选择“Change File”,在路径“C:\altera\PCO\lab\output_files”下选择or2in.sof文件,并点击“Open”。最后,选择Program/Configuration框(复选框)。

-

- 最后,点击Start按钮对设备进行编程,如此,就可以将你设计的电路编程到FPGA板上了!

- 在工程中创建一个revision

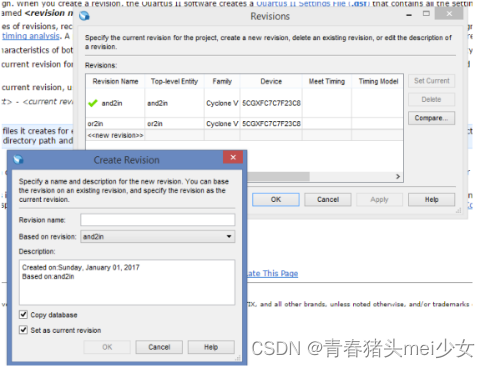

- revision是一个设计中为设计文件定义的一组设置和分配。你可以采用不同的revision来定义不同的设置和分配以决策他们如何影响处理设计的结果。例如:你可以采用多个revision来为同一个设备编译设计,这个设备具有不同的默认逻辑选项和时间分析设置。或者,也可以采用两个revision来为两台保持所有其他设置和分配不变的不同的设备编译同一个设计。

- 为当前工程创建一个新的revision,可以选择“Project->Revision”,在弹出的窗口中双击《new revision》。然后为创建的新revision选择基础revision并命名,点击OK。

-

- 你可以按照上图选择当前revision(绿色标记为当前选择的revision)

- 为了仿真或下载当前revision,需要将当前revision设置为顶层实体。操作方法为:“Project->Set as top-level entity”。

四、实验步骤

(1) 阅读说明书“Introduction to VHDL.doc”和“DE1-SoC_User_manual_rev.FG.pdf”,对Quartus II集成开发环境有基本的了解;

(2) 利用图编辑器创建顶层实体AND门和D触发器,生成对应VHDL脚本;

(3) 利用VHDL语言编写AND门和D触发器,生成相应图形块;

(4) 全程编译,创建VWF文件或者编写ModelSim的do文件对电路进行仿真;

(5) 根据Cyclone V指导书,为创建的电路分配物理引脚,锁定输入输出引脚,完成全程编译;

(6) 编程下载。下载 SOF 文件至 FPGA,将你的电路下载到FPGA板中,并进行功能验证。

五、实验结果与分析

|

1、各模块的设计电路和系统的整体电路

- 实验结果的记录与分析

|

|

|

|

- 实验中碰到的问题和解决的方法

软件难以破解安装,做到实验最后一步发现软件没有破解好,无法生成对应的SOF文件去烧录在板子上,最后只能重装软件解决。

4、几点认识和体会

通过本次计算机组成原理实验,我认识到了软件安装的困难和破解的困难,本次实验本身并不复杂,但配置环境变量特别麻烦,前期软件安装和破解需要十分的耐心和时间。后期的实验步骤需要先画出实验图,并使用仿真,得出波形图,最后烧录在板上,整个过程感觉特别费时间,但是真的特别磨练我的心智。

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?