目 录

2.2原理框图中各子模块的VHDL语言表述及生成模块框图... 3

一 课程设计的目的及意义

1.0设计目的

本次设计的目的就是在掌握计算机组成原理理论的基础上,了解EDA技术,掌握VHDL硬件描述语言的设计方法和思想,通过学习的VHDL语言结合电子电路的设计知识理论联系实际,掌握所学的课程知识,例如本课程设计就是基于所学的计算机原理中的数控分频器基础之上的,通过本课程设计,达到巩固和综合运用计算机原理中的知识,理论联系实际,巩固所学理论知识,并且提高自己通过所学理论分析、解决计算机实际问题的能力。进一步加深对计算机原理以及数字电路应用技术方面的了解与认识,进一步熟悉数字电路系统设计、制作与调试的方法和步骤

1.1设计意义

巩固所学课堂知识,理论联系实际,提高分析、解决计算机技术实际问题的独立工作能力。为了进一步了解计算机工作组成原理与系统结构,深入学习EDA技术,用VHDL技术,用VHDL语言去控制将会使我们对本专业知识可以更好地掌握。熟悉QUARUS II软件的应用。熟悉EDA实验开发系统的基本使用。学习用VHDL基本单元电路的时间应用。进一步掌握EDA的多层次设计方法

1.2 设计要求

-

- 在Quartus中编写VHDL程序实现年、月、日、时、分、秒各模块的功能。

(2) 将各模块在原理图中连接起来实现百年历计时功能。

(3) 将年、月、日和时、分、秒两种模式分别在试验箱模式7下显示,并设置键8为模式的切换键,键3 为调整数键,键6为在当前模式下切换调整位键。将各端口引脚绑定好并下载到实验箱实现其功能,观察是否能实现相应功能效果,如是否可以进位,是否能判断闰年等等。

二 设计流程:

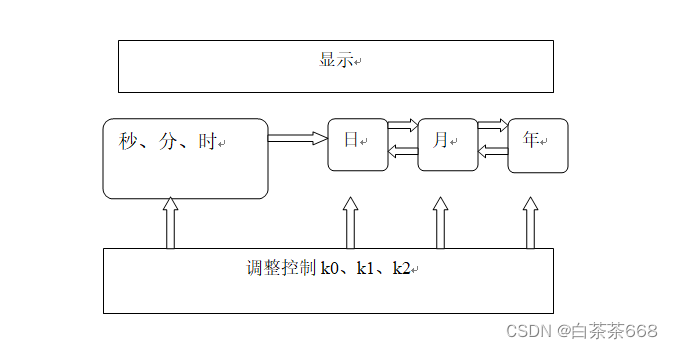

2.0 万年历原理

秒、分是60进制,时是24进制,日31天由月1.3.5.7.8.10.12控制,日28/29由2月和润年控制,日30由月4.6.9.11控制。原理如下图:

2.1 原理框图

根据实验要求,截得实验原理框图如下:

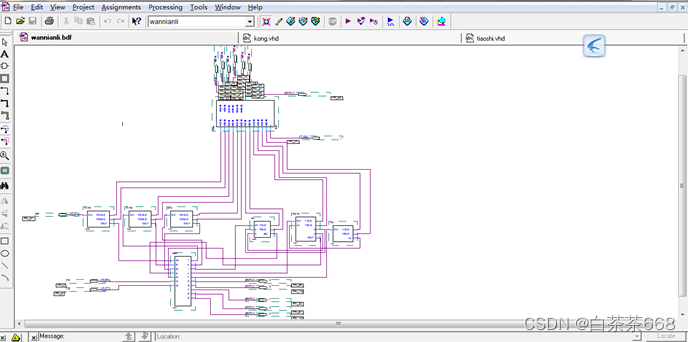

2.2 原理框图中各子模块的VHDL语言表述及生成模块框图:

2.3 VHDL设计流程

(1)设计输入根据电路设计所提出的要求,将程序输入到VHDL编辑器中区编辑。

(2)功能及模拟用VHDL,模拟器对编辑后的程序进行模拟,如果达不到设计要求,则可以重新修改程序,直到通过功能模拟。

(3)逻辑综合与优化,将通过功能模拟的程序放到VHDL编译器中,进行逻辑、综合与优化。

三 部分VHDL程序

3.0 60进制计数器

library ieee;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT60 IS

PORT(CLK:IN STD_LOGIC;

CQ1,CQ2:OUT STD_LOGIC_VECTOR (3 DOWNTO 0);

COUT:OUT STD_LOGIC);

END CNT60;

ARCHITECTURE behav OF CNT60 IS

BEGIN

PROCESS(CLK)

VARIABLE Q1,Q2: STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

IF CLK'EVENT AND CLK='1' THEN

Q1:=Q1+1;

IF Q1>9 THEN Q1:="0000";Q2:=Q2+1;

END;

3.1 24进制计数器

library ieee;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY cnt24 IS

PORT(CLK:IN STD_LOGIC;

CQ1,CQ2:OUT STD_LOGIC_VECTOR (3 DOWNTO 0);

PROCESS(CLK)

VARIABLE Q1,Q2: STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

IF CLK'EVENT AND CLK='1' THEN

Q1:=Q1+1;

IF Q1>9 THEN Q1:="0000";Q2:=Q2+1;

END IF;

IF Q2=2 AND Q1=4 THEN Q1:="0000";Q2:="0000";COUT<='1';

ELSE COUT<='0';

END IF;

END IF;

CQ1<=Q1;CQ2<=Q2;

END PROCESS;

END;

3.2 天计数模块

Library ieee;

USE IEEE.STD_LOGIC _UNSIGNED.ALL;

USE IEEE.STD_LOGIC _1164.all;

Entity day is

Port( clk : in std_logic;

a,b : in std_logic;

T1,T2 : out std_logic_vector(3 downto 0);

PROCESS(clk,a,b)

begin

IF CLK'EVENT AND CLK='1' THEN

Q1<=Q1+1;

IF Q1=9 THEN Q1<="0000";Q2<=Q2+1;

end if;

ab<=a&b;

case ab is

when"00"=>

if Q2=3 AND Q1=1 THEN

8552

8552

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?