第四章 存储子系统-2

主存储器的组织涉及到这样一些方面:

(1)从存储器基本逻辑设计角度看,半导体存储器的逻辑主要是寻址逻辑;

(2) 如果采用DRAM,还需考虑动态刷新问题;

(3) 所构成的主存如何与CPU连接、匹配;

1.驱动能力

2.存储器芯片与CPU的时序配合

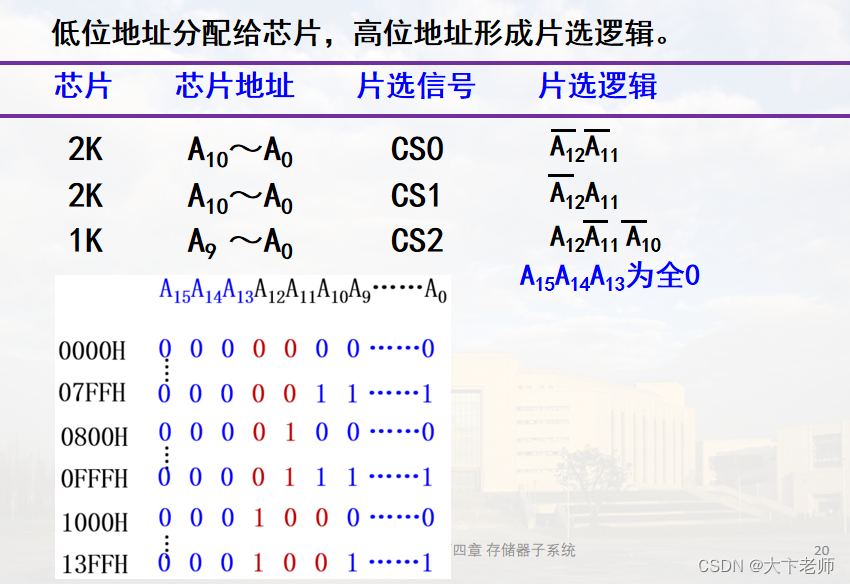

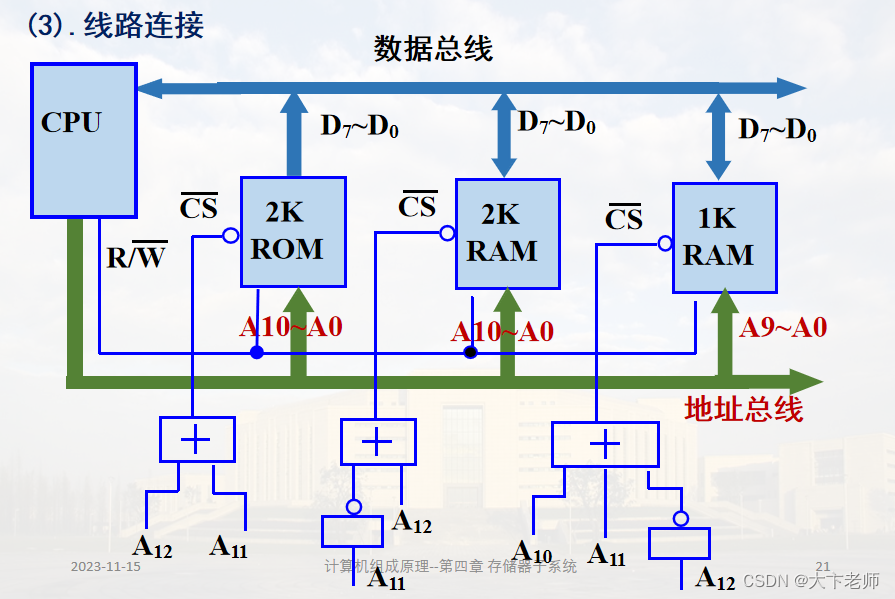

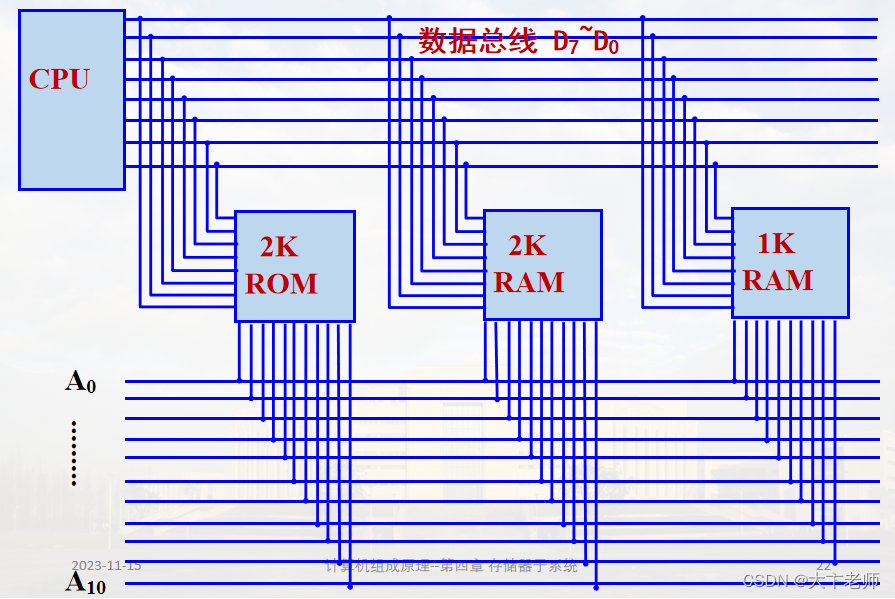

3.存储器的地址分配和片选译码

4.行选信号和列选信号的产生

(4) 主存校验,如何保证存取信息的正确性。

一、主存储器的逻辑设计

1、设计主存时,需要注意两点:

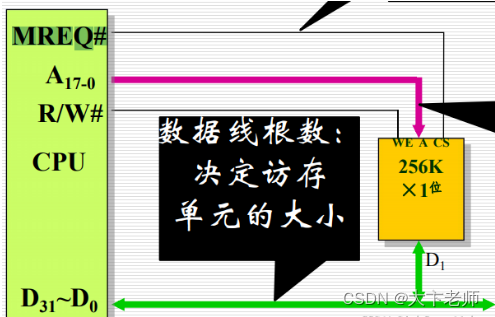

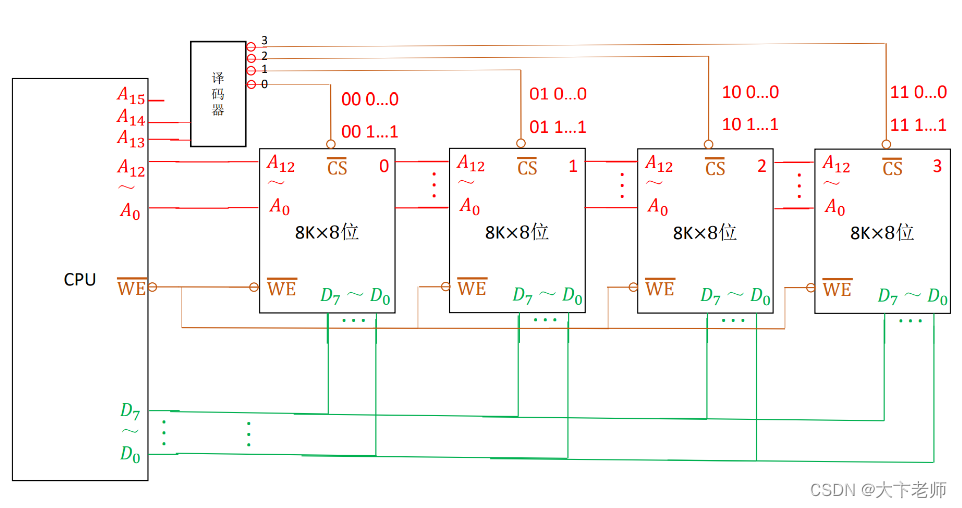

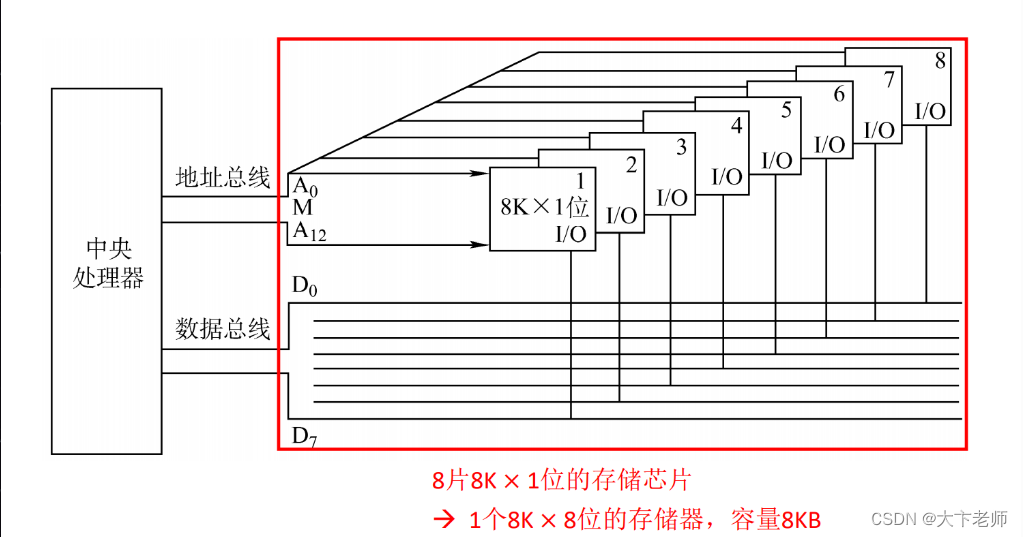

那我们看一下最简单的一个情况: 单块存储芯片与CPU的连接 假设有一块 8Kx1位 的存储芯片,说明此芯片需要 13根地址线,CPU有8个数据线和16根地址线,从上面可以看出,CPU每次只能传送1位数据到该芯片中,这会导致CPU的数据线没有得到充分利用,并且会有需要扩展主存容量的情况。扩展如下

假设有一块 8Kx1位 的存储芯片,说明此芯片需要 13根地址线,CPU有8个数据线和16根地址线,从上面可以看出,CPU每次只能传送1位数据到该芯片中,这会导致CPU的数据线没有得到充分利用,并且会有需要扩展主存容量的情况。扩展如下

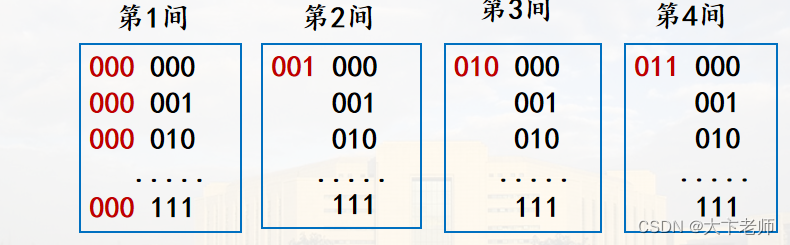

译码选片和译码选单元关系:假设拟修建一栋教学楼, 最多可以有64排座位, 给定了一个6位数的编号(二进制):A0、A1、A2、A3、A4、A5实际修建了4间教室, 每间8排(共32排)。要从64个编号中为这32排座位选32个号。假设选低32个编号。 PS:1.每间教室内的坐位的编号都相同(由低3位确定)2.高3位用来判断是哪一间教室。存储芯片相当于教室,选片相当于选教室, 由地址的 高位部分译码产生片选信号; 选哪一个单元相当于选哪一排坐位,由芯片接收地址的 低位部分在芯片内译码来选择哪一个单元。 这里的高位部分和低位部分的具体位数由芯片的容量、CPU提供的地址位数、以及拟构成的存储器的容量来决定。因此,存储器设计需要为芯片分配地址, 并根据所分配的地址来设计译码器以产生片选信号; 而选择单元的译码由存储芯片内置的译码器完成, 与存储器组织者无关。

PS:1.每间教室内的坐位的编号都相同(由低3位确定)2.高3位用来判断是哪一间教室。存储芯片相当于教室,选片相当于选教室, 由地址的 高位部分译码产生片选信号; 选哪一个单元相当于选哪一排坐位,由芯片接收地址的 低位部分在芯片内译码来选择哪一个单元。 这里的高位部分和低位部分的具体位数由芯片的容量、CPU提供的地址位数、以及拟构成的存储器的容量来决定。因此,存储器设计需要为芯片分配地址, 并根据所分配的地址来设计译码器以产生片选信号; 而选择单元的译码由存储芯片内置的译码器完成, 与存储器组织者无关。

补充:

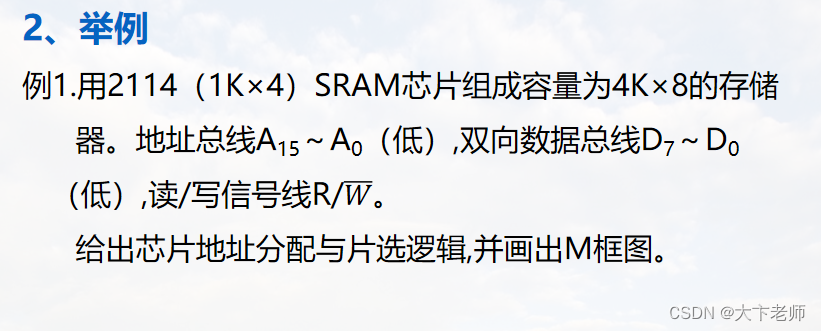

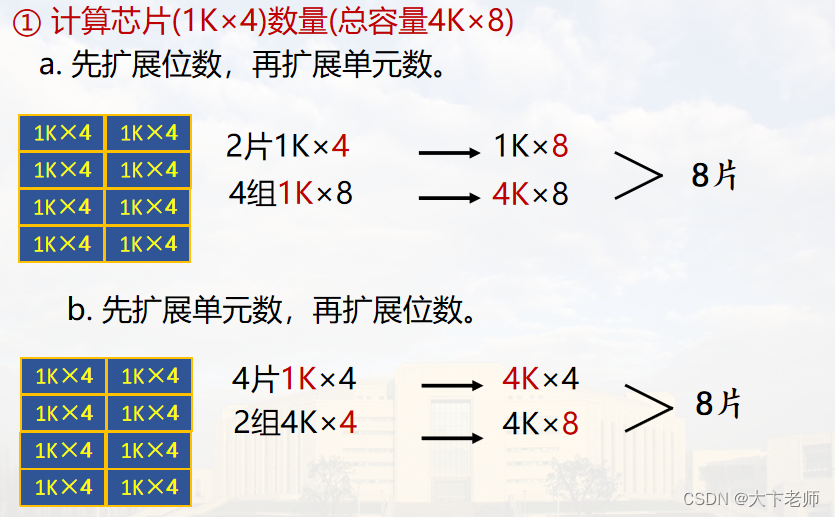

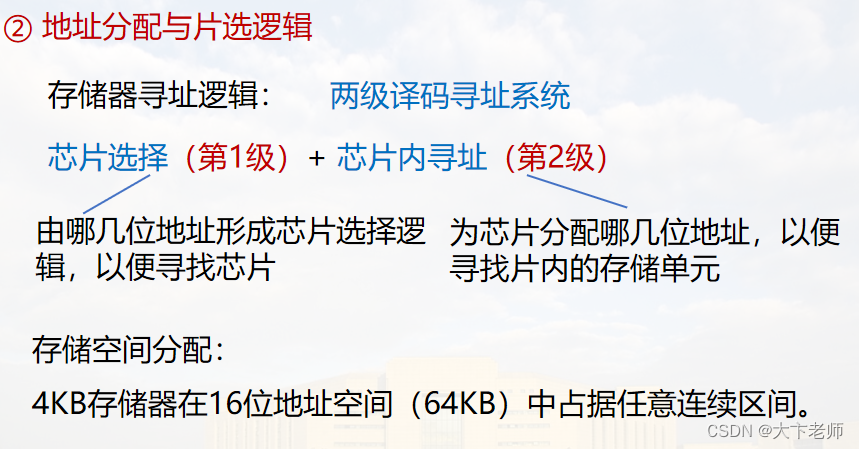

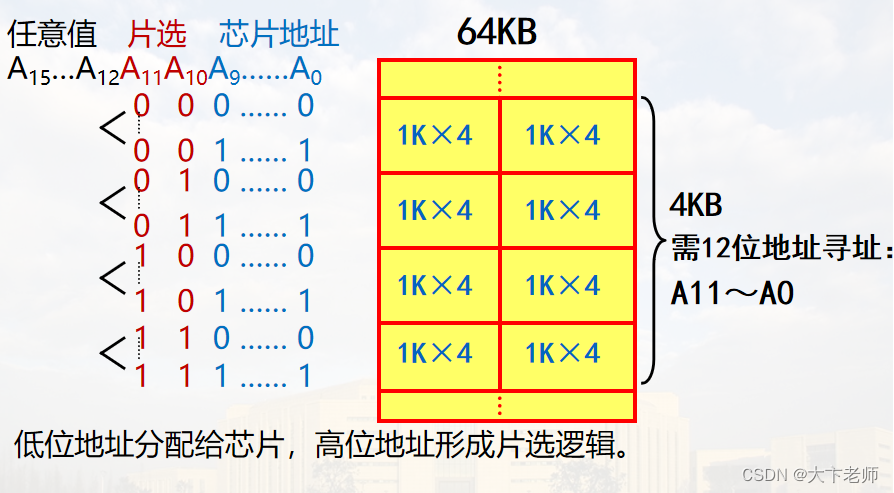

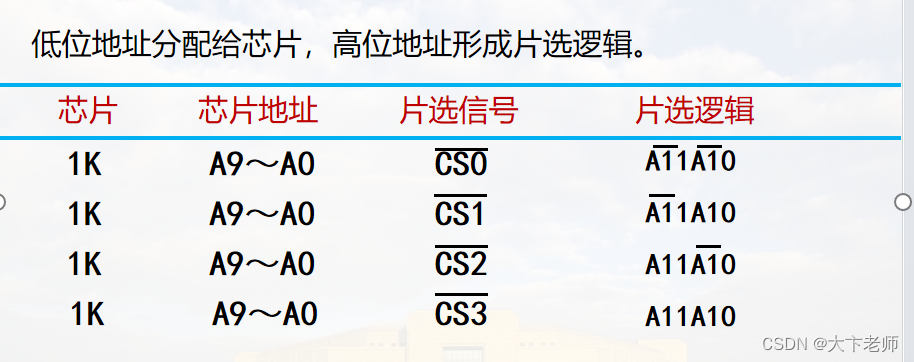

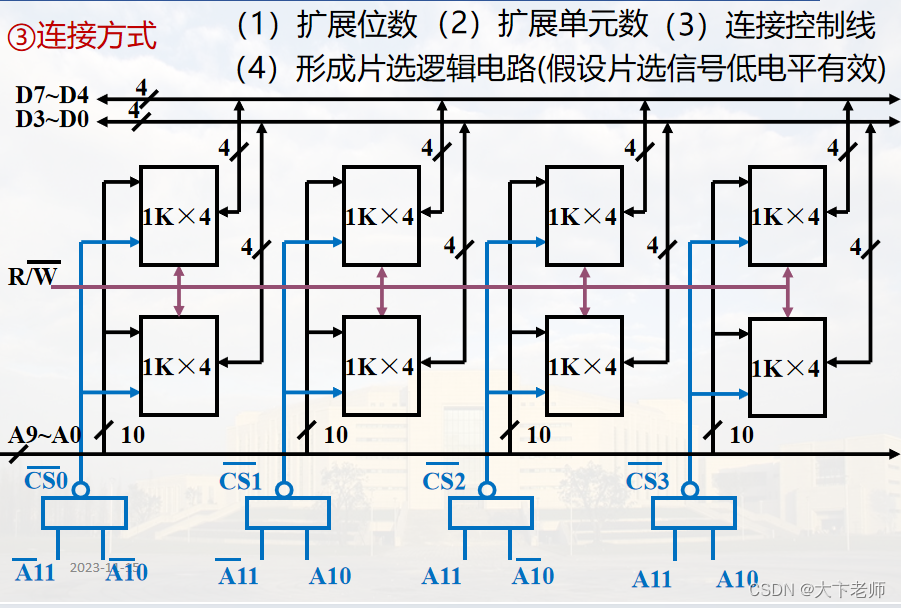

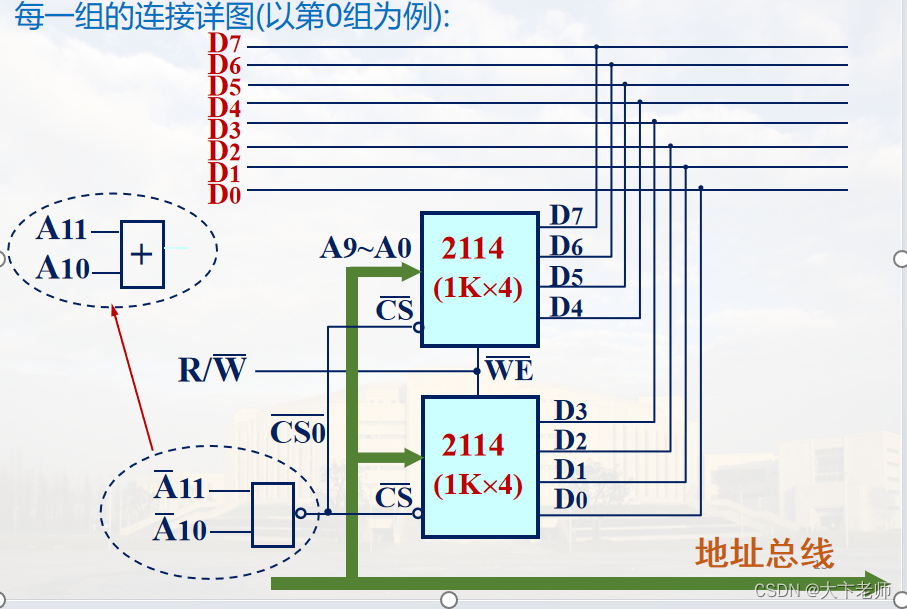

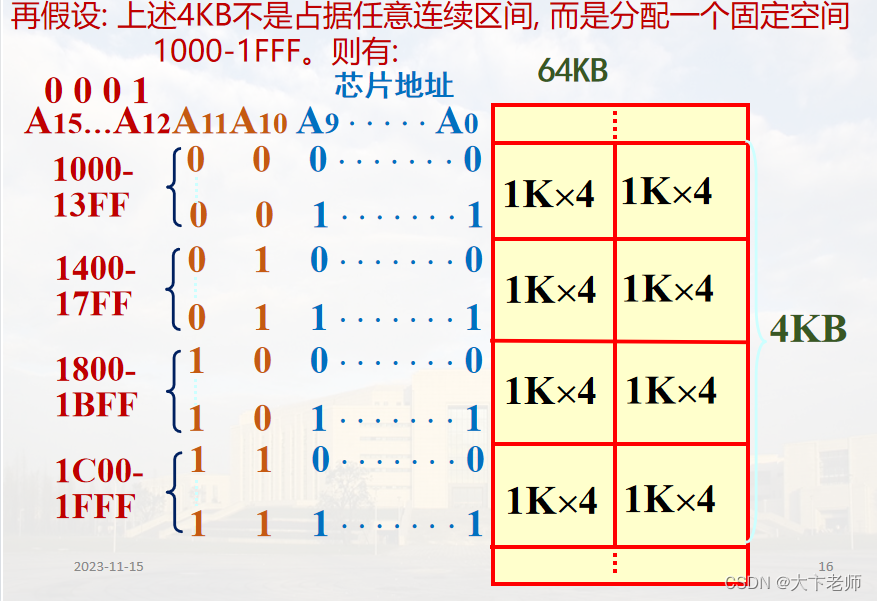

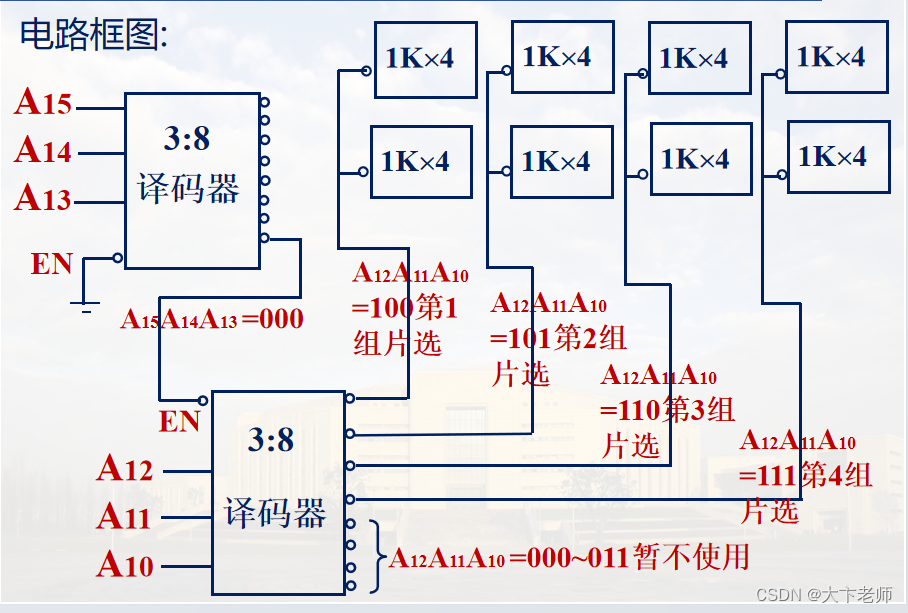

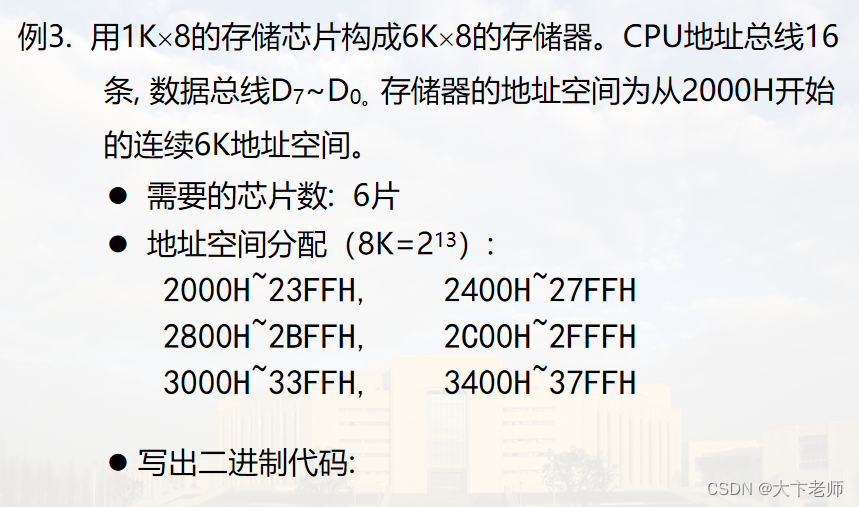

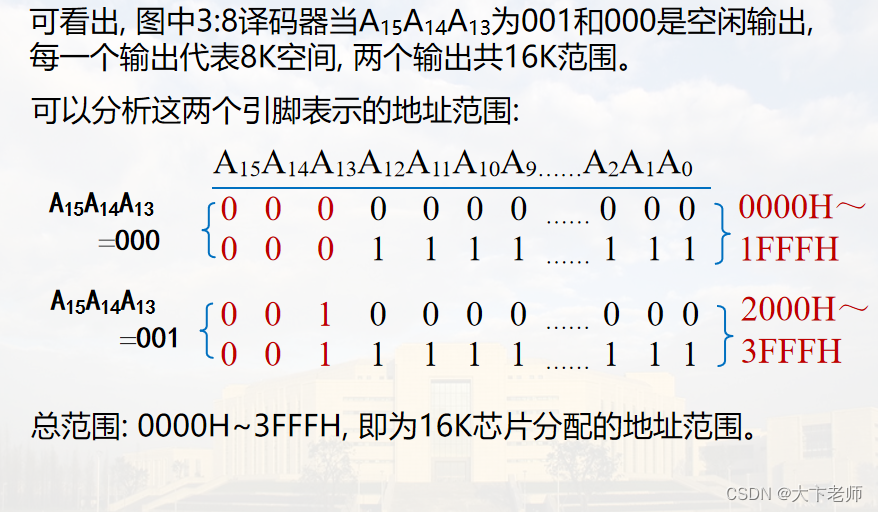

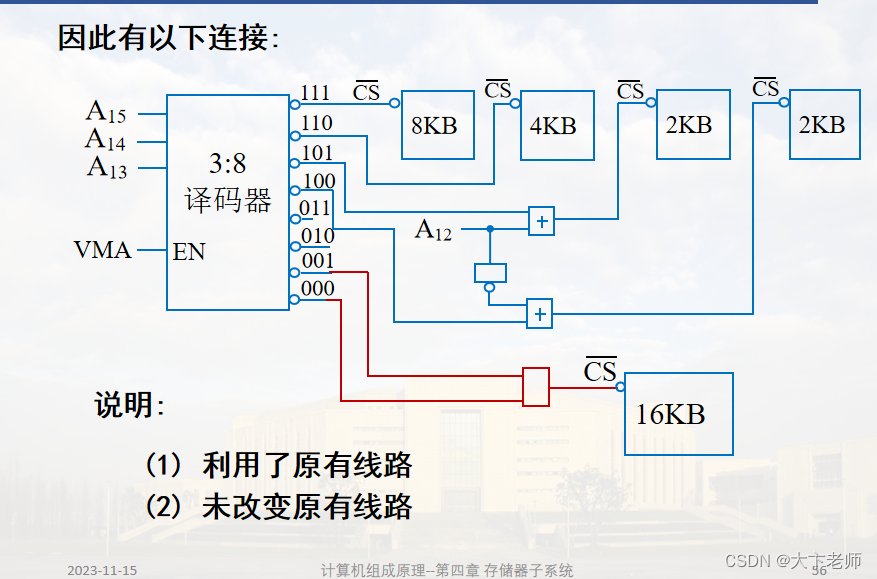

2.举例

PS:12位寻址的由来:1KB=2^10,4KB=2^12.任意值的位置叫做使能端;

一定要注意上面的存储逻辑电路图

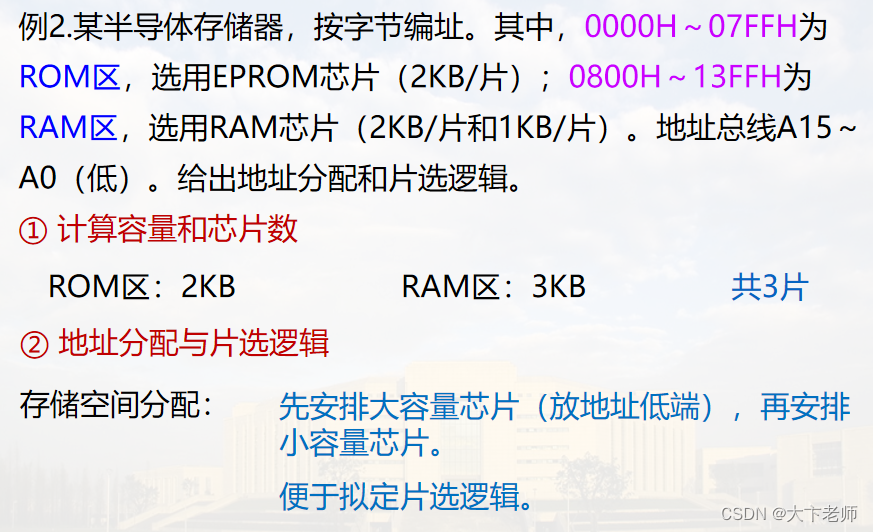

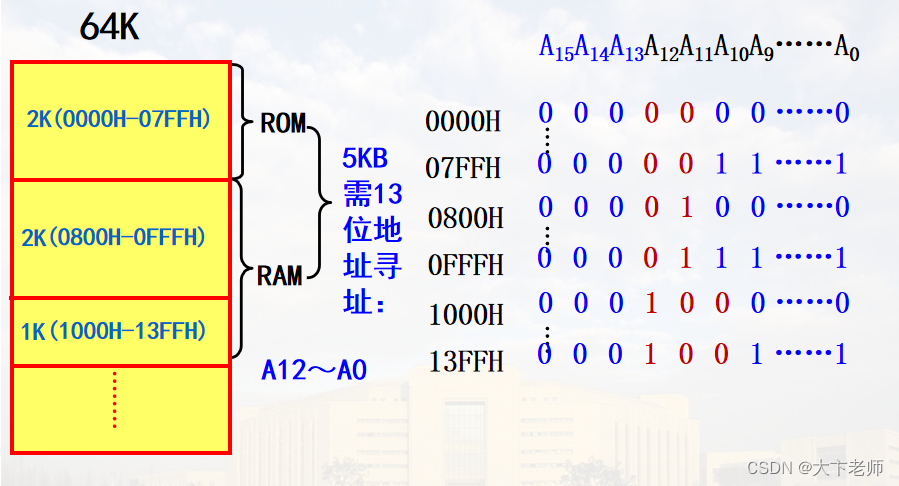

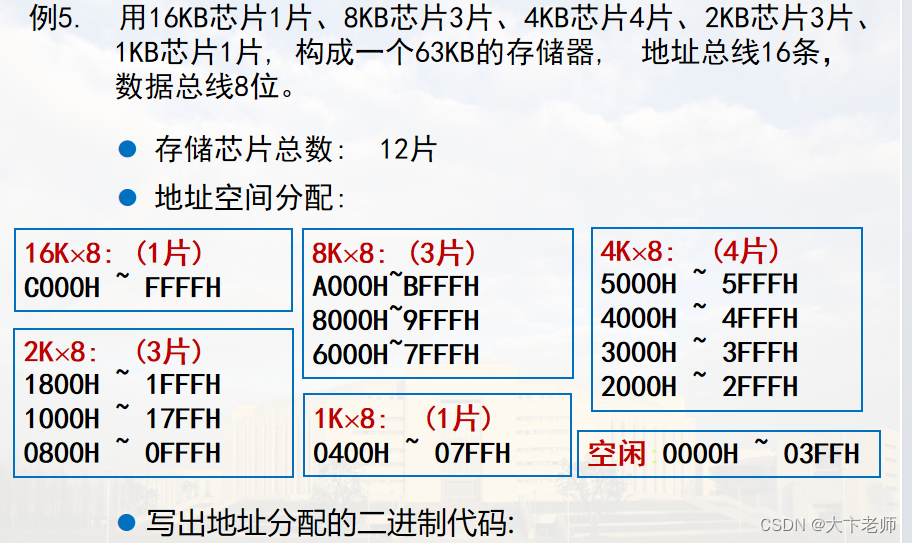

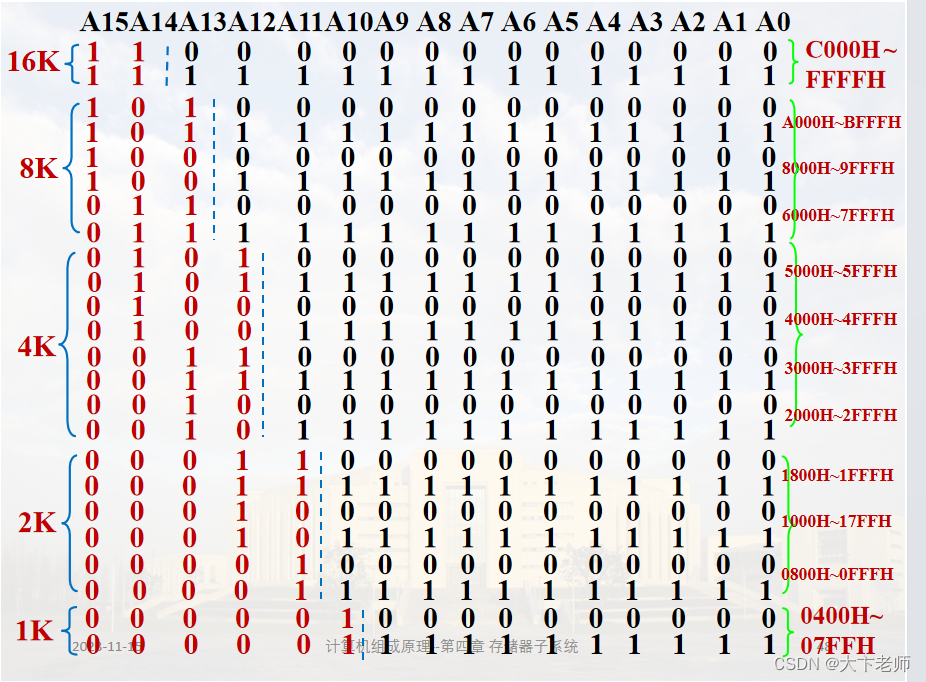

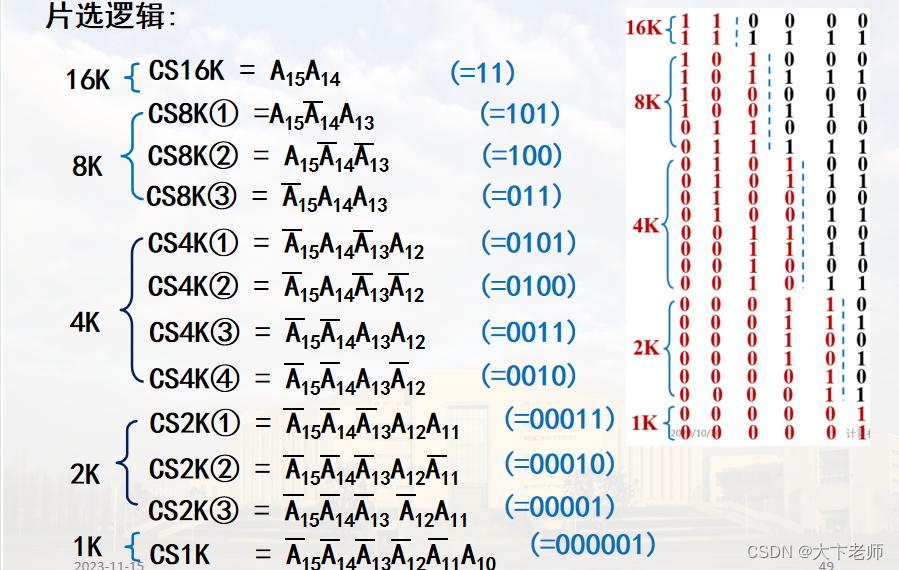

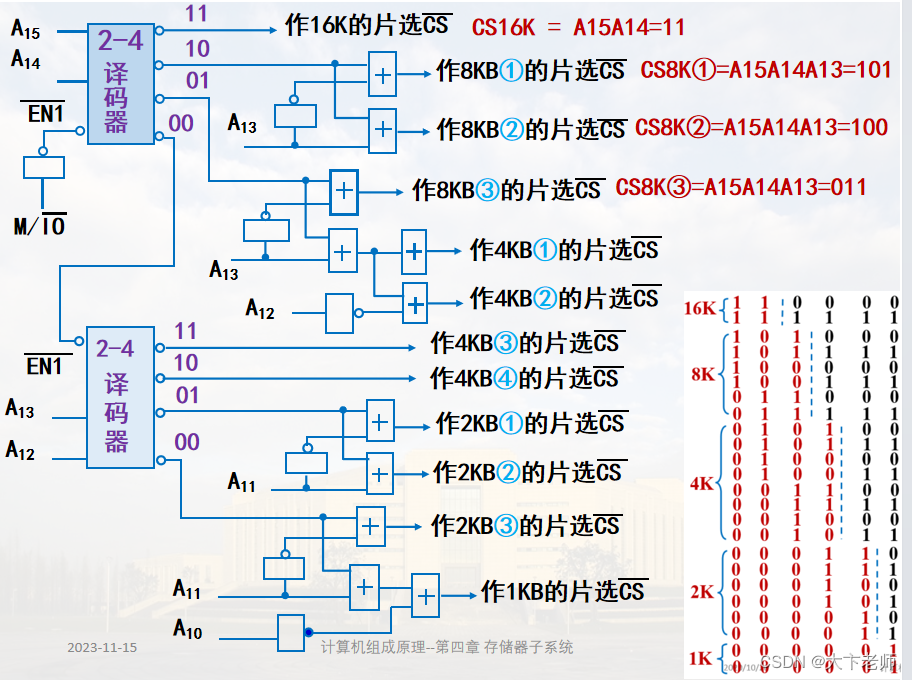

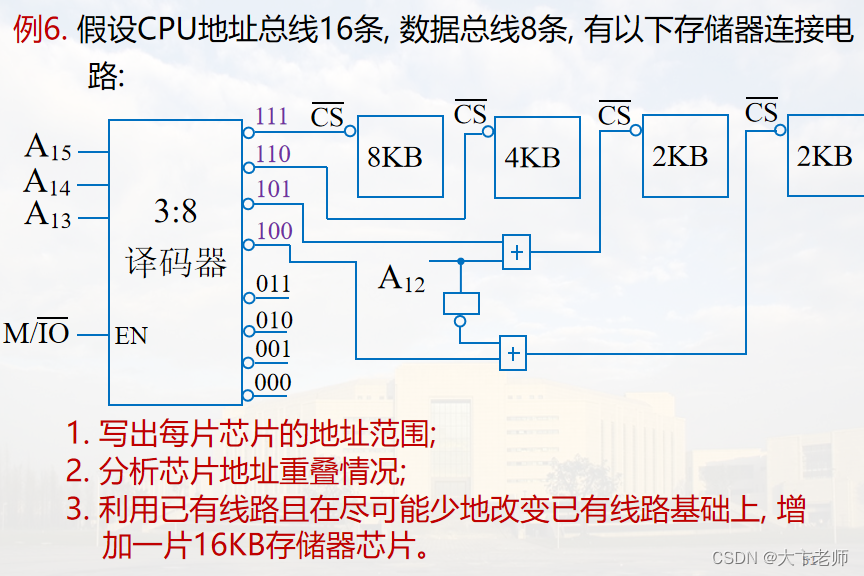

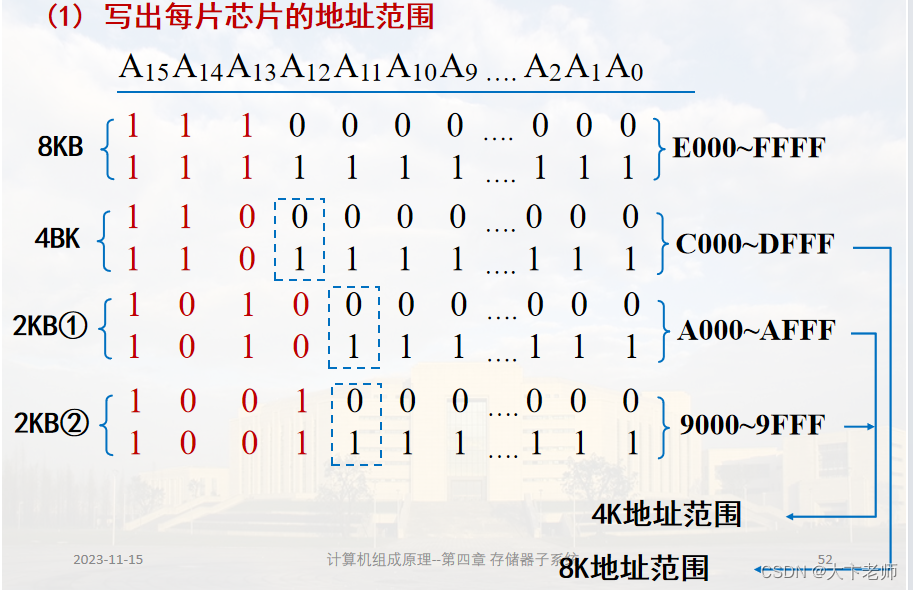

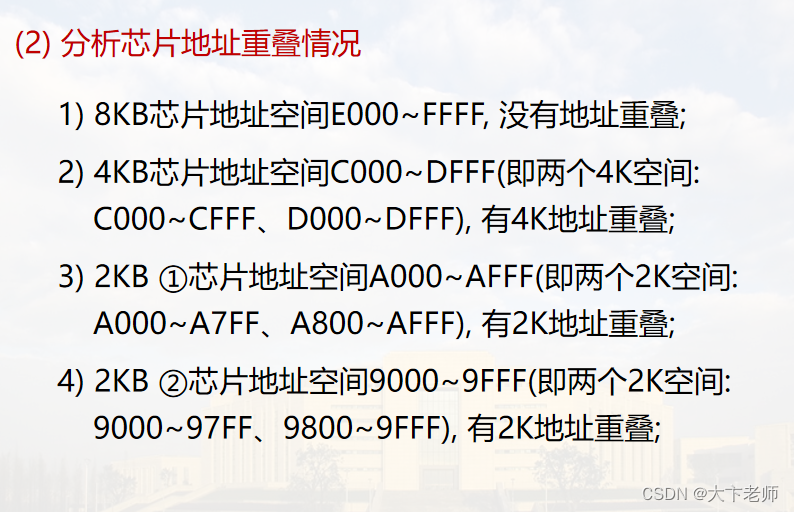

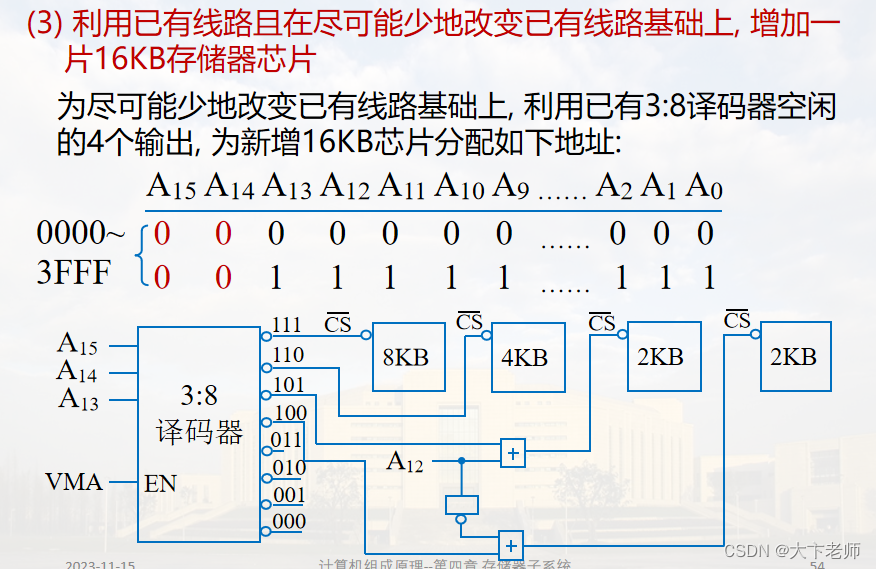

我们再看一个例题

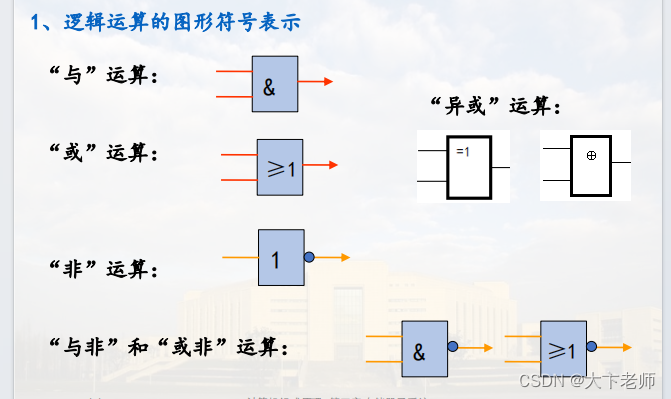

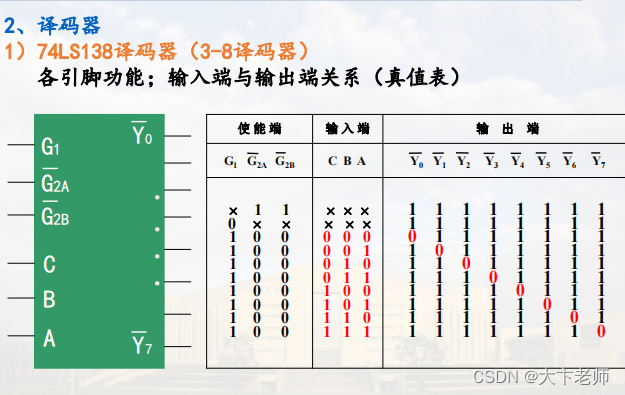

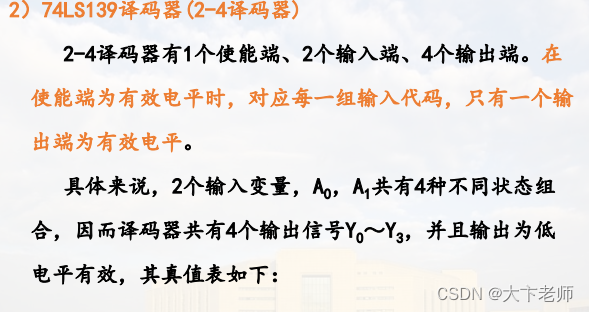

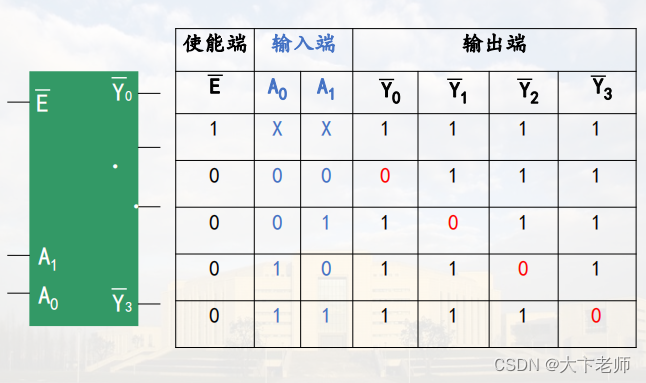

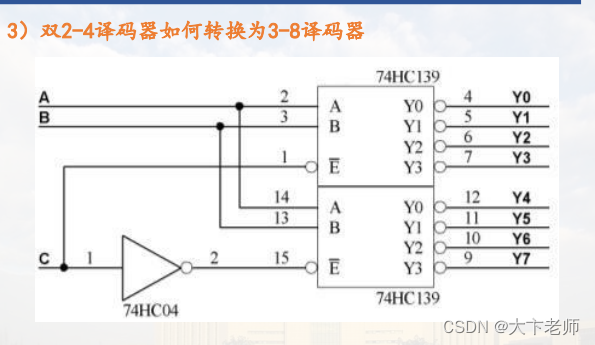

二、基本逻辑门及译码器

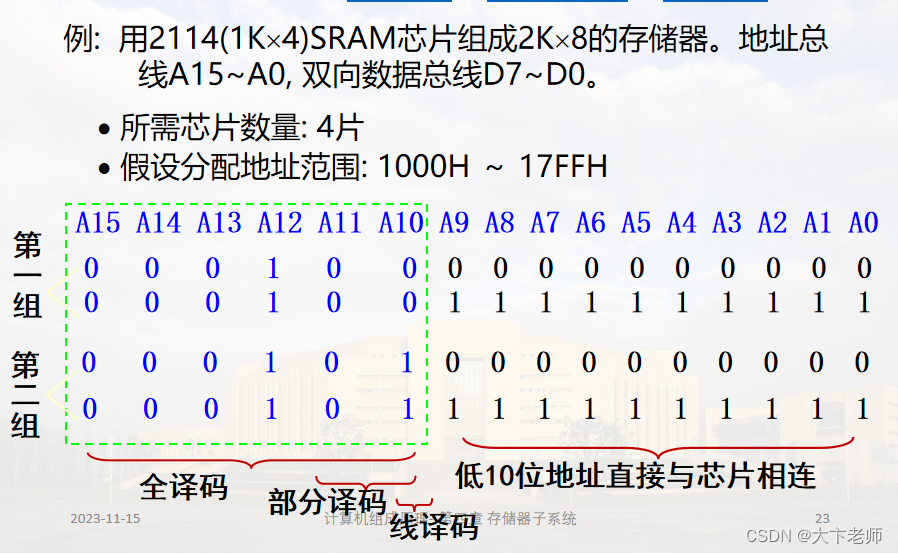

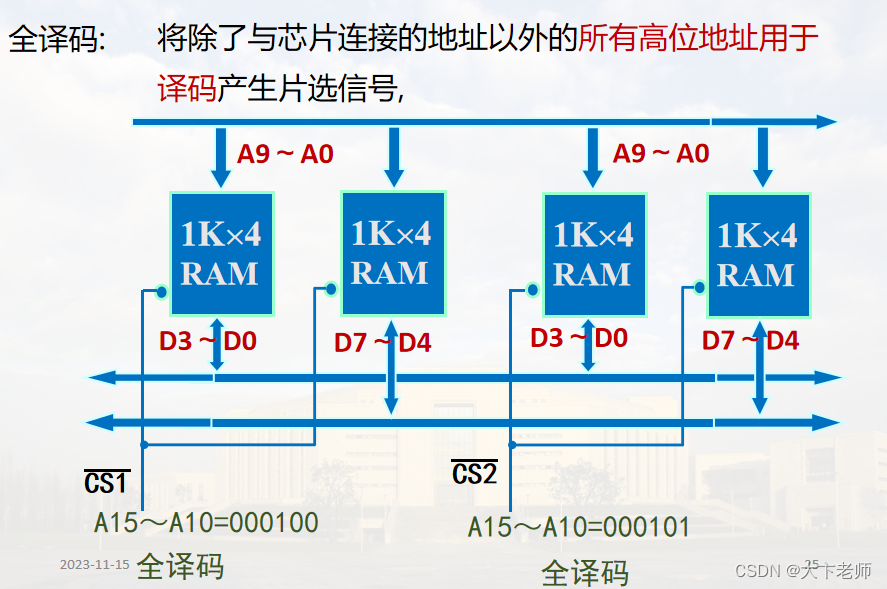

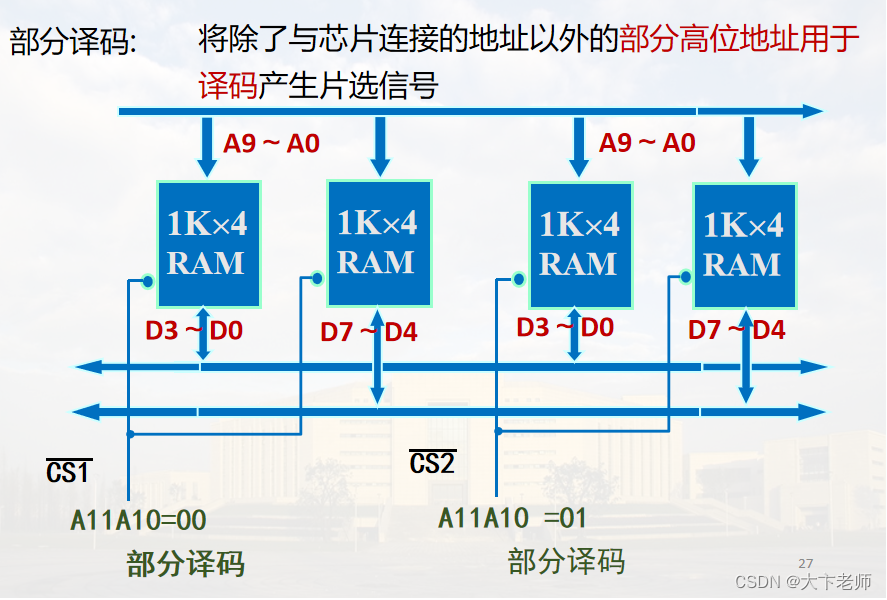

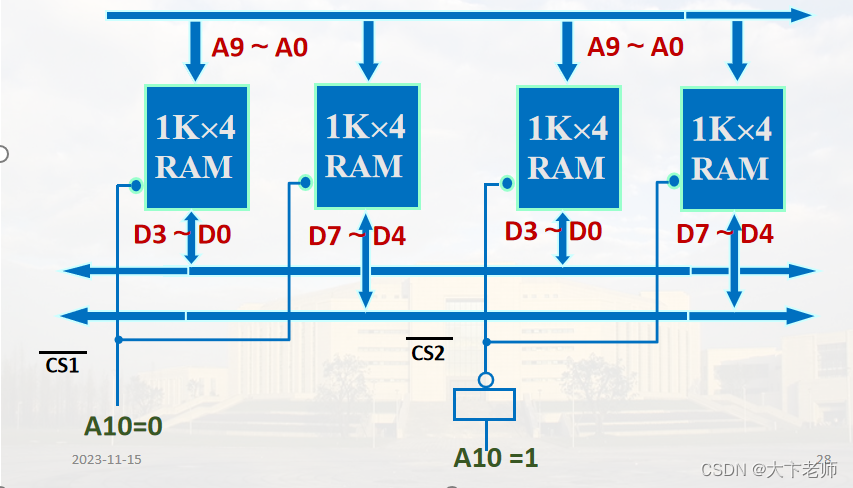

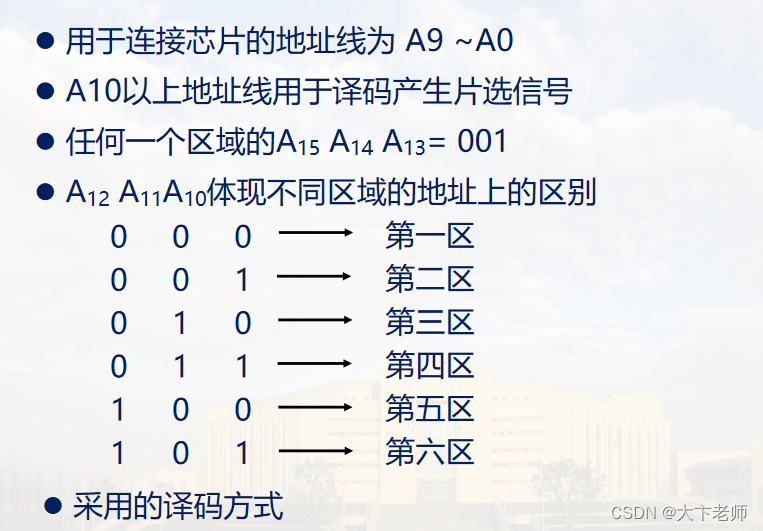

3、地址译码方法:全译码、部分译码和线译码

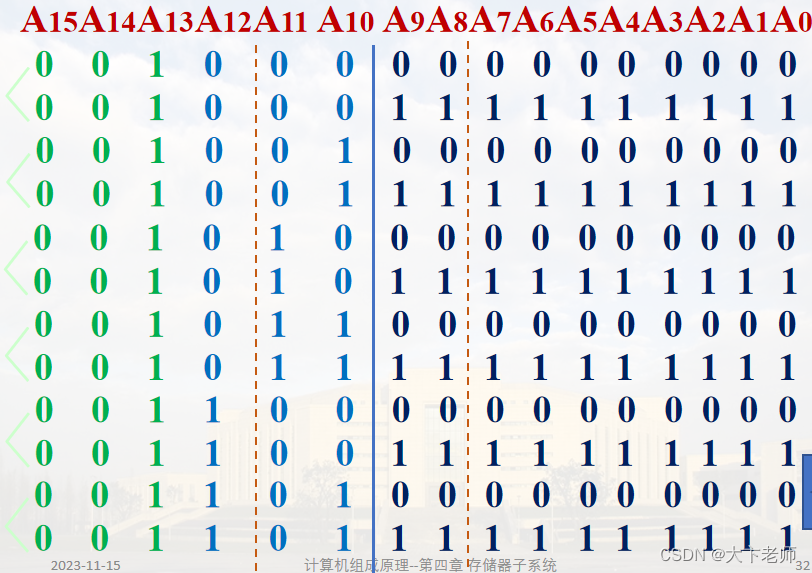

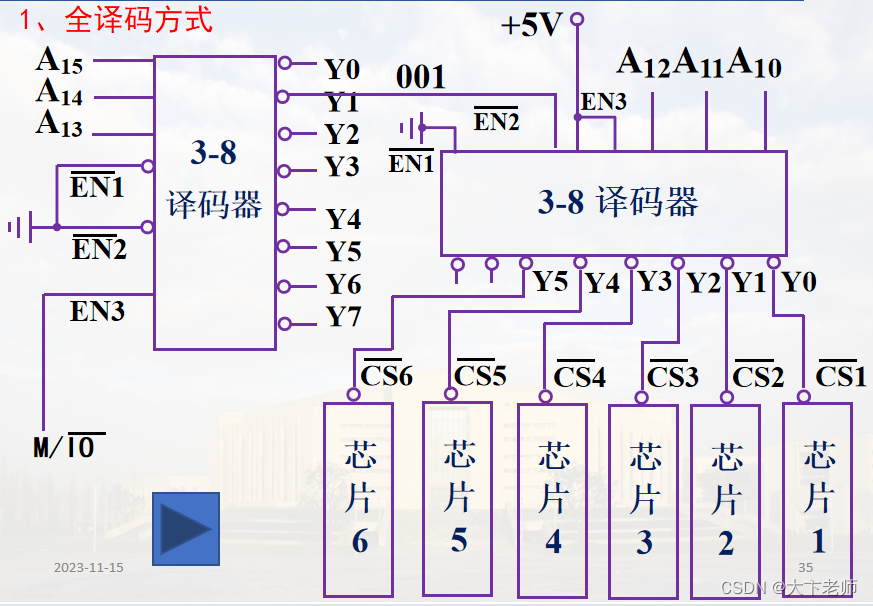

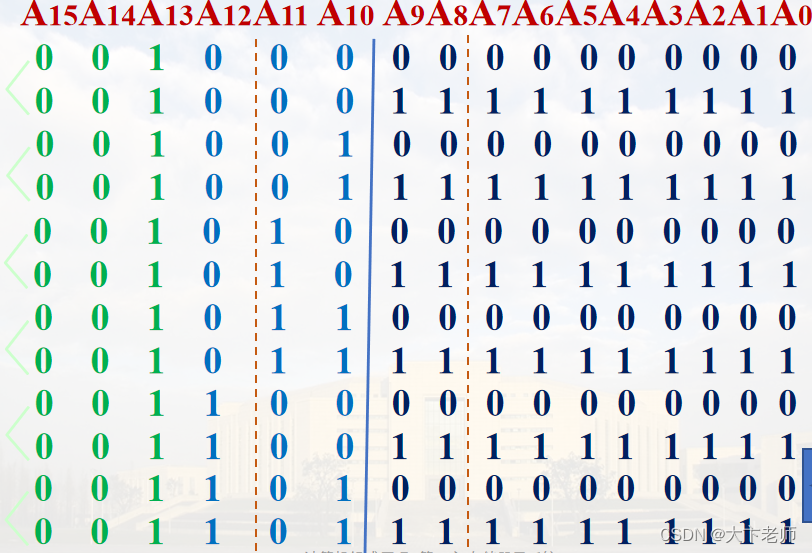

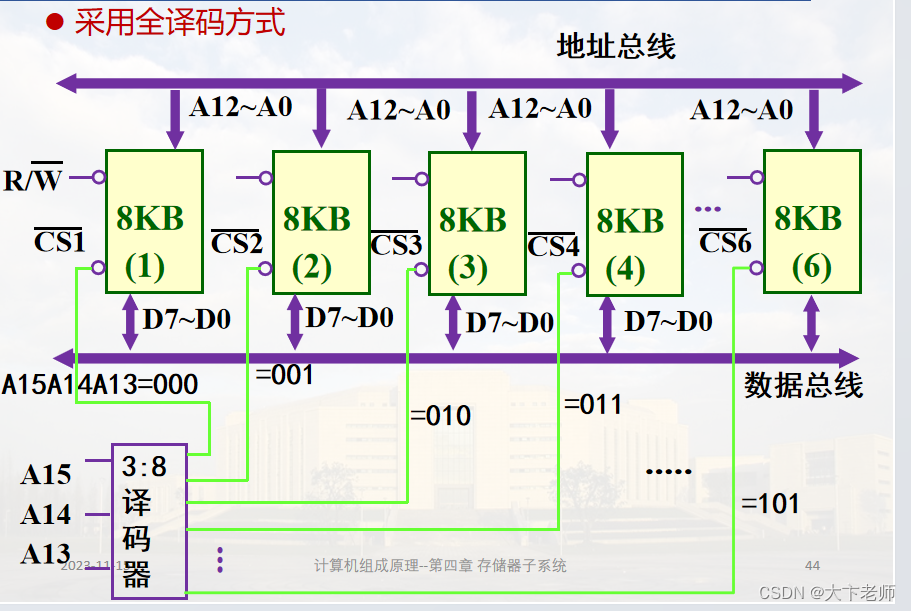

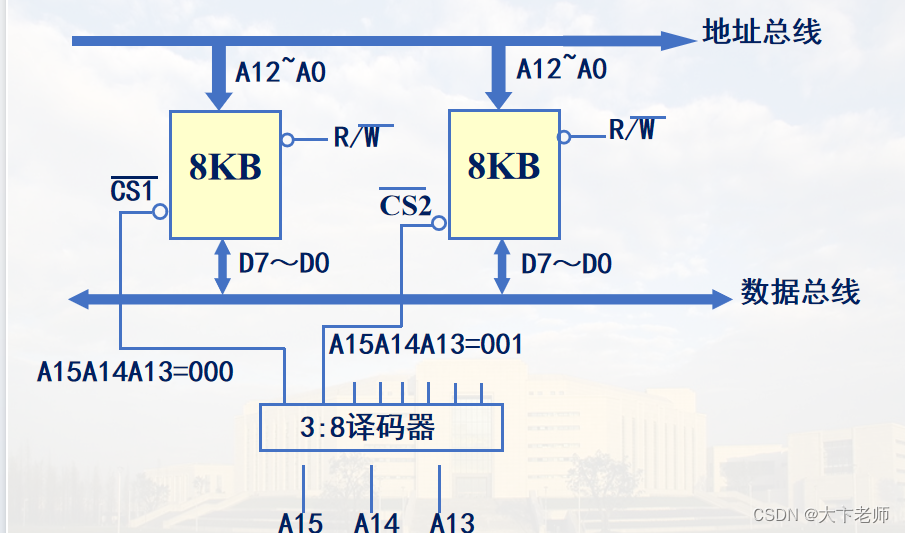

(1)全地址译码方式

就是构成存储器时要使用全部地址总线信号,即所有的高位地址信号都用来作为译码器的输入,低位地址信号接存储芯片的地址输入线,从而使存储器芯片上的每一个单元在整个内存空间中具有唯一的地址。

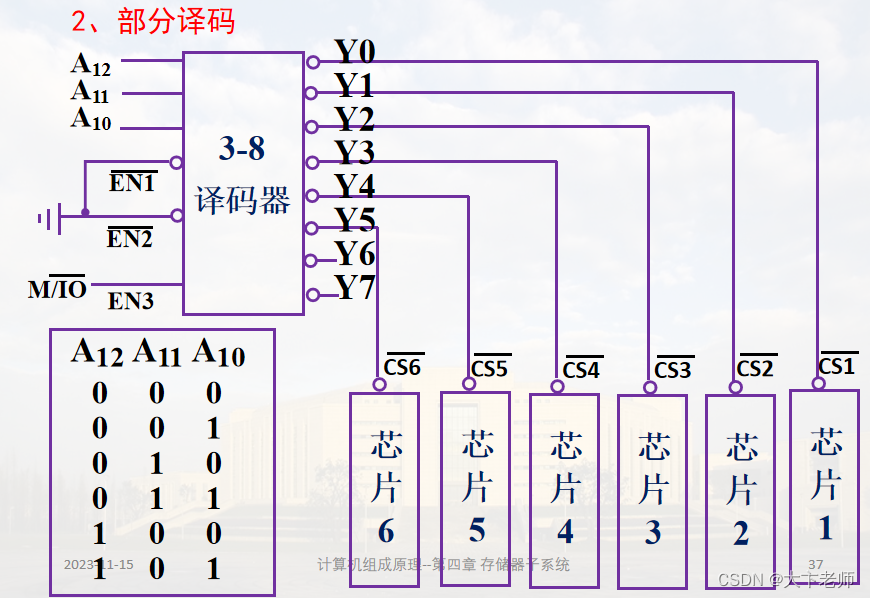

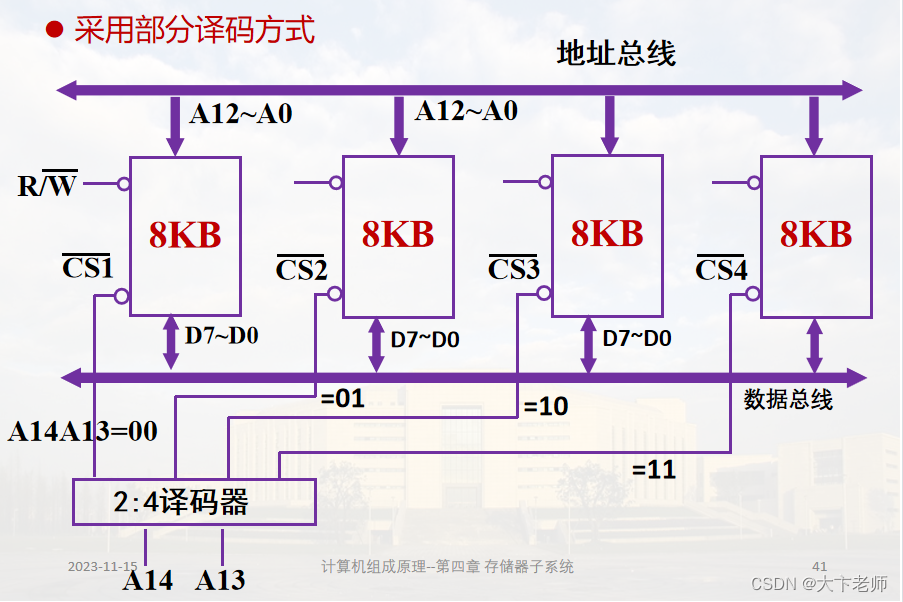

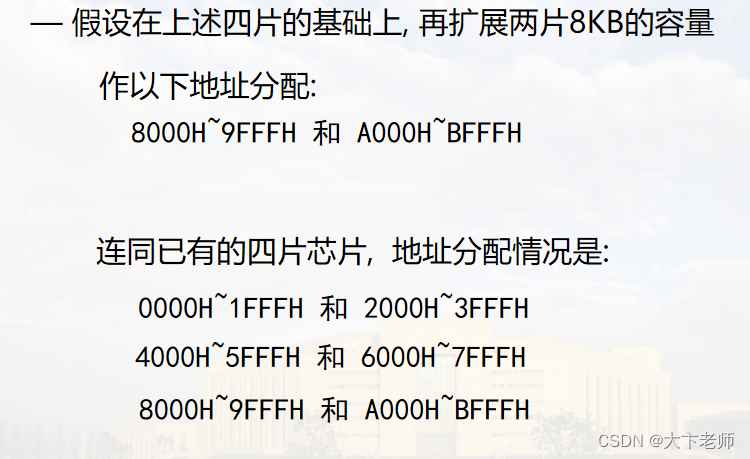

(2)部分地址译码方式

就是仅把地址总线的一部分地址信号线与存储器连接,通常是用高位地址信号的一部分(而不是全部)作为片选译码信号;低位地址信号接存储芯片的地址输入线。

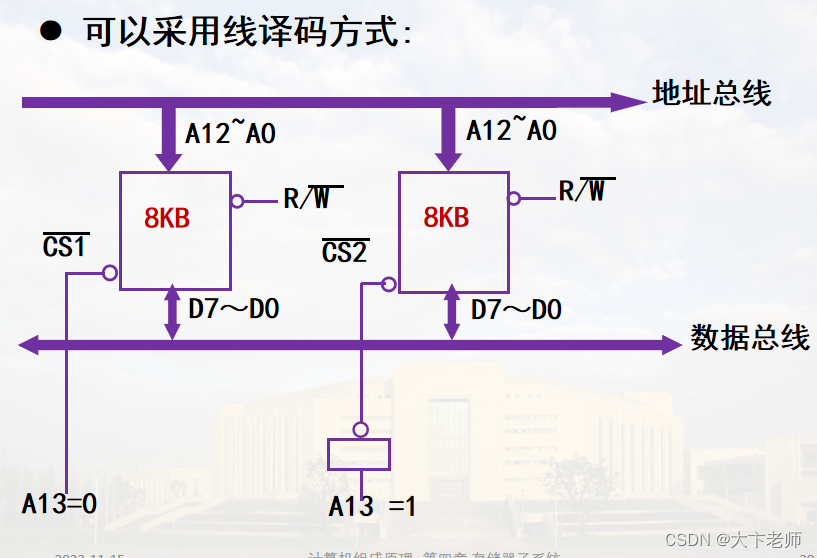

(3)线译码

直接用一条可以区分两组地址范围的地址线的高低电平作为片选信号

(4)全地址译码、部分地址译码特点

1.部分地址译码使地址出现重叠区,而重叠区的部分必须空着不准使用,这就破坏了地址空间的连续性,也在实际上减少了总的可用存储地址空间。其优点是其译码器的构成比较简单,成本较低。

2.全地址译码使存储器芯片上的每一个单元在整个内存空间中具有唯一的地址。

3.在实际应用中,采用全地址译码还是部分地址译码应根据具体情况来定。如果地址资源很富余,为使电路简单可考虑用部分地址译码;如果要充分利用地址空间,则应采用全地址译码。

三种译码方式的应用场合:

所设计的存储器达到(或接近达到)CPU提供的全部存储空间时, 必须用全译码, 且任何时候都可以使用全译码方式

所设计的存储器未达到CPU提供的全部存储空间时, 可以用部分译码或线译码。

可采用全译码与部分译码相结合的方式, 即部分芯片用全译码, 另一些芯片采用部分译码。

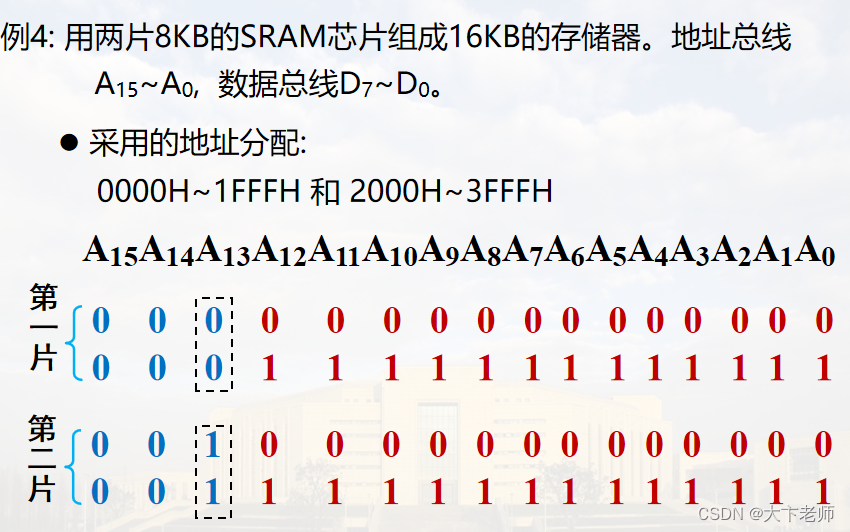

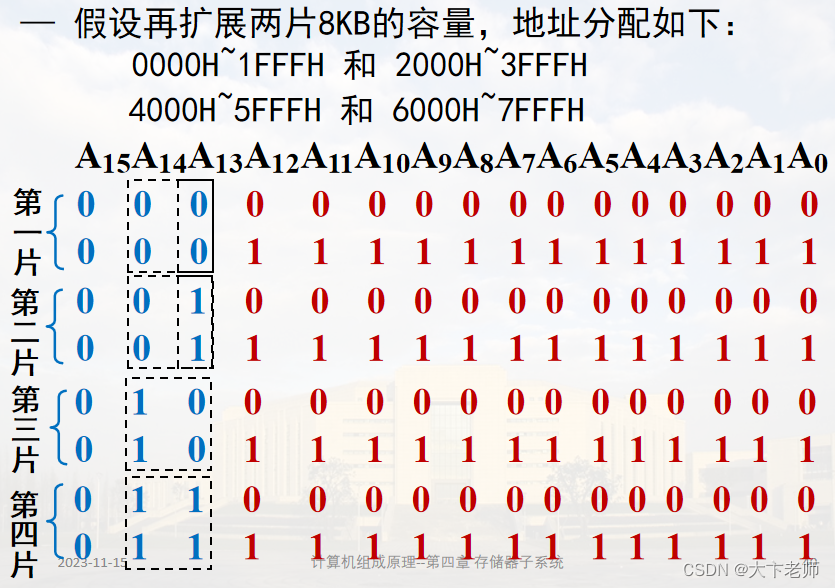

线译码例题

线译码例题

(5)总结:

(1)采用线译码和部分译码方式,译码线路简单,但是可扩展性差;

(2)采用哪一种译码方式取决于所设计的存储系统的容量;

(3)任何容量的存储器系统都可以采用全译码方式, 可扩展性好。(比如下面例: 仅有两片8KB的芯片时, 采用全译码方式:)

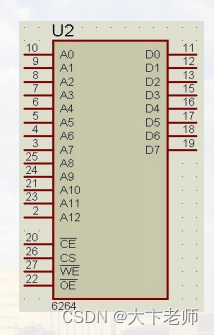

(6)、SRAM芯片6264(intel)

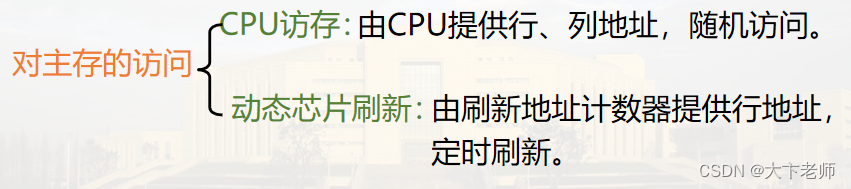

三.动态存储器的刷新

1、刷新定义与原因

定义:定期向电容补充电荷——刷新

原因:动态存储器依靠电容电荷存储信息。平时无电源供电,时间一长电容电荷会泄放,需定期向 电容补充电荷,以保持信息不变。

刷新与重写的区别:

刷新:动态存储芯片,需补充电荷以保持原来的信息。

重写:破坏性读出后重写,以恢复原来的信息。

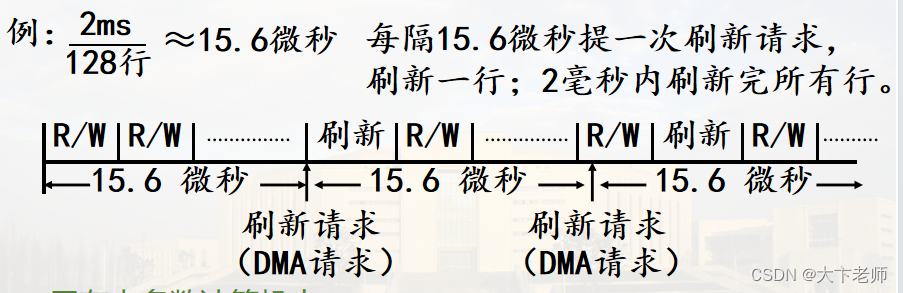

2、最大刷新间隔 2ms。在此期间,必须对所有动态单元刷新一遍。

3、刷新方法 :按行读。

刷新一行所用的时间——刷新周期(存取周期)

刷新一块芯片所需的刷新周期数由芯片矩阵的行数决定。

2、刷新周期的安排方式

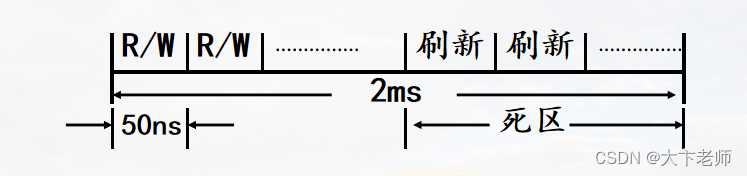

1)集中刷新 2ms内集中安排所有刷新周期。(用在实用要求不高的地方)

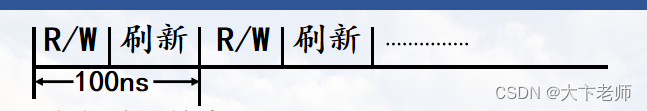

2)分散刷新 各刷新周期分散安排在存取周期中。(用在低速系统中)

3)异步刷新 各刷新周期分散安排在2ms内。每隔一段时间刷新一行(大多数的计算机使用)

四、主存储器的校验方法

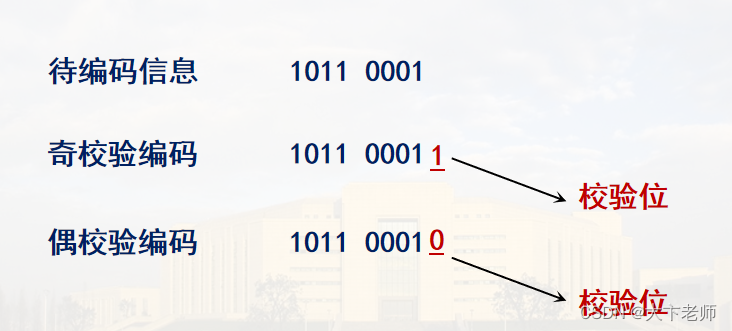

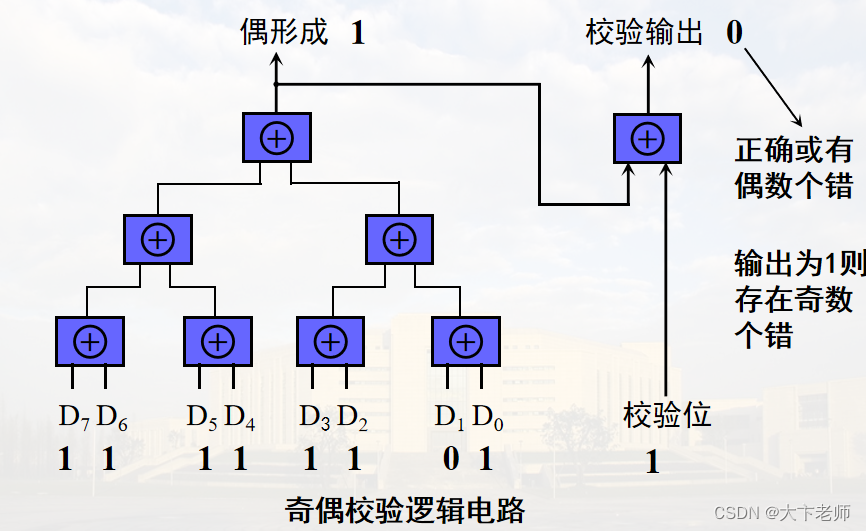

(1)奇偶校验示例

规则:编码中“1”的个数为奇数或偶数

(2)奇偶校验逻辑

由于学校不考磁表面存储器,所以我就不写啦。

本文详细探讨了主存储器的逻辑设计,包括寻址逻辑、DRAM中的动态刷新问题,以及与CPU的连接匹配。介绍了存储器的地址分配、驱动能力和时序配合,重点讨论了全译码、部分译码和线译码的不同译码方式,并涉及动态存储器的刷新机制和校验方法,如奇偶校验示例。

本文详细探讨了主存储器的逻辑设计,包括寻址逻辑、DRAM中的动态刷新问题,以及与CPU的连接匹配。介绍了存储器的地址分配、驱动能力和时序配合,重点讨论了全译码、部分译码和线译码的不同译码方式,并涉及动态存储器的刷新机制和校验方法,如奇偶校验示例。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?