一、DMA的核心思想

DMA(Direct Memory Access)即直接内存访问技术,其核心在于硬件子系统直接操作内存,无需CPU逐条指令控制。这一设计思想源于对系统效率的极致追求:

- 独立搬运数据:DMA控制器作为专用硬件单元,能在存储区域或外设间直接传输数据。类比而言,CPU如同忙于复杂工作的工程师,而DMA则是自动传送带,将数据"箱子"从源地址搬运到目标地址,解放CPU资源。

- 减少CPU开销:传统I/O方式中,CPU需通过中断或轮询逐字节处理数据,导致频繁中断和指令周期浪费。DMA仅需CPU初始化参数,后续由硬件自主完成传输,效率提升10-100倍。

二、DMA的工作方式

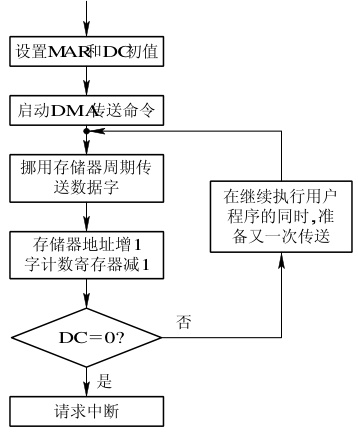

DMA工作流程分为三个阶段:预处理、数据传送、后处理。

-

预处理:

- CPU配置DMA控制器参数,包括传输方向(内存→外设或外设→内存)、源/目标地址、数据长度等。

- 示例代码片段(伪代码):

DMA->SourceAddress = src_addr; // 设置源地址 DMA->DestAddress = dest_addr; // 设置目标地址 DMA->DataLength = data_size; // 设置传输长度

-

数据传送:

- 外设触发DMA请求(DREQ信号),DMA控制器接管总线控制权(HRQ/HLDA信号),直接完成数据搬运。

- 传输过程中,CPU可继续执行其他任务,实现并行处理。

3. 后处理:

- DMA传输完成后,控制器通过中断通知CPU进行后续处理(如释放资源或启动下一次传输)。

流程图示例:

初始化参数 → 启动DMA → 传输数据 → 地址递增/计数器递减 → 完成中断

工作流程对比

| 传输方式 | CPU参与度 | 适用场景 | 传输效率 |

|---|---|---|---|

| 程序化I/O | 全程控制 | 小数据量传输 | 低 |

| 中断驱动I/O | 中断响应 | 中等数据量 | 中 |

| DMA | 仅初始化和结束 | 大批量高速数据传输 | 高 |

关键差异点

- 中断方式:需要保存/恢复现场,响应延迟大(需等待指令周期结束)

- DMA方式:总线请求可在任意机器周期响应,优先级高于中断

- 传输速率:DMA可达数百MB/s,比中断方式快10倍以上

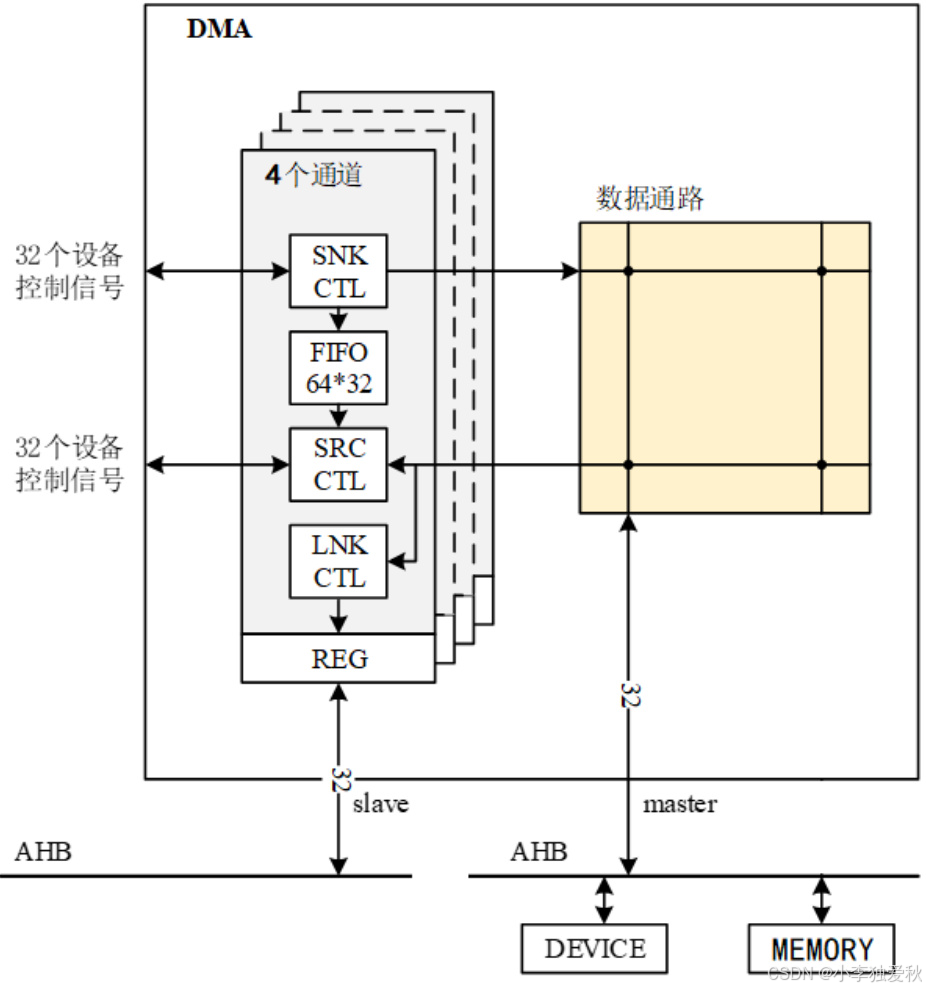

三、DMA控制器原理与模块构成

DMA控制器核心模块:

- 地址寄存器:存储源地址和目标地址。

- 计数器:记录剩余待传输数据长度。

- 控制逻辑单元:管理传输方向、模式(单次/循环)等信号。

- 状态寄存器:指示传输状态(完成、错误等)。

典型DMA模块框图:

+------------------+

| 控制逻辑 | ← DMA请求/响应信号

| 地址寄存器 | → 地址总线

| 数据寄存器 | ↔ 数据总线

| 计数器 | → 传输长度控制

+------------------+

功能说明:

- 总线仲裁:DMA控制器通过HRQ/HLDA与CPU协商总线使用权。

- 多通道支持:支持多个外设同时发起传输请求,优先级由硬件或软件配置。

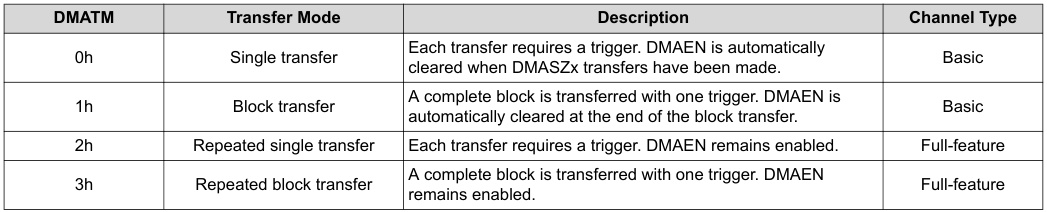

四、DMA数据搬运模式

- 单次传输(Single Mode) :完成指定长度传输后停止,适用于一次性任务。

- 循环传输(Circular Mode) :传输完成后自动重置地址和计数器,用于持续数据流(如音频采集)。

- 乒乓传输(Ping-Pong Mode) :双缓冲区交替读写,提升吞吐量(适用于实时处理)。

- 突发传输(Burst Mode) :一次传输多个连续数据块,减少总线切换开销。

模式选择建议:

- 小数据量:单次模式(DMA配置时间可能超过CPU搬运时间)。

- 大数据量/实时性要求:循环或乒乓模式。

| 模式 | 触发条件 | 应用场景 |

|---|---|---|

| 单次传输 | 每次传输需独立触发 | 小数据量实时传输 |

| 块传输 | 单触发完成整块数据传输 | 文件读写、图像处理 |

| 请求传输 | 外设持续请求时连续传输 | 高速ADC采样 |

| 循环传输 | 自动重置计数器重复传输 | 音频流缓冲、环形队列 |

例如,在音频播放中,DMA采用循环模式持续填充音频缓冲区,避免CPU频繁介入。

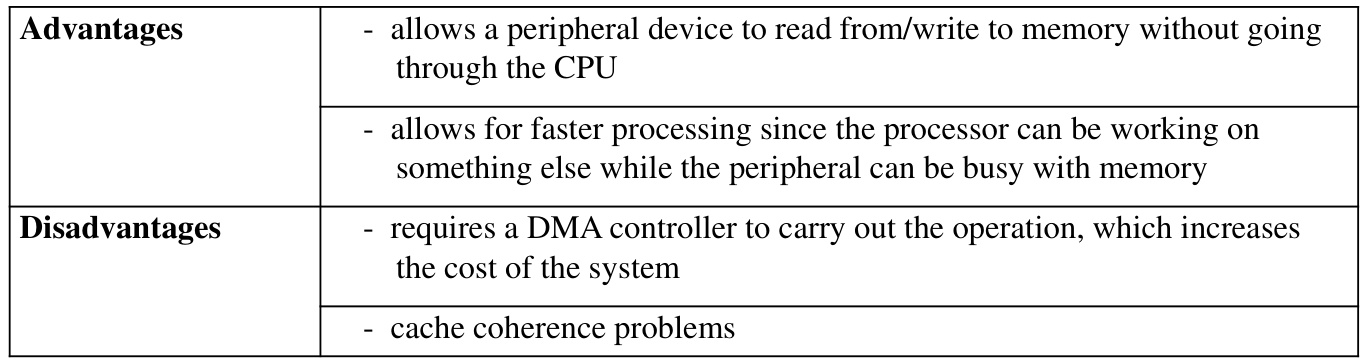

五、DMA的优缺点

| 优点 | 缺点 |

|---|---|

| 减少CPU负载,提升并行处理能力 | 需额外硬件支持,增加系统成本 |

| 支持高速数据传输(如视频流) | 配置复杂(需设置地址、长度等参数) |

| 降低功耗(CPU无需频繁中断) | 可能引发缓存一致性问题 |

六、DMA练习题精选

选择题:

1.DMA传输前需由谁设置参数?

A. CPU

B. 操作系统

C. 设备驱动

D. DMA控制器

答案:C。设备驱动负责初始化DMA寄存器。

2.下列关于DMA的叙述中,正确的是():

I. DMA传送前由设备驱动程序设置参数

II. DMA控制器需请求总线使用权

III. 数据传送由DMA控制器直接控制

IV. 传输完成后通过中断处理

答案:I、II、III、IV

3.采用DMA方式传送数据时,每传送一个数据需要占用( )

A. 指令周期

B. 总线周期

C. 存储周期

D. 机器周期

答案:B。DMA传输需要占用总线周期完成数据传输,CPU在此期间不能访问总线。

4.DMA初始化不包括()

A. 设置传输方向

B. 配置Cache策略

C. 指定数据块大小

D. 使能通道中断

答案:B(Cache管理由软件处理)

填空题:

- DMA传输的三个阶段是______、______、______。(预处理、数据传送、后处理)

- DMA控制器通过______信号向CPU申请总线控制权。(HRQ)

- 循环传输模式下,DMA传输完成后会______。(自动重置地址和计数器)

- DMA传输结束时通过______通知CPU。(中断)

- DMA控制器在传输时需要接管对____的控制权,数据直接在____与____间传输(总线,

内存,外设)

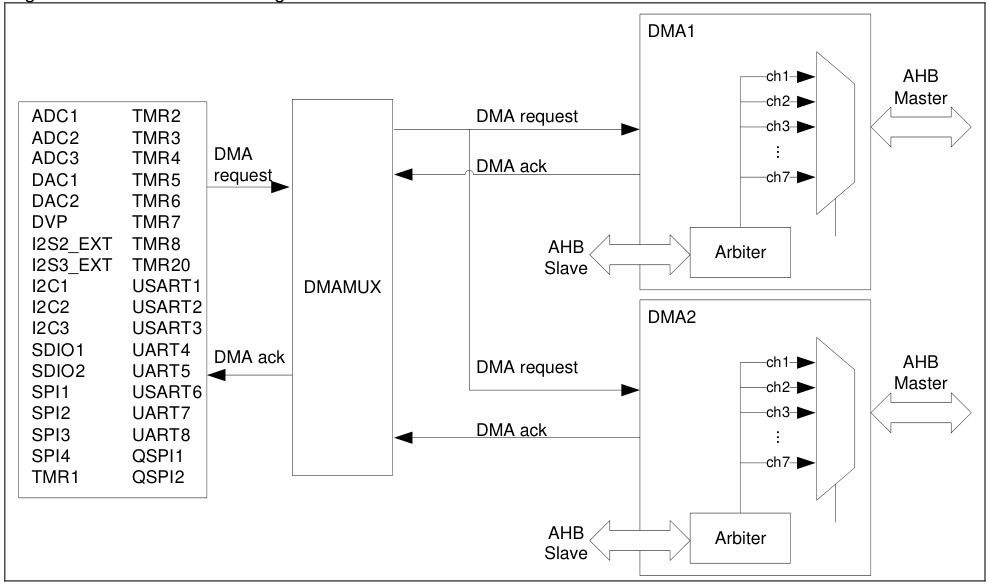

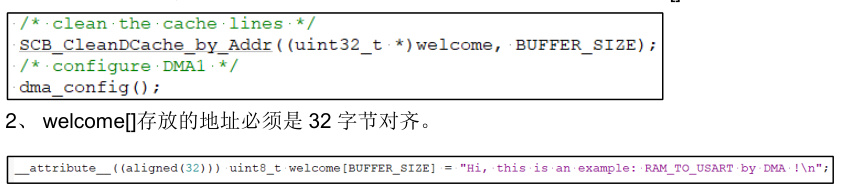

七、DMA编程实现(以STM32为例)

设计流程:

-

初始化DMA通道:

// 使能DMA时钟 RCC_AHBPeriphClockCmd(RCC_AHBPeriph_DMA1, ENABLE); // 配置DMA参数 DMA_InitTypeDef DMA_InitStruct; DMA_InitStruct.DMA_PeripheralBaseAddr = &USART1->DR; // 外设地址 DMA_InitStruct.DMA_MemoryBaseAddr = (uint32_t)buffer; // 内存地址 DMA_InitStruct.DMA_DIR = DMA_DIR_PeripheralSRC; // 传输方向 DMA_InitStruct.DMA_BufferSize = 256; // 数据长度 DMA_Init(DMA1_Channel4, &DMA_InitStruct); -

启动传输并处理中断:

// 使能传输完成中断 DMA_ITConfig(DMA1_Channel4, DMA_IT_TC, ENABLE); // 启动DMA DMA_Cmd(DMA1_Channel4, ENABLE); // 中断服务函数 void DMA1_Channel4_IRQHandler(void) { if (DMA_GetITStatus(DMA1_IT_TC4)) { // 处理传输完成逻辑 DMA_ClearITPendingBit(DMA1_IT_TC4); } }

核心代码说明:

- 外设与内存地址对齐:使用

__attribute__((aligned(32)))确保DMA高效访问。

- 中断机制:传输完成后触发中断,释放资源或启动下一轮传输。

结语

DMA技术通过硬件加速数据传输,在嵌入式系统、音视频处理等领域广泛应用。深入理解其原理和编程实现,有助于优化系统性能并应对复杂场景需求。

641

641

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?