引用b站大佬rong晔手册

1.使用门控时钟的原因:减少时钟网络的功耗消耗,最直接的办法就是如果不需要时钟的时候,就把时钟关掉。

2.门控时钟的结构:

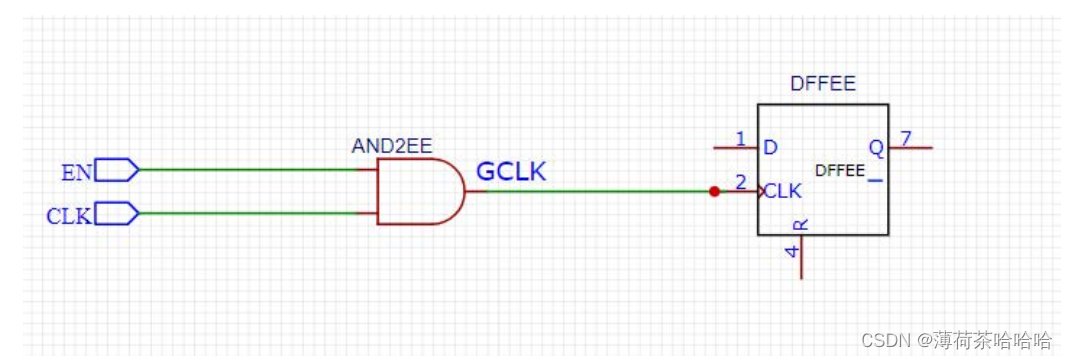

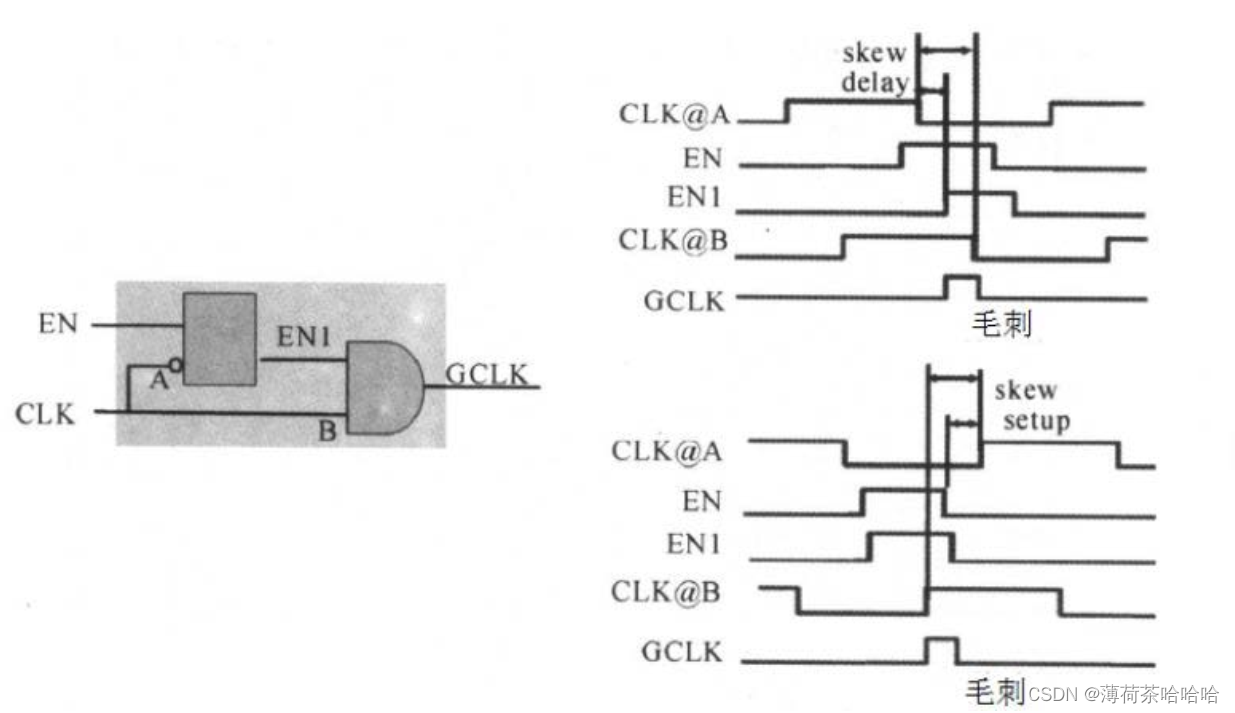

1)与门门控

这种直接将控制 EN 信号和时钟 CLK 进行与操作完成门控的方式,可以完成 EN 为 0 时,时钟被关掉。

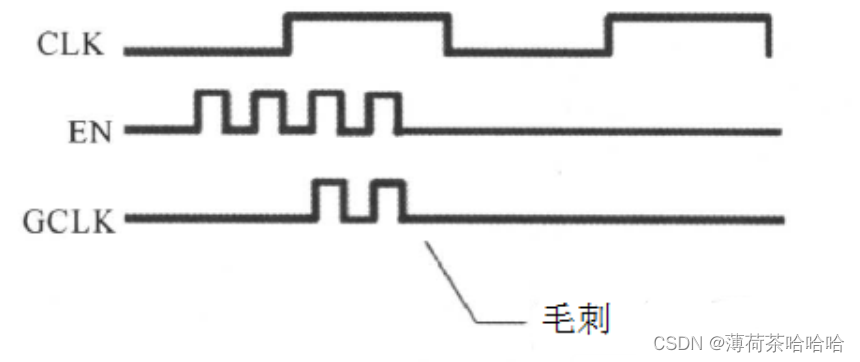

产生问题:毛刺

产生原因:如上图所示, EN 是不受控制的,随时可能跳变,这样纯组合输出 GCLK 就完全可能会有毛产生。时钟信号上产生毛刺是很危险的。实际中,这种直接与门的方式基本不会被采样。所以我们需要改进电路,为了使门控时钟不产生毛刺,我们必须对 EN 信号进行处理,使其在 CLK 的高低电平期间保持不变,或者说 EN 的变化就是以 CLK 为基准的。

解决方法:

1)只要把 EN 用 CLK 寄存一下,那么输出就是以 CLK 为基准

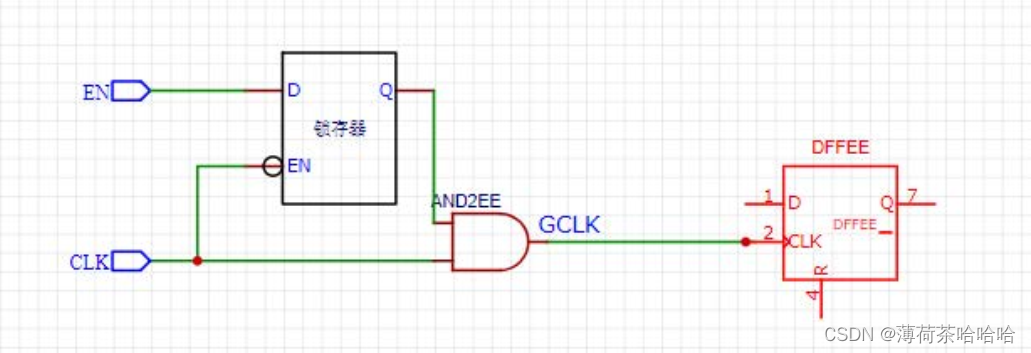

2)把 EN 用锁存器锁存的输出,也是以 CLK 为基准的。

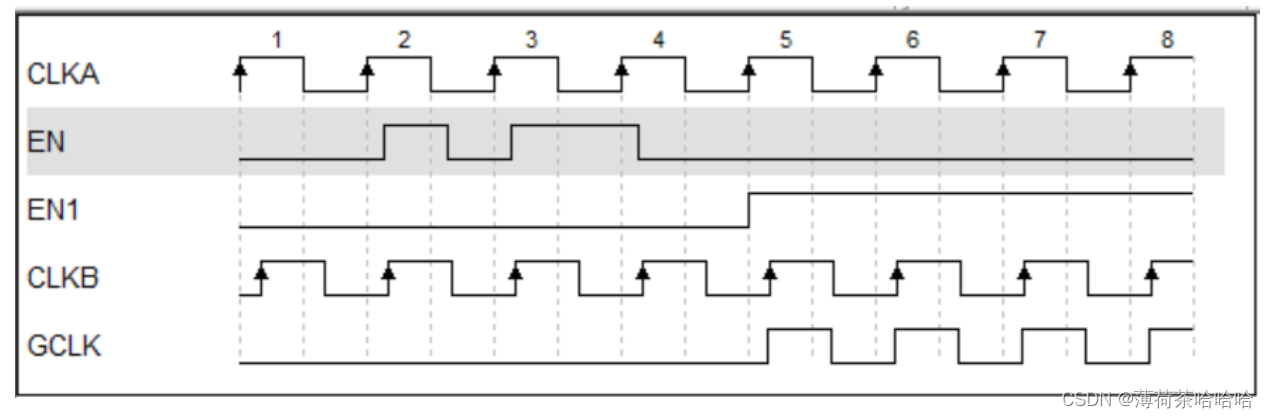

2)锁存门控

时序:

可以看到,只有在 CLK 为高的时候, GCLK 才可能会输出高,这样就能消除 EN 带来的毛刺。这是因为 D 锁存器是电平触发,在 clk=1 时,数据通过 D 锁存器流到了 Q;在 Clk=0 时,Q 保持原来的值不变。

虽然达到了我们消除毛刺的目的,但是这个电路还有两个缺点:

1 如果在电路中,锁存器与与门相隔很远,到达锁存器的时钟与到达与门的时钟有较大的延迟差别,则仍会出现毛刺。

2 如果在电路中,时钟使能信号距离锁存器很近,可能会不满足锁存器的建立时间,会造成锁存器输出出现亚稳态。

缺点时序图:

分析:上述的右上图中, B 点的时钟比 A 时钟迟到,并且 Skew > delay,这种情况下,产生了毛刺。

为了消除毛刺,要控制 Clock Skew,使它满足 Skew >Latch delay(也就是锁存器的 clk-q 的延时)。(这里消除应该是skew<delay吧)

上述的右下图中, B 点的时钟比 A 时钟早到,并且|Skew| > ENsetup 一 (D->Q),这种情况下,也产生了毛刺。为了消除毛刺,要控制 Clock Skew,使它满足|Skew|< ENsetup一(D->Q)。

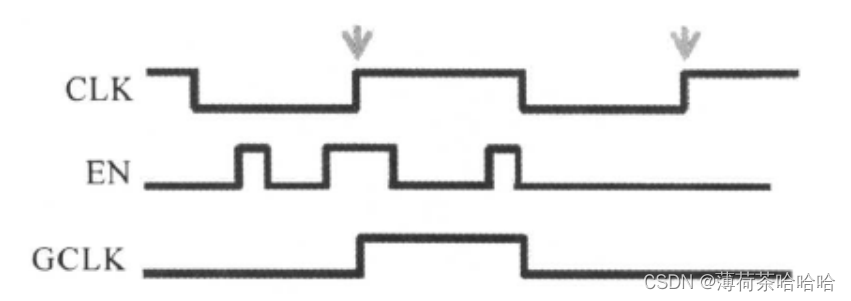

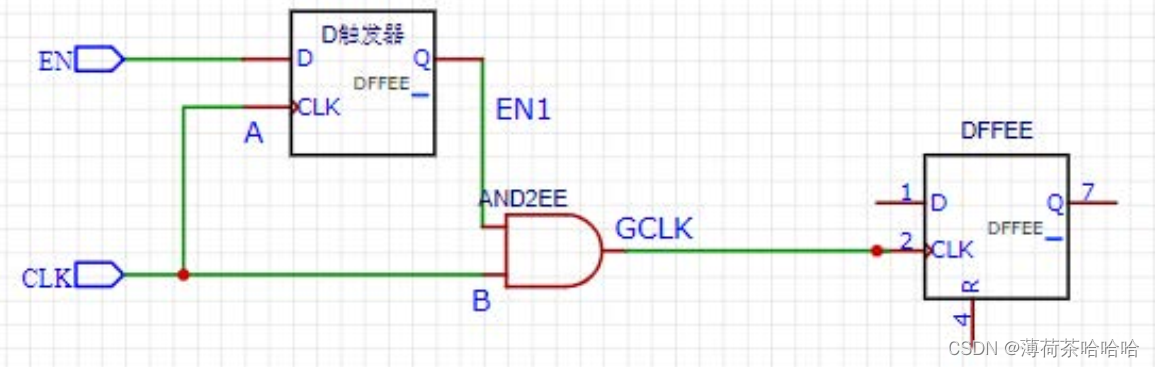

3) 寄存门控

如 1.1 中提到的,我们还有另外的解决办法,就是用寄存器来寄存 EN 信号再与上 CLK 得到

GCLK,电路图如下所示:

时序:

分析:由于 DFF 输出会 delay 一个周期,所以除非 CLKB 上升沿提前 CLKA 很多,快半个周期,才会出现毛刺,而这种情况一般很难发生。但是,这种情况 CLKB 比 CLKA 迟到,是不会出现

毛刺的。

当然,如果第一个 D 触发器不能满足 setup 时间,还是有可能产生亚稳态。

4)总结

SOC 芯片设计中使用最多的是锁存结构的门控时钟:

原因:在实际的 SOC 芯片中,要使用大量的门控时钟单元。所以通常会把门控时钟做出一个标准单元,有工艺厂商提供。那么锁存器结构中线延时带来的问题就不存在了,因为是做成一个单元,线延时是可控和不变的。而且也可以通过挑选锁存器和增加延时,总是能满足锁存器的建立时间,这样通过工艺厂预先把门控时钟做出标准单元,这些问题都解决了。

不用寄存门控时钟的原因:

那么用寄存器结构也可以达到这种效果,为什么不用寄存器结构呢?那是因为面积!一个

DFF 是由两个 D 锁存器组成的,采样 D 锁存器组成门控时钟单元,可以节省一个锁存器的

面积。当大量的门控时钟插入到 SOC 芯片中时,这个节省的面积就相当可观了。所谓门控时钟就是指连接触发器时钟端来自于组合逻辑,凡是组合逻辑在布局布线之后肯定会产生毛刺,而如果采用这种有毛刺的信号来作为时钟使用的话将会出现功能上的错误。

门控时钟技术用于降低功耗,主要通过与门或锁存器结构实现。然而,直接使用与门可能导致毛刺,锁存器结构则能消除毛刺但可能面临时序问题。寄存门控通过DFF避免毛刺,但可能产生亚稳态。在SOC设计中,锁存结构因面积效率和预设时序优化成为首选。

门控时钟技术用于降低功耗,主要通过与门或锁存器结构实现。然而,直接使用与门可能导致毛刺,锁存器结构则能消除毛刺但可能面临时序问题。寄存门控通过DFF避免毛刺,但可能产生亚稳态。在SOC设计中,锁存结构因面积效率和预设时序优化成为首选。

914

914

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?