多端口Cache设计

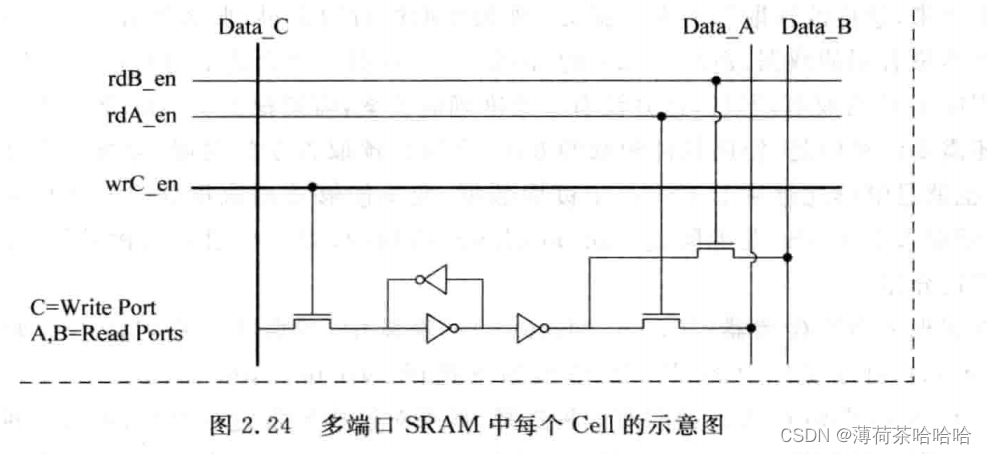

1. 使用True Multi-port

需要有两套地址解码器,使得两个端口可以同事寻址Tag和Data, 使用两个多路选择器去读取两个端口的数据,比较器数量*2进而判断两个端口的命中情况,需要两个对齐器Aligner,完成字节或半字的读取,Tag SRAM和Data SRAM本身不需要复制,但是每个cell需要同时支持两个并行的读取操作。

增大了电路面积,多端口SRAM Cell的驱动需要更长的访问时间,功耗也会增大。

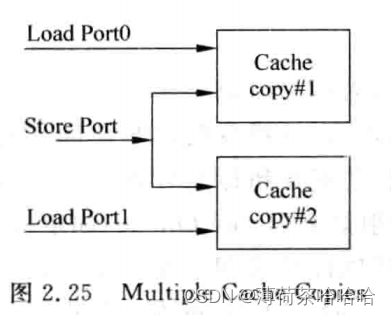

2.使用Mulitple Cache Copies

通过将Cahe复制,SRAM不需要再使用多端口的结构,消除对处理器周期时间的影响。

浪费面积,需要保持两个Cache之间的同步(非常麻烦)

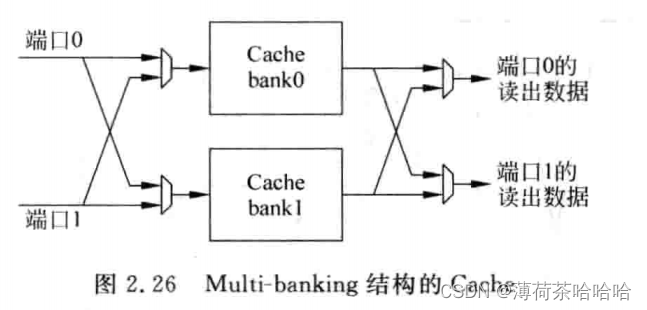

3. Multi-banking

在现实中广泛使用的方法,将Cache分为很多小的bank,每个bank之间只有一个端口。

如果一个周期之内Cache多个端口上的访问地址位于不同的bank之中,就不会引起任何问题。

若两个或多个端口的地址位于同一个bank,会以后引起bank conflict冲突,需要使用Multi-banking

一个双端口的Cache需要两个地址解码器,两个Way Mux,两个比较器和一个对其器Aligner,但是Data SRAM不需要实现多端口结构,进而提升速度减小面积。

在周期不能同时让端口0和端口1都访问同一个Cache bank,若两个端口同时访问Bank1,当前周期Cache只能对一个端口进行响应。

影响多端口Cache性能的关键因素就是bank冲突,采用更多的bank可以缓解这个问题,使得bank冲突发生的概率尽可能降低,提高bank的利用效率,避免有用的数据都集中在一个bank的情况(可能需要编译器的配合才可以实现)

每次会访问不同路的bank,然后通过比较Tag,从一个way中选择出来。

551

551

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?