文章目录

指令集

CISC复杂指令集

- x86指令集基本特色:

1,向下兼容

2,变长指令:1-15字节,多为2-3字节

3,多种寻址方式(可访问不对齐内存地址)

4,指令集的通用寄存器个数有限:

(32位系统有8个,64位扩展到16个)

5,至多只有一个操作数在内存中,另一个操作数为立即数或者寄存器 - x86指令集的缺点:

1,向下兼容导致指令集越来越大,越复杂

2,类RISC内核,采用micro-op模式进行翻译,使得功耗相对增大,这导致其在注重低功耗领域不易占优势

3,对很多领域而言,资源利用率低(在高性能计算领域,300余条x86指令中,大致只有80余条是被科学计算所需要的)

RISC精简指令集

-

MIPS指令集

1,MIPS Ⅰ、MIPS Ⅱ、MIPS Ⅲ、MIPS Ⅳ、到MIPS Ⅴ,嵌入式指令体系MIPS16、MIPS32到MIPS64的发展已经十分成熟

2,为充分利用处理器的流水线结构,其设计思想是使得各个指令的流水线分段较为均匀(分段一致,每段的操作时延相差不多,以提高主频)

3,尽量利用软件办法避免流水线中的数据相关/控制相关问题(实例:Branch Delay Slot)

4,以寄存器位中心(32个),只有Load/Store指令访问内存,所有的计算类型的指令均从寄存器堆中读取数据并把结果写入寄存器中(MIPS还定义了32个浮点寄存器)

5,MIPS32指令集的指令格式非常规整,所有的指令长度一样,而且指令操作码在固定的位置上

6,MIPS指令的寻址方式非常简单,每条指令的操作也较简单 -

MIPS32(TM)的指令格式只有3种:

1,R(register)类型的指令从寄存器堆中读取两个源操作数,计算结果写回寄存器堆

2,I(immediate)类型的指令使用一个16位的立即数作为源操作数

3,J(jump)类型的指令使用一个26位立即数作为跳转的目标地址(target address) -

Load和Store指令都位立即数(I-type)类型,用来在存储器和通用寄存器之间的存储和装载数据。MIPS指令集只有该类指令能访问内存,而其他指令操作寄存器

该类指令只有基址寄存器的值加上扩展的16位有符号立即数一种寻址模式,数据的存储方式可以时字节(Byte)、字(word)、和双字(Double word) -

MIPS扩展指令集:

MIPS-3D,浮点SIMD用于三维几何处理(MIPS64架构下)

采用MIPS64浮点运算单元和双单精度数据类型:

PS(paired-single,双单精度)操作可对64位寄存器中的两个32位浮点值进行运算,从而提供2路SIMD(单指令多数据)能力。 -

ARM指令集:

1,ARM指令完成简单的操作,编译器或者程序员通过几条简单指令的组合来实现一个复杂的操作

2,ARM指令集大多数指令采用相同的字节长度,并且在字边界上对齐,字段位置固定,特别是操作码的位置

3,使用Load/Store的存储模式,只有Load和Store指令才能从内存中读取数据到寄存器,所有的其他指令只对寄存器中的操作数进行处理。(16个32位寄存器以及1个the current program status register(User mode))

4,大多数指令具有“条件执行”模式

5,具有16位压缩指令集(Thumb) -

ARM的Thumb指令集(16位):

1,Thumb指令可以看做是ARM指令的压缩形式子集,为提高代码密度而引入

2,与ARM指令集混合使用(BX指令)

主要区别:

除了条件跳转指令外,其它指令均为无条件执行

没有乘加指令及64位乘法指令等,且指令的第二操作数受到限制

指令编码不如32位版本的规整

CISC和RISC的联系、区别及发展:

CISC和RISC两种指令集越来越趋于融合。

两者明显的区别:RISC只能通过Load和Store指令访问内存,CISC则不受限。

兼容性考虑是指令集发展的关键性因素

数的机器表示

机器字(machine word)长

一般指计算机进行一次整数运算所能处理的二进制数据的位数,通常也包括数据地址长度

32位字长

地址的表示空间是4GB

对内存需求量大的应用而言,非常有限

64位字长

地址的表示空间是1.8x10的19次方bytes

目前的x86-64机型实际支持48位宽的地址:256TB

机器字在内存中的组织

- 地址按照字节(byte)来定位

机器字中第一个字节的地址

相邻机器字的地址相差4(32-bit)或者8(64-bit)

整数表示:

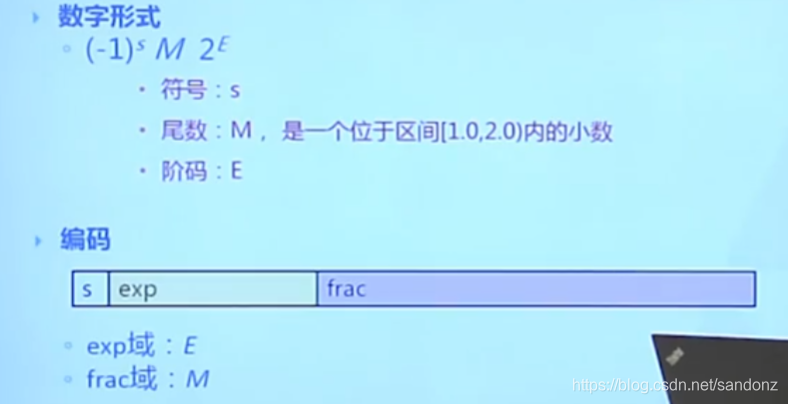

浮点数表示

- 符号(sign)——s决定这个数是负数(s=1)还是正数(s=0),而对于数值0的符号位解释,作为特殊情况处理;

- 尾数(significand)——M决定浮点数的精度,它是一个二进制小数;

- 阶码(exponent)——E的作用是对浮点数加权,这个权重是2的E次幂(可能是负数),它决定浮点数的取值范围。

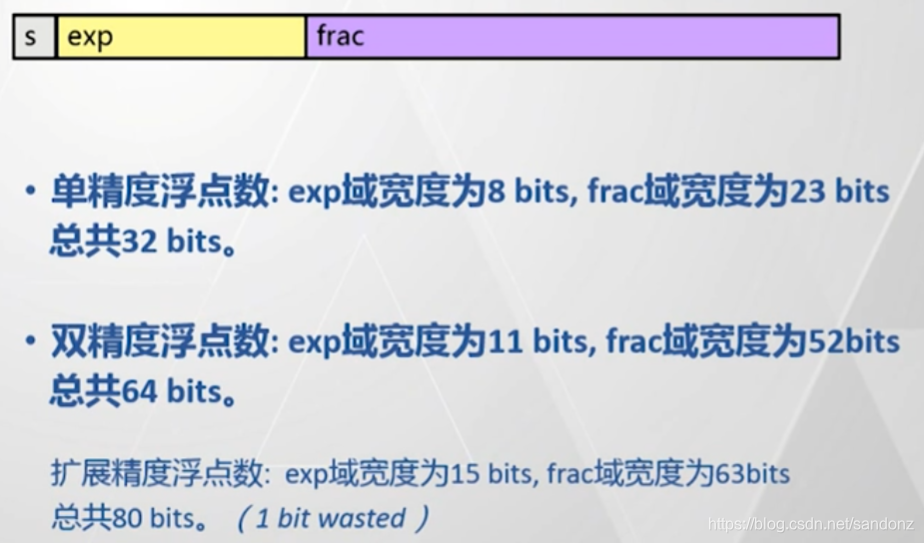

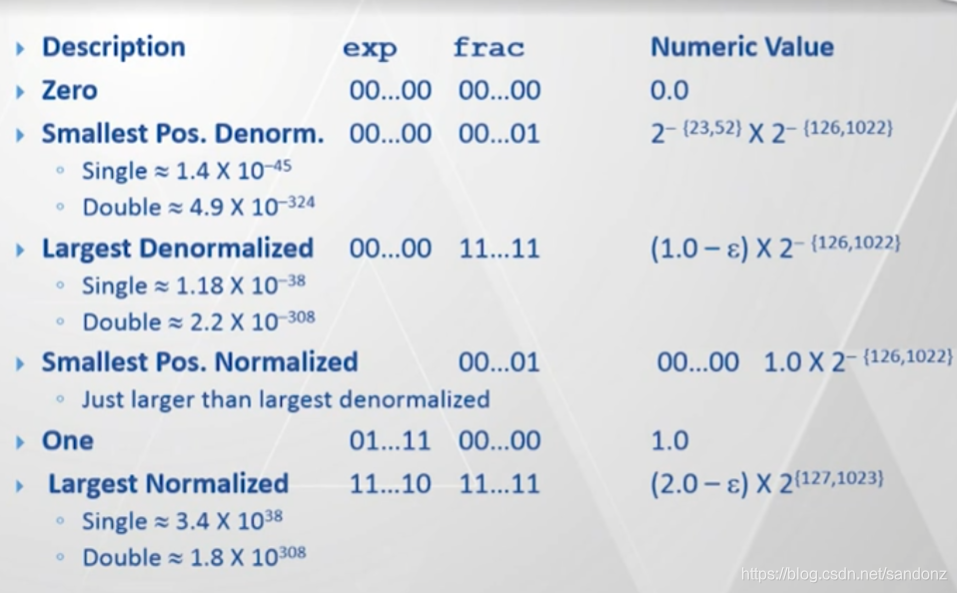

- 对于双精度double,组成形式是:1位符号,11位阶码,52位尾数。

- 对于单精度float,组成形式是:1位符号,8位阶码,23位尾数。

浮点数编码

IEEE 754标准浮点数类型

-

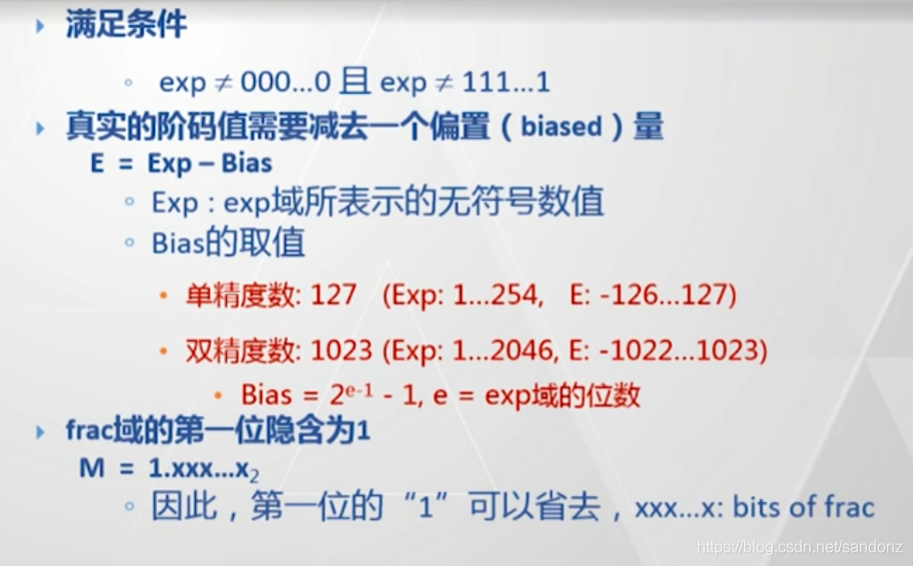

1,规格化浮点数

机器内部是以无符号存储,所以真实的阶码需要减去一个偏置(biased)量 -

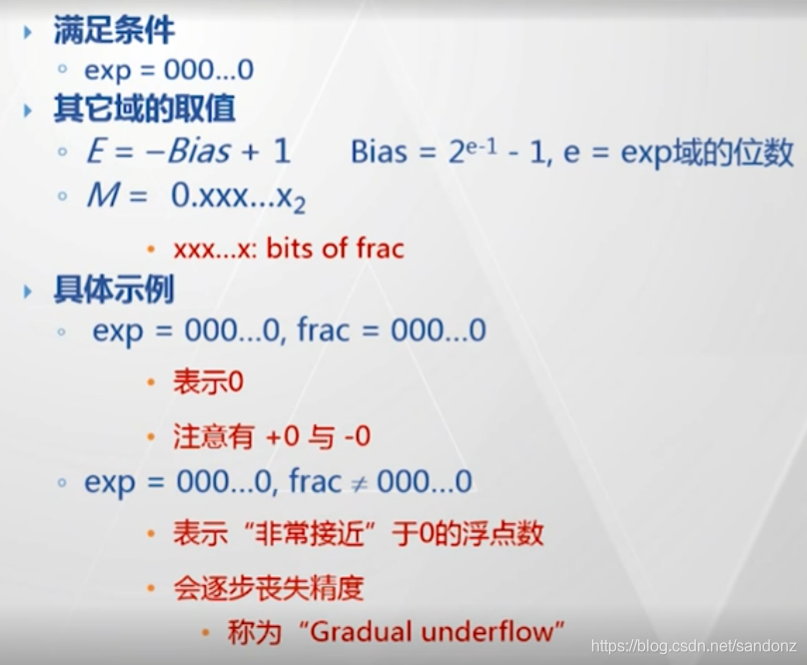

2,非规格化浮点数

-

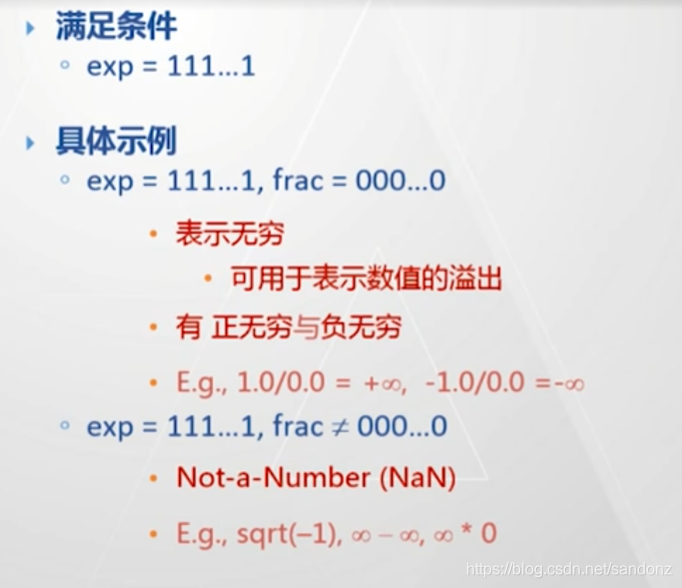

3,一些特殊值

-

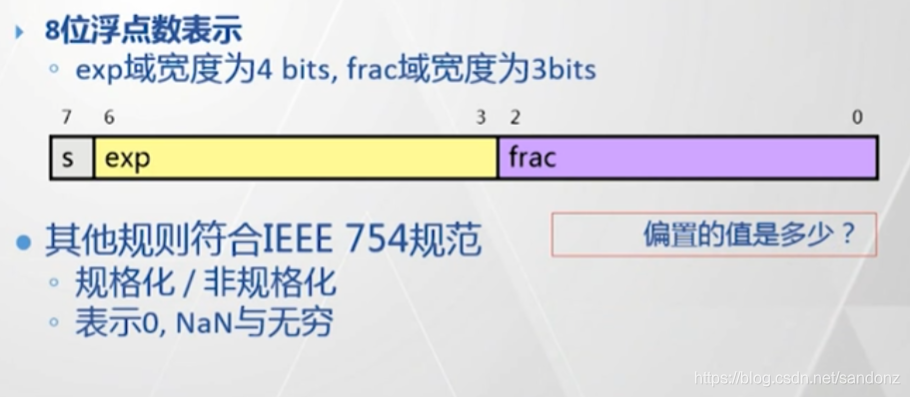

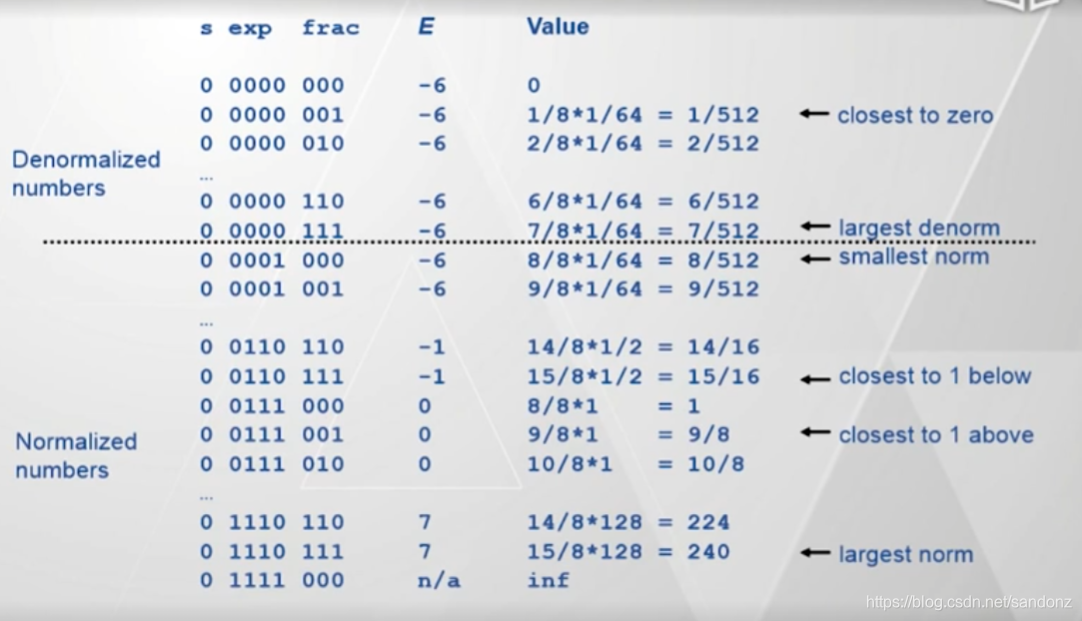

一种“小”的浮点数实例

一些特例

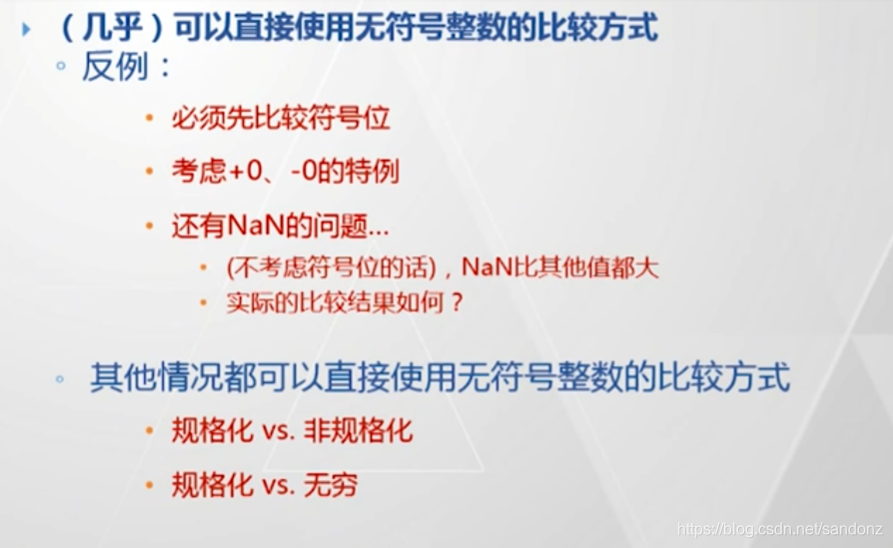

浮点数编码特性

实数的浮点数表示

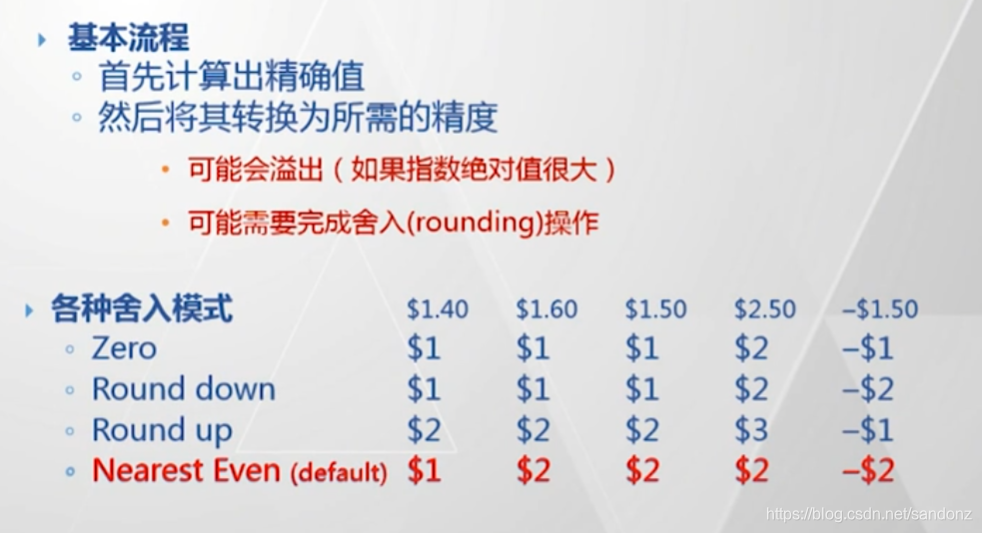

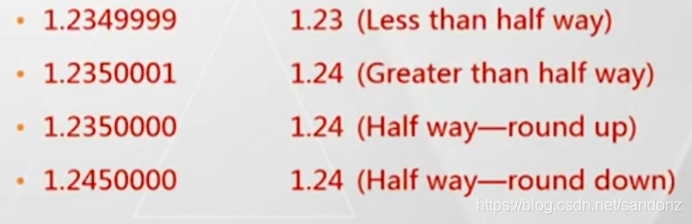

向偶数舍入(Round-To-Even)

1,十进制下,四舍五入

- 这是计算机内默认的舍入方式,也称为“向最接近值的舍入”

其它方式会产生系统误差(statistically biased) - 关键的设计决策是确定两个可能结果的中间数值的舍入

确保舍入后的最低有效数字是偶数

E.g.,round to nearest hundredth

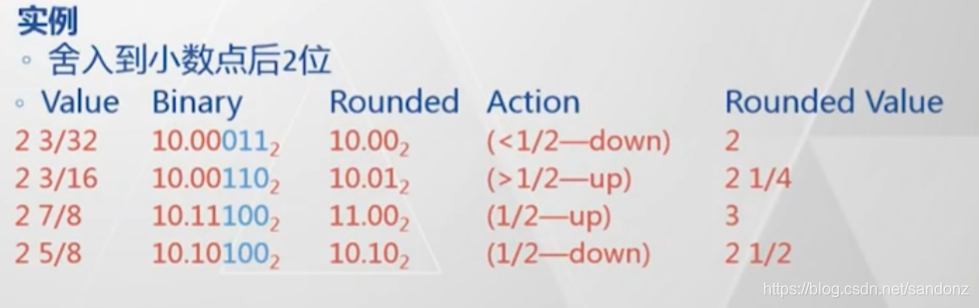

2,对二进制而言 - “Even”意味着最低有效数字需为0

- 而最低有效数字右侧的位串为100

具体步骤:

- 将数值规格化(前导1)

- 舍入(round to even)以便符合尾数的位数需求

- 后调整

二进制编码方式

- 无符号数:原码表示

范围:0 ~(2的n次方 -1),n表示字长 - 带符号数:最高位为符号位

正数:原码表示

负数:补码表示(绝对值的反码加1)

范围:- (2的n-1次方)~ +(2的n-1次方 - 1),n表示字长

在硬件层面,无符号数与带符号数之间的转换:二进制串的表示是不变的。

本文深入探讨了CISC和RISC指令集的特点,如x86的复杂指令集和MIPS的精简指令集。同时,详细介绍了数的机器表示,包括机器字长、浮点数的IEEE 754标准以及二进制编码方式。此外,还讨论了80X86处理器的保护模式、汇编语言与C语言的交互,以及程序运行栈的基本操作,如栈帧和递归调用。最后,讲解了数组和结构在内存中的存储和访问方式。

本文深入探讨了CISC和RISC指令集的特点,如x86的复杂指令集和MIPS的精简指令集。同时,详细介绍了数的机器表示,包括机器字长、浮点数的IEEE 754标准以及二进制编码方式。此外,还讨论了80X86处理器的保护模式、汇编语言与C语言的交互,以及程序运行栈的基本操作,如栈帧和递归调用。最后,讲解了数组和结构在内存中的存储和访问方式。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?