3 DDR SDRAM 介绍及其应用要点

1. DDR SDRAM 的技术更新及其与 SDRAM 的比较

DDR 指双倍速率(Double Data Rate),DDR SDRAM 与 SDRAM 的基本结构是相似的,最根本的区别在于 DDR SDRAM 支持在一个时钟周期内传输两次数据,这是通过接口结构的改进而实现的。

相对 SDRAM,DDR SDRAM 在技术上的更新有以下几项。

1)数据预取方式

DDR SDRAM 采用 2 倍预取架构,即芯片内部能以两倍于时钟运行的速率预取数据,从而使得芯片内核工作速率仅为外部数据传输速率的一半。SDRAM 采用 1 倍预取架构,即芯片内核工作速率与外部数据传输速率相同。

内核工作速率越高,芯片工艺越复杂,基于这种工艺的限制,不可能快速地提高芯片内核工作速率。在相同的内核工作速率下,DDR SDRAM 的外部数据传输速率为 SDRAM 的两倍,从而提高了存储器的传输效率。

例如,在 DDR SDRAM 和 SDRAM 的外部数据传输速率都为 400Mbps 的情况下,对于 DDR SDRAM,其内核工作速率仅需为 200MHz,而对于 SDRAM,其内核工作速率需要为 400MHz。目前,无法在技术上实现如此高的内核频率,因而 SDRAM 的数据传输速率无法达到 400Mbps。

利用这项技术,DDR SDRAM 可以在不提高内核工作速率的前提下(即无需对芯片做大的技术革新),大大提高外部数据传输速率,从而获得更高的性能。值得一提的是,后续章节将要提到的 DDR2 SDRAM 以及新推出的 DDR3 SDRAM 技术,其数据传输速率比 DDR SDRAM 又有大幅度提高,这种提高并不是源于技术上的巨大变革,而是因为分别采用了 4 倍和 8 倍数据预取技术。

2)信号电平

为提高信号完整性,DDR SDRAM 采用 SSTL-2(Sub Series Terminated Logic for 2.5V)电平,SSTL-2 是由 JEDEC 制定的专用于存储器接口的电平。

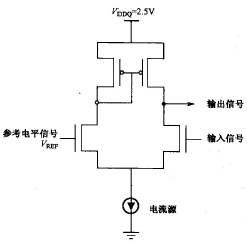

从芯片引脚上看,DDR SDRAM 的信号大多是单端信号,但本质上却都属于差分对。SSTL 电平的实现机制在于,将普通信号与参考电平 VREF 组合成差分对,如下图所示,信号逻辑状态参考电平为 VREF,而不再是 GND,高电平逻辑和低电平逻辑相对参考电平对称分布,有利于噪声量的提高和电压摆幅的减小。同时,差分对的结构也有利于信号温度稳定性的提高。

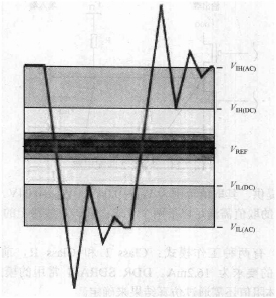

SSTL-2 电平的输入门限定义如下图所示。

其中,VIH 和 VIL 分别为输入逻辑高电平和低电平门限值,它们各有一个交流参数 AC 和一个直流参数 DC。信号沿第一次通过 AC 门限的时刻,是计算建立时间和保持时间的参考点,此后,只要信号不翻越 DC 门限,则逻辑状态将得到保持。以上升沿为例,当信号电平第一次超越 VIH(AC),表示信号已翻转为高电平,这一时刻用于计算信号的建立时间,此后,不论信号纹波有多大,只要信号电平不低于 VIL(DC),则信号将稳定于逻辑高电平上。这样,利用交流参数和直流参数共同定义逻辑高、低电平,有利于减小信号过冲、振铃、噪声等干扰对逻辑电平判决的影响。

根据 SSTL-2 标准规范,各个门限电平的定义为:

VIH(AC) = VREF + 0.31

VIH(DC) = VREF + 0.15

VIL(AC) = VREF - 0.31

VIL(DC) = VREF - 0.15

对于 DDR SDRAM,当 VREF=1.25V 时,有 VIH(AC)=1.56V,VIH(DC)=1.40V,VIL(AC) = 0.94V,VIL(DC)=1.10V。

推荐 VREF 的取值范围为 0.49×VDDQ~0.51×VDDQ;其中,VDDQ 为 DDR SDRAM 数据总线 I/O 接口的电源,其推荐取值范围为 2.3~2.7V。

DDR SDRAM 的时钟信号 CK/CK#为 SSTL-2 电平的差分对,以其边沿交叉点作为时序参考点,而不像 SDRAM 那样采用 CLK 信号的中间电平 1.5V 作为时序参考点,这有利于减小时钟信号抖动对时序的影响。

以下继续介绍 SSTL-2 的匹配方式。

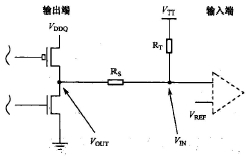

如下图所示是标准的 SSTL-2 匹配电路图。Rs 为始端匹配电阻,Rr 为终端匹配电阻,上拉到 VTT 电平。

VTT 需由外部电源提供,其取值范围为 VREF-0.04V~VREF+0.04V。

Rs 和 Rr 匹配电阻的取值需满足以下两个要求:其一,线路上的阻抗匹配;其二,线路上电流的要求。

对 SSTL-2 电平,有两种工作模式:Class I 和 Class II,前者线路电流的要求为 8.1mA,后者线路电流的要求为 16.2mA。DDR SDRAM 常用的模式是 Class II,一般取 Rs=25Ω,Rr=50Ω,其值还需通过仿真结果来确定。

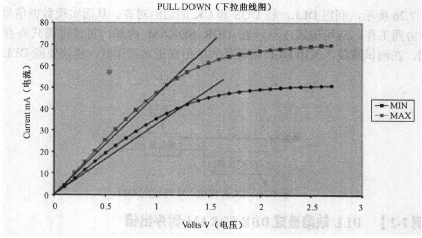

在确定 Rs 值的过程中,需得到驱动器的输出阻抗参数,该参数可以从驱动器 IBIS 模型的 dV/dI 曲线得到,如下图所示,驱动器输出阻抗的值在 21~28Ω 之间,且该输出阻抗随着信号电平的变化而变化,在端端添加串联匹配电阻 Rs 有利于减小该影响。

驱动器输出阻抗小,驱动能力越强。

在该操作时,途中的匹配方式对双向信号如 DQ、DQS 的信号质量存在一定的影响,但该问题在 DDR2 SDRAM 已经得到解决。

3)数据信号采样参考源

与 SDRAM 不同,DDR SDRAM 不再依靠时钟信号 CK/CK#实现对数据信号 DQ 的采样,而是采用了与 DQ 同步的信号 DQS(数据选通信号,Data Strobe)作为采样参考源。

DQS 是双向信号,传输方向与 DQ 相同。写操作时,由存储器控制器发往存储器,DQS 的边沿与 DQ 的中央对齐,在接收端的存储器,直接利用 DQS 的边沿对 DQ 采样,读操作时,由存储器发往存储器控制器,DQS 的边沿与 DQ 的边沿对齐,在接收端的存储器控制器内部,对 DQS 偏移 1/4 个时钟周期后,使用其边沿对 DQ 采样。一般,一个 DQS 与八个 DQ 配合使用,对于位宽为 16 位的 DDR SDRAM,芯片上提供了两个 DQS 信号,分别为 UDQS 和 LDQS。其中,UDQS 与 DQ[15:8]构成一组,LDQS 与 DQ[7:0]构成一组。需注意的是,在许多存储器控制器内部,有相应寄存器以设置 DQS 的偏移量,调试电路时,不能忽略对这些寄存器的设置。

为何要增加 DQS,而不直接采用 CK/CK#作为数据信号的采样参考源?原因有三:其一,CK/CK#是单向信号,其方向是由存储器控制器发往存储器,而 DQ 为双向信号,在由存储器发往存储器控制器的方向上,无法直接采用 CK/CK#作为采样参考源;其二,CK/CK#主要用于单边沿信号如地址、控制信号的采样,不适合用于双边沿信号 DQ 的采样;其三,SDRAM 和 DDR SDRAM 的数据信号都属于双向信号,前者属于普通同步时序,而后者属于源同步时序(请参考第 5 章),SDRAM 的数据传输率低,可以采用普通同步时序,而 DDR SDRAM 的数据传输率高,时序裕量小,需采用源同步时序以保证充裕的时序裕量。

因此,对 DDR SDRAM 而言,地址信号、控制信号等单向信号仍采用 CK/CK#采样(CK 的上升沿和 CK#的下降沿交叉点为时序参考点),而数据信号 DQ 则使用其同步信号 DQS 采样。需注意,DDR SDRAM 的地址信号、控制信号仍为单边沿信号,只有 DQ、DM 和 DQS 为双边沿信号。

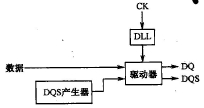

综上所述,看起来数据信号 DQ 与时钟信号 CK/CK#没有任何时序上的关系,那么如何保证数据信号与地址、控制信号的协同工作?这可通过存储器内部的 DLL(延迟锁相环)实现,关于 DLL 的知识,请参考之前章节。

如下图 所示,利用 DLL,将 DQS 和 CK 的边沿对齐,从而实现数据信号和地址、控制信号的协同工作。应用中需注意,在 DDR SDRAM 内部,可通过模式寄存器的配置将 DLL 关闭,在测试阶段,关闭 DLL 是可行的,但在正常工作时,建议使能 DLL。

【案例2】DLL 缺陷造成 DDR SDRAM 时序出错

某单板设计中,使用 DDR SDRAM 作为数据包的缓存器,FPGA 作为存储器控制器。测试中,发现经缓存后的数据包经常出错。

【讨论】

测量 DDR SDRAM 的时序,发现在某些时候,DQS 和 DQ 时序关系不正确。在 PCB 设计时,DQS 和 DQ 信号走线等长,读操作时,DQS 的延时在 FPGA 内部实现。经逻辑工程师确认,该 FPGA 的逻辑设计已在其他单板上得到验证,因此问题很可能出现在电路设计上。

根据 DDR SDRAM 的器件资料,对 CK 和 DQS 之间的时序关系有如下要求:

tDSH:DQS 相对 CK 的保持时间,最小值要求为 0.2ns。

tDSS:DQS 相对 CK 的建立时间,最小值要求为 0.2ns。

经测试,DQS 相对 CK 的时序很大,可初步定位为 FPGA 内部 DLL 工作不稳定。经测量,发现为 FPGA 内部 DLL 供电的电源引脚上的纹波较大,在 PCB 上,该引脚附近只有一颗 4.7 μF 的陶瓷电容,且距离较远。

在改板设计中,增加一颗 0.1μF 的陶瓷电容,紧贴 DLL 电源引脚放置,同时将 4.7 μF 陶瓷电容靠近电源引脚,问题得到解决。

4)功耗

SDRAM 采用 3.3V 的 LVTTL 电平,而 DDR SDRAM 采用 2.5V 的 SSTL-2 电平,相对于 SDRAM,功耗更小。

5)总结

在硬件电路设计上,DDR SDRAM 与 SDRAM 的不同点,可总结如下:

区别一,时钟信号。SDRAM 的时钟信号 CLK 为单端信号,而 DDR SDRAM 则采用差分对时钟信号 CK/CK#。

区别二,信号电平。SDRAM 采用 LVTTL 电平,接口信号为单端信号,而 DDR SDRAM 采用 SSTL-2 电平,接口信号本质上属于差分对。

区别三,电源。两种存储器的电源引脚都分为 VDD 和 VDDQ,一般这两种引脚均可采用同一电源供电,但 SDRAM 的电源为 3.3V,而 DDR SDRAM 的电源为 2.5V。

区别四,电源种类。SDRAM 仅需 3.3V 一种电源,而 DDR SDRAM 需三种电源:给 VDD 和 VDDQ 供电的 2.5V,给 VREF 供电的 1.25V,以及给 SSTL-2 终结电路供电的 VTT 电源 1.25V,关于 DDR SDRAM 的电源电路设计,将在下文讨论。

区别五,时序测试。对地址信号、控制信号,SDRAM 和 DDR SDRAM 的时序测试方法相同,对数据信号,SDRAM 为单边沿采样,DDR SDRAM 为双边沿采样,且时序参考信号为 DQS 而不是时钟信号。

区别六,输出信号驱动能力。DDR SDRAM 输出信号的驱动能力可被设置为强驱动或弱驱动两种模式,SDRAM 则不能设置。在设计中,某些存储器控制器对 DDR SDRAM 的输出驱动能力有要求,应相应地对存储器的寄存器进行配置。

2. DDR SDRAM 基本操作

DDR SDRAM 的操作方式与 SDRAM 基本相同,此处仅简要介绍某些关键的操作。

1)读操作

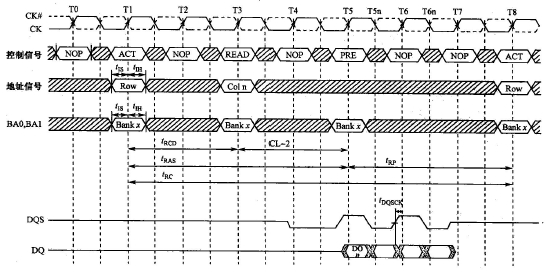

如下图所示为 DDR SDRAM 读操作时序图。

DDR SDRAM 的延时参数如 tRCD、tRAS、tRC、tRP,它们的定义与 SDRAM 相同。地址信号和控制信号的采样应参考 CK 上升沿与 CK#下降沿的交叉点,时序参数如下:

tAS:地址信号和控制信号的建立时间。

tRTP:地址信号和控制信号的保持时间。

以上两个参数的测量与读操作无关,应在接收端存储器一侧测量,使用示波器的两个通道即可,通道一接差分探头,为时钟信号 CK/CK#,通道二接单端探头,为待测地址信号或控制信号。

DQS 与 CK/CK#之间的时序关系要求如下:

tDQSS:DQS 边沿与 CK/CK#交叉点之间的时序关系。

tDQSCK 参数应在存储器一侧测量,同样,使用示波器的两个通道即可,通道一接差分探头,为时钟信号 CK/CK#,通道二接单端探头,为 DQS 信号。

对读操作,还需在接收端存储器控制器一侧,测量 DQ 和 DQS 之间的时序关系。一般在存储器控制器内,将 DQS 偏移四分之一个时钟周期(即二分之一个数据周期)后,再对 DQ 进行采样,因此在控制器的引脚上,DQ 和 DQS 最佳的时序关系是边沿对齐,对于某些 DQS 偏移量可调节的存储器控制器,在引脚上测得的 DQ 和 DQS 信号,则没有边沿对齐的要求。

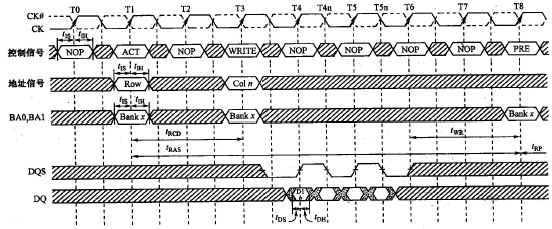

2)写操作

如下图所示为 DDR SDRAM 写操作的时序图,延时参数如 tRCD、tRAS、tWR、tRP 等,它们的定义与 SDRAM 相同。

对写操作,DQS 和 DQ 需满足以下时序参数:

tDS:DQ 相对 DQS 的建立时间;

tDH:DQ 相对 DQS 的保持时间。

需注意,对写操作,一般而言,存储器控制器在发出数据时,已将 DQS 偏移四分之一个时钟周期,即在发送端,DQS 的边沿正好位于 DQ 信号的中央,因此,只要在 PCB 设计中保证同组之内的 DQS 和 DQ 信号走线等长,即可满足接收端的时序要求。

3)上电初始化操作

DDR SDRAM 的上电初始化流程如下:

(1)VDD 和 VDDQ 同时上电。

(2)VREF 上电完成后,VTT 上电。

(3)等待 CK/CK#稳定运行 200μs。

(4)通过 PRECHARGE 操作对所有 BANK 预充电。

(5)配置扩展模式寄存器。

(6)配置模式寄存器。

(7)通过 PRECHARGE 操作对所有 BANK 预充电。

(8)发起数次 AUTO REFRESH 操作,至少要求两次。

(9)存储器开始正常工作。

4)模式寄存器的配置

对于 DDR SDRAM,片内寄存器分为模式寄存器和扩展模式寄存器,BANK[1:0]=00 时,选择模式寄存器,如下图所示。该寄存器的内容与 SDRAM 类似,不再赘述。

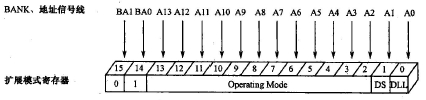

5)扩展模式寄存器的配置

BANK[1:0]=01 时,选择扩展模式寄存器,如下图所示。

第 13~2 位:操作模式位,必须为全 0 位。

第 1 位:DS,指驱动模式(Drive Strength),DS=0,选择正常驱动模式,DS=1,选择弱驱动模式。

第 0 位:DLL。DLL=0 时,使能 DDR SDRAM 内部延迟锁相环 DLL,DLL=1 时,关闭片内 DLL。

DDR SDRAM 的正常驱动模式即 SSTL-2 Class II 模式,线路电流 16.2mA,出于减小线路上信号衰减、过冲的考虑,某些场合下,要求较小的线路电流,因此,DDR SDRAM 提供了对弱驱动模式的支持,使能该模式时,输出电流仅为正常模式下线路电流的 54%,接近 SSTL-2 Class I 模式。应用中需注意以下三点:

要点一,并不是所有的 DDR SDRAM 器件都支持弱驱动模式。

要点二,在弱驱动模式下,信号边沿速率减缓,可能对时序产生一定的影响。

要点三,根据驱动模式的不同,对某些时序参数有不同的要求。在 DDR SDRAM 器件资料上,地址信号和控制信号的时序参数 tDS 和 tDH,有快边沿速率(fast slew rate)和慢边沿速率(slow slew rate)两种要求,其中快边沿速率的要求针对正常驱动模式,而慢边沿速率的要求针对弱驱动模式。例如,某款 DDR SDRAM,选择慢边沿速率时,tDS 的要求为 0.8ns,选择快边沿速率时,tDS 的要求为 0.75ns,前者略大于后者,即,在信号边沿速率较缓的情况下,应对时序裕量进行补偿。

某些存储器控制器,如 Vitesse 公司的 VSC9128,出于对信号质量的考虑,在器件资料上明确要求采用弱驱动模式,此时,一方面应配置 VSC9128 内部寄存器,使其弱驱动模式,同时,在 DDR SDRAM 的选型上,应注意选择支持弱驱动模式的器件,并对其扩展模式寄存器进行相应的配置。

3. DDR SDRAM 的时序测试

DDR SDRAM 的时序测试方法与 SDRAM 类似。

1)时序参考点

时钟信号的时序参考点是 CK 上升沿和 CK#下降沿的交点,对地址信号和控制信号,时序参考点选取为信号上升沿的 VREF 位置,而对数据信号如 DQ 和 DQS,时序参考点选取为信号变化沿(包括上升沿和下降沿)的 VREF 位置。

2)边沿变化速率

对时钟信号,CK 和 CK#的边沿变化速率应大于 1V/ns(当使用差分探头同时测量时钟信号的两端时,边沿变化速率应大于 2V/ns)。

对其他信号,从 VIL(AC) 到 VIH(AC),推荐边沿变化速率为 0.5~1V/ns,当边沿变化速率小于 0.5V/ns 时,时序参数应做降额处理:第一,对地址信号和控制信号,相对 0.5V/ns,每相差 0.1V/ns,要求 tDS 增加 50ps;tH 则不受边沿变化速率的影响;第二,对数据信号,相对 0.5V/ns,每相差 0.1V/ns,要求 tD 和 tH 都增加 50ps。

边沿变化速率也不能太快,当超过 4V/ns 时,DDR SDRAM 的功能不能得到保证。某些速率等级的器件,要求信号边沿变化速率必须大于 0.5V/ns,否则功能不能得到保证。

4. DDR SDRAM 的电源设计

DDR SDRAM 涉及四种电源。

VDD:DDR SDRAM 内核工作电源,为 2.5V。

VDDQ:DDR SDRAM 数据总线 I/O 接口电源,为 2.5V。

VREF:SSTL-2 参考电源。

VTT:SSTL-2 终结电源。

其中,VDD、VDDQ、VREF 是 DDR SDRAM 的电源引脚,VTT 不直接给 DDR SDRAM 供电,而是作为终结电阻的端接电源。

前文已讨论过这四种电源,以下将进一步加以总结。

(1)上电顺序:VDD 和 VDDQ 同时上电,随后 VREF 上电,VTT 最后上电。

(2)电平关系

VDD(min) = VDDQ(min) = 2.3V

VDD(max) = VDDQ(max) = 2.7V

VREF(min) = 0.49 × VDDQ

VREF(max) = 0.51 × VDDQ

VTT(min) = VREF(min) - 40mV

VTT(max) = VREF(max) + 40mV

VIH(AC)(min) = VREF + 0.15V

VIH(DC)(max) = VDD + 0.3V

VIH(AC)(min) = VREF + 0.31V

VIH(AC)(max) = VREF + 0.31V

VIL(DC)(min) = VREF - 0.15V

VIL(DC)(max) = VREF - 0.15V

VIH(AC)(min) = -0.3V

VIH(AC)(max) = VREF + 0.31V

3)功耗

在四种电源中,对 VDD、VDDQ 的功耗,需根据厂家提供的器件资料信息计算得出,一般每片 DDR SDRAM,功耗不会超过 1W。

对 VTT,除了 CK/CK#信号外,DDR SDRAM 的其他信号都将终结于 VTT。由于数据信号为双向信号,VTT 需支持吸收电流和驱动电流这两个方向的电流。

假设 Rs=Rr=25Ω,DDR SDRAM 源端内置串联电阻 RIN=10Ω,则对每个终结于 VTT 的信号,电流计算如下:

DDR SDRAM 输出高电平时,VTT 吸收电流为:

(VDDQ(max)-VTT(min)) / (Rs + Rr + RIN) = (2.7-1.09) / (25+25+10) = 26.8mA

DDR SDRAM 输出低电平时,VTT 驱动电流为:

(VTT(max)-VOL(min)) / (Rs + Rr + RIN) = (1.42-0) / (25+25+10) = 23.6mA

通过以上计算可知,这两个方向的电流大致相等。因此,接口总线中,当高电平和低电平信号数目相等时,VTT 电源上基本不耗电(吸收电流和驱动电流相抵消),但考虑极限情况,当所有信号的逻辑状态都相同时,耗电量最大。以某位宽为 16 位的 DDR SDRAM 为例,需终结于 VTT 的信号数是 42(16 个 DQ,2 个 DQS,2 个 DM,15 个地址信号,以及 7 个控制信号),则 VTT 电源需支持电流 1A。

在某些设计中,信号无需终结于 VTT,这些设计应满足如下要求:连接于同一个存储器控制器的 DDR SDRAM 少于两片,走线长度短于 2 英寸,经仿真,信号质量满足 SSTL-2 标准。对这种设计,可省去 VTT 电源。

对 VREF,其只是提供参考电平,耗电量不超过 5mA,但 VREF 必须和 VDDQ 保持稳定的关系,且对纹波的要求比较高,要求 VREF 电源上的纹波不超过 50mV。

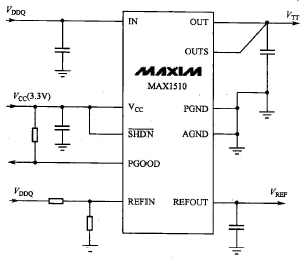

设计中,经常利用一个电源芯片同时输出 VTT 和 VREF 这两种电源,如下图所示MAX1510。

MAXIM1510 内置 MOSFET,可提供峰值电流高达 3A 的 VTT 电源,且同时提供纹波小、紧密跟踪 VDDQ 的 VREF 电源,即 MAX1510 等效于一个 DCDC 电源(输出 VTT)和一个 LDO 电源(输出 VREF)。

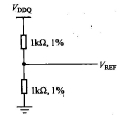

对 VREF,除使用 MAXIM1510 等商业电源芯片外,在轻负载的情况下(连接于同一个存储器控制器的 DDR SDRAM 少于两片),还可直接通过电阻分压得到,如下图所示。

由于 VREF 对干扰的要求特别高,在电源纹波测试时需注意,若将示波器探头放在器件 VREF 引脚上,将耦合进一定量的干扰,为避免测试时干扰的引入,应将示波器探头放在最靠近 VREF 引脚的电容上,而不是直接放在 VREF 引脚上。

【案例3】VREF 不稳定造成存储器读写操作出错

某设计中,对 DDR SDRAM 读写测试出错,测量 VREF,发现纹波较大。

【讨论】

检查 PCB 上 VREF 的滤波电路,DDR SDRAM 的每个 VREF 引脚附近均放置有一个 1μF 和一个 0.1μF 的去耦电容,符合设计的要求。

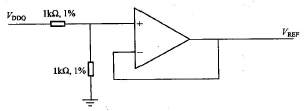

原理图上,VREF 产生电路如下图所示。

在该设计中,由于放大器输入端为高阻,VREF 电源只能产生单向电流,而 DDR SDRAM 要求 VREF 跟踪 VDDQ 的变化,VDDQ 支持灌电流和拉电流这两个方向的电流,因此 VREF 同样需支持两个方向的电流。

5. 存储器 DIMM 条

由于封装尺寸的限制,单片存储器的容量往往不能满足设计的要求,如单片 DDR SDRAM,最大容量是 1Gbit(1G 比特位,等于 128M 字节,以下简称为 1Gb,或 128MB),在高性能单板设计中,CPU 等芯片对存储器容量的要求往往较高,如 512MB,甚至达到 1GB 或更高。

为实现大容量存储,可采用两种方法。

方法一,将多片存储器芯片布放在 PCB 上,通过走线,将这些芯片连接在一起以构成大容量存储。

方法二,采用 DIMM 条,相对方法一,DIMM 条的使用有三个优势,其一是实现了大容量的存储,其二是节省了 PCB 面积,其三是简化了设计。

DIMM(双列直插式存储模块,Dual-In-line-Memory-Modules)简称双面内存条,是将多片存储器件集成于一块 PCB 上,通过该 PCB 的“金手指”引脚与单板上的 DIMM 条插槽相连的存储技术。DIMM 条本身也是一块 PCB 板,可以将 DIMM 条理解成大容量的存储模块,DIMM 条上 PCB 的金手指引脚分布于 PCB 的两面,因此,将这种存储模块称为双面内存条。

SDRAM、DDR SDRAM,以及下一节将要介绍的 DDR2 SDRAM 都有与自己相对应的 DIMM 条。区别在于 DIMM 条金手指引脚数目的不同:SDRAM DIMM 条引脚数为 168,每面的引脚数为 84;DDR SDRAM DIMM 条引脚数为 184,每面的引脚数为 92;DDR2 SDRAM DIMM 条引脚数为 240,每面引脚数为 120。

DIMM 分为两类:Unbuffered DIMM(无缓冲 DIMM)和 Registered DIMM(有寄存 DIMM)。

1)Unbuffered DIMM

对 Unbuffered DIMM(无缓冲 DIMM)而言,所有信号都是从存储器控制器直接连接到存储器芯片上。

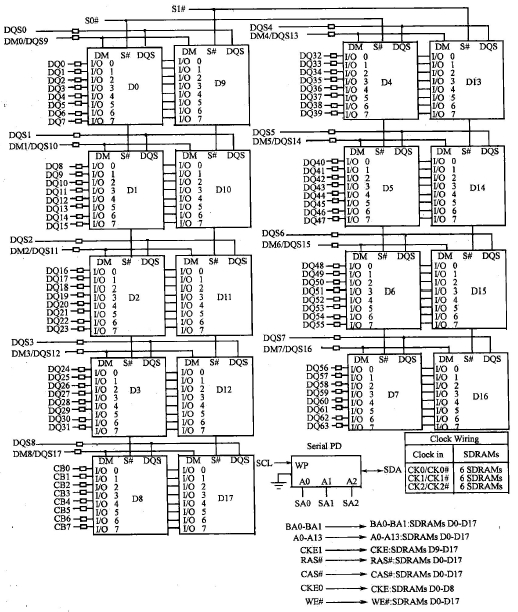

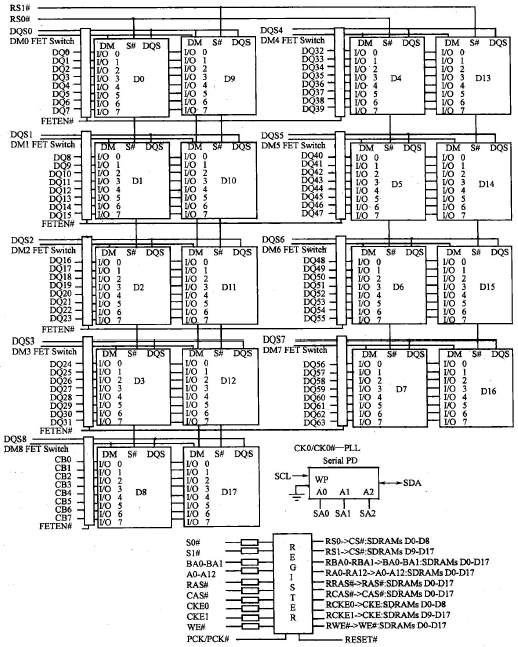

如下图所示为 DDR SDRAM DIMM 条的框图。DIMM 条分两个模块组,对模块组的选择是通过片选信号 SM#[1:0]实现。每组由 9 片位宽为 8 的 DDR SDRAM 芯片构成,因此,每个模块组的数据总线宽度为 64,另有 8 位数据用于 ECC(错误检查和纠正,Error Checking and Correcting)校验。在 DIMM 条上,每个数据信号线的负载数为 2。

图中,每个 DIMM 条有三组差分时钟输入端,即 CK/CK#[2:0]。每组为 6 片 DDR SDRAM 芯片提供时钟。DIMM 条输入的地址和控制信号直接连接到每个 DDR SDRAM 芯片上,除 CKE[1:0]的负载数为 9 外,其他信号的负载数都是 18。

DIMM 条上还有一个称为 SPD(串行存在检测,Serial Presence Detect)的 EEPROM 芯片。在 SPD 上存储有 DIMM 条上存储器件的基本信息,例如,BANK 数目、行地址数目、列地址数目、位宽,以及各时序参数如 CL、tRCD、tRP 等。上电后,通过读取 SPD,存储器控制器才能掌握 DIMM 条上存储器件的信息,以便正确配置存储接口。在设计中需注意,一般要求 SPD 的电源为 3.3V(某些 DIMM 条也支持 2.5V 的 SPD 电源),即便 DDR SDRAM 本身不需要 3.3V,也需专门为 DIMM 条上的 SPD 提供一个 3.3V 电源,该电源功耗很小,在 PCB 上用 20mil 宽度的走线即可。

2)Registered DIMM

Unbuffered DIMM(无缓冲 DIMM)条存在的主要问题是,地址和控制信号负载较多,负载越多,容性越大,信号的稳定性也越差,以至于存储器无法以最高速率工作。针对这个问题,JEDEC 国际标准组织定义了 Registered DIMM(有寄存 DIMM),某些对存储性能要求很高的芯片,如 Intel 公司的北桥芯片 E7501 等,即要求必须配套使用 Registered DIMM。

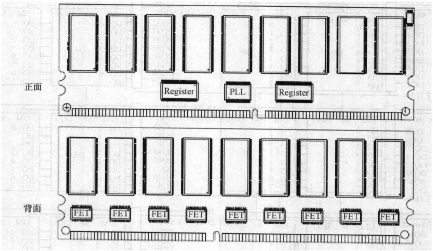

某款 Registered DIMM 外观图如下图所示。

该型号的 DDR SDRAM Registered DIMM 由两组模块组构成,每组由 9 片位宽为 8 的 DDR SDRAM 芯片构成,数据总线 64 位,另有 8 位数据线 CB[7:0]用于 ECC 校验。每个数据信号线的负载数为 2。

对地址信号和控制信号,除 CKE[1:0]的负载数为 9 外,其他信号的负载数都是 18,不同的是,在地址信号和控制信号被送到各个存储器芯片之前,都经过了驱动。

时钟信号将被 DIMM 条上的锁相环 PLL 作零延时驱动后,输往各个存储器芯片以及地址、控制信号的 Register 驱动器。

Registered DIMM 同样具有 SPD,置于正面的右上角。

Registered DIMM 原理图如下图所示。

3)两种 DIMM 的比较

Registered DIMM 与 Unbuffered DIMM 不同之处有以下几点。

区别一,利用 Register(寄存器)器件对地址和控制信号寄存,通过对存储器控制器的配置,使地址信号和控制信号先于数据信号一个时钟周期到达 DIMM,在 DIMM 的 Register 器件停留一个时钟周期,并在下一个时钟的上升沿输送到各个存储器芯片,通过 Register 器件的寄存,可以达到提高信号质量、增强驱动能力的目的。Register 器件位于 DIMM 条正面的下方。

区别二,利用锁相环 PLL 对 DIMM 条输入的时钟做零延时驱动,之后送往各个存储器芯片,同时还作为 Register 器件的时钟源。

区别三,Registered DIMM 增加了一个复位引脚 RESET#,以实现对 Register 器件和 PLL 锁相环的复位。Unbuffered DIMM 和 SDRAM、DDR SDRAM、DDR2 SDRAM 都不具备 RESET#引脚,复位功能通过 CKE 的低电平实现,而在使用 Registered DIMM 时需特别注意,操作前,软件程序必须先发出一个有效的 RESET#脉冲,Registered DIMM 才能正常工作。

区别四,在某些型号的 Registered DIMM 上,数据总线串接有 FET(场效应晶体管,Field Effect Transistor)开关,以增强数据信号的驱动能力。

由于增加了 Register 器件和锁相环 PLL,在对 Registered DIMM 的应用中,必须根据存储器控制器的器件资料,仔细进行时序分析。

简单要点:

① 相对于 SDRAM,DDR SDRAM 在以下方面有了技术更新:数据预取方式、信号电平、数据信号采样参考源、功耗等。

② 与 SDRAM 的 LVTTL 电平不同,DDR SDRAM 采用的电平方式是 SSTL-2。

③ 对于 DDR SDRAM,地址、控制信号均是基于 CK/CK#的单边沿采样,只有数据信号是基于 DQS 的双边沿采样。

④ DDR SDRAM 的时序测试方法。

⑤ Unbuffered DIMM 和 Registered DIMM 的区别。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?