4 PCB设计中的ESD防护

本小节介绍与ESD(Electronic Static Discharge,静电放电)防护设计相关的器件选型以及设计要点。

1. ESD防护器件

在单板的对外接口部分,常用的与防护设计相关的器件种类有TVS管、压敏电阻、气体放电管。

1)TVS管

TVS(Transient Voltage Suppressor)管指电压型瞬态抑制二极管,一般并联在被保护线路之中。在功能上,TVS管与稳压二极管相似,当输入电压突然增大,超过阈值电压时,TVS管反向导通,并提供快速的电流泄放通道,从而将电压钳位在安全区域,后级电路得到保护,而当输入电压恢复正常后,TVS管又能迅速地回到反向截止状态,不影响后级电路的正常工作。

与后面将要介绍的压敏电阻、气体放电管相比,TVS管是响应最快,但也是通流能力最差的器件。

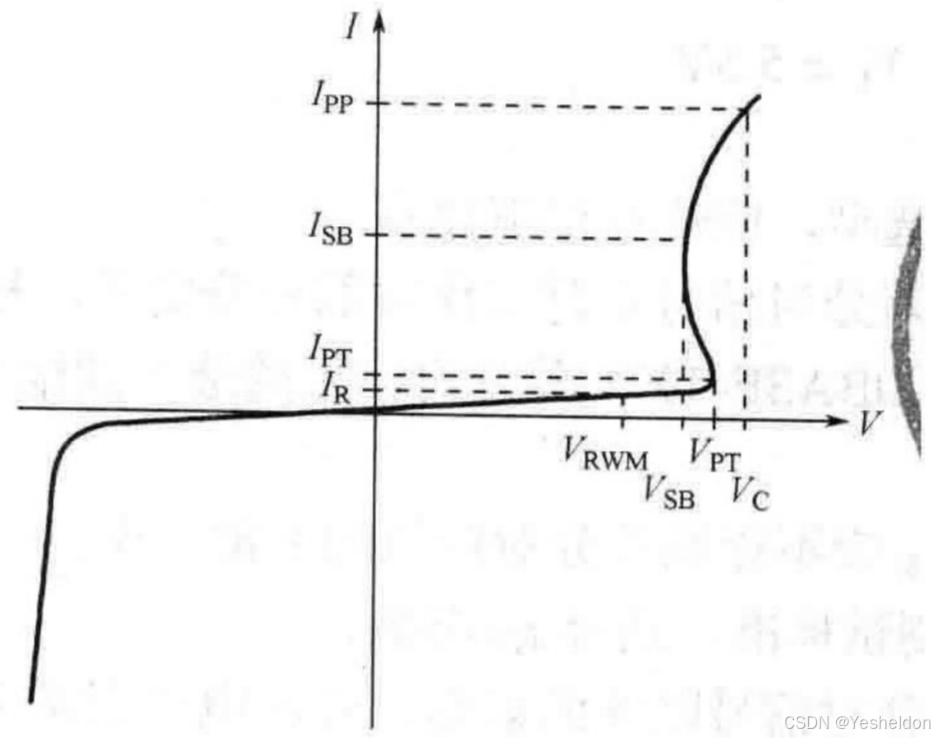

TVS管V-I曲线如下图所示。

以SEMITECH公司的SLVU2.8-4为例,介绍TVS管的关键参数。

VBWM:最高反向截止电压。当两端电压低于VBWM时,TVS管处于截止状态,管内仅有极小的反向漏电流IR流过。

VBR:最低导通电压。当两端电压高于VBR时,TVS管进入导通状态,此时管内流经的电流为IPP。

IPP:峰值电流。TVS管所能承受的最高电流,TVS导通的电流达到IPP时,两端电压达到最高钳位电压VC。

Cj:寄生电容。

VSAT:某些TVS管导通后,在一定的导通电流区间,随着电流的增大,两端电压反而减小,这种特性由VSAT和ISAT定义。VSAT和ISAT不属于关键参数,本小节不做过多的讨论。

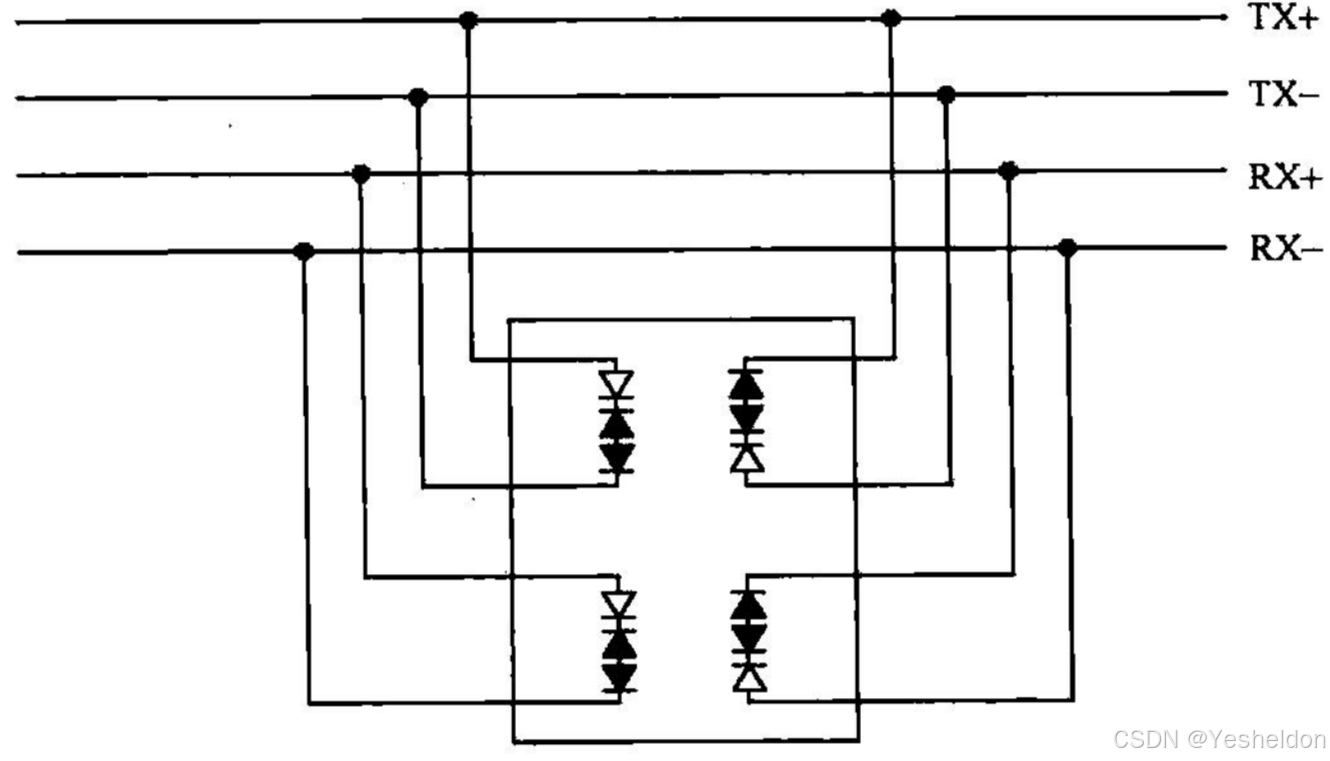

一片SLVU2.8-4由4个TVS管组成,以百兆以太网电口差分对信号为例,说明对TVS管的应用。

百兆电口的信号由一收一发两对差分对构成(TX+/-、RX+/-),与TVS管的连接原理图如下图所示。每对差分对使用两个TVS管,目的是实现正向、负向过压的保护。

对SLVU2.8-4而言,各项参数值如下:

VRWM = 2.8V IR = 1μA;

VBR = 3V VC = 5.5V

IPP = 24A Cj = 5pF

本例中,对TVS管的选型,应注意以下要点:

要点一,VRWM应高于差分对信号正常工作时的差分电平。根据IEEE(电气电子工程师协会)规范,百兆电口(100BASE-TX)差分对信号的最高摆幅为1.05V,2.8V的VRWM能满足该要求。

要点二,反向漏电流IR应不影响差分对信号的正常工作。

要点三,根据产品的测试标准,选择IPP参数。

要点四,权衡Cj对差分对信号眼图的影响。百兆电口正常工作时,TVS管的Cj参数将对信号质量构成一定的影响,例如,由于容性的存在,眼图边沿速率将降低,同时电口的回损等参数也会受到影响。因此,在TVS管选型以及测试中,应结合多方面的要求,确定适合的器件。

【案例10】TVS管布放位置不合理导致静电放电测试失败

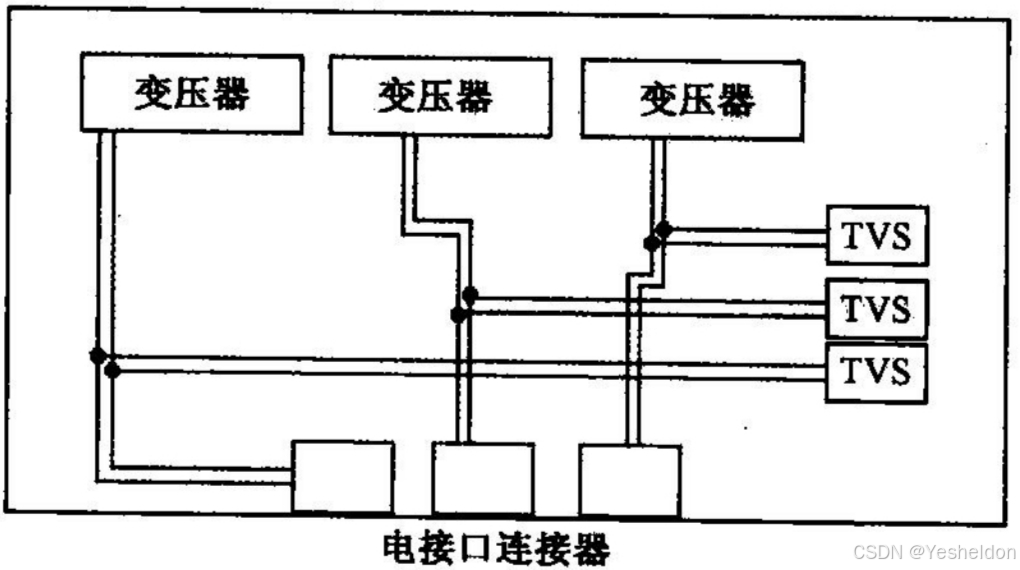

某电接口板TVS管放置位置如图8.43所示。

测试发现,该单板无法通过静电放电的测试。

【讨论】

在该设计中,设计者认为电接口信号速率较低(仅2MHz),线路上的stub影响不大,同时受限于PCB的布局,用户面板附近器件太密,这使得TVS管与被保护的差分对信号线距离较远,以致保护失效。

对接口电路的处理,需考虑的因素比较多,如前面提到的平面分割、EMI抑制,以及本小节提到的ESD保护,同时接口部分的信号速率往往较高,因此,在PCB设计时,需要做出一定的权衡。如在本案例中,接口差分对信号上还连接有电容、电感等调节回损、眼图的器件(未显示在图上),出于布局的限制,TVS管放置得较远,忽略了TVS管靠近主线路放置的原则,导致问题的出现。

2)压敏电阻

压敏电阻(VDR,Voltage Dependent Resistor),是指在一定电流和电压范围内,阻值随两端电压而变化的器件。压敏电阻一般并联在电路中,其保护机理与TVS管类似,当输入电压突然增大且超过阈值时,压敏电阻能将电压钳位到稳定的电压值。

压敏电阻响应时间为纳秒级,略慢于TVS管,但远快于气体放电管,通流能力介于TVS管和气体放电管之间。

在应用中要注意,压敏电阻的寄生电容相对较大,不建议用于高速接口。

3)气体放电管

气体放电管一般并联于接口信号的前端,其工作原理是,当放电管两端的电压超过阈值时,放电管击穿导通,两端电压降低,电荷快速地通过管体,从而实现了对后级电路的保护。两端电压恢复正常后,气体放电管恢复为断路,不对后级电路的工作造成影响。

气体放电管的响应速度较慢,为微秒级,但通流能力远高于TVS管和压敏电阻。另外,与TVS管和压敏电阻相比,气体放电管的寄生电容的寄生电容相对较小,因此,对高速信号的影响也是最小的。

4)ESD保护器件总结

TVS管、压敏电阻、气体放电管三者的特性总结如下。

响应速度:由高到低分别是TVS管、压敏电阻、气体放电管。

通流能力:由高到低分别是气体放电管、TVS管、压敏电阻。

寄生电容:由高到低分别是压敏电阻、TVS管、气体放电管。

反向漏电流:由高到低分别是压敏电阻、TVS管、气体放电管。

若结合三者同时实现对后级电路的保护,应遵循以下原则:

原则一,使响应速度最快的TVS管最靠近被保护的器件,而通流能力较强的气体放电管和压敏电阻则放置在接口的前端。即由接口的前级到后级分别放置:气体放电管、压敏电阻、TVS管。

原则二,高速设计中应考虑保护器件的寄生电容对高速信号的影响。一般不建议在高速信号上使用压敏电阻。是否使用TVS管,需仿真其寄生电容对接口信号眼图、回损等参数的影响。

原则三,保护器件应就近放置于接口信号的主线路,不能通过长引线连接到接口信号上。

2. 防护设计要点

1)高、低压电路之间的爬电距离

在分布式电源架构中,通常由-48V(或50V等)电源作为单板的总电源,经一级隔离电源电路得到中间电源IBV后,再通过第二级非隔离电源电路获得板内器件所需的各种电源。在这种电源架构中,-48V属于高压电源,其他电源可以为低压电源,在高、低压电源的布局和布线设计上,应注意有足够爬电距离的要求。

爬电距离指电平相差较大的导电体(如器件、PCB走线等)之间应保持的最小距离。电路设计上应保证爬电距离的原因在于,电路工作时,导电体周围的PCB材质将被电极化,当相邻导电体的压差较大时,通过电极化后的PCB材质,能形成一条导电的通路,使得相邻导电体之间存在短路的危险。

在PCB上,高压电路(仅指与-48V、50V等电源相关的电路,不包括220V交流电等)与其他低压电路之间的爬电距离要求为1.4mm。在对爬电距离规则的应用中,有以下几个常见的误区:

误区一,只有-48V电源才是高压电源。事实上,除-48V电源外,-48V电源的返回路径也为高压电路的地,本书以HV_GND代表。-48V缓启电路、-48V滤波电路、-48V的电压电流监控电路等,都应作为高压电路。

误区二,只在同一层上保证1.4mm的爬电距离。事实上,对多层板的层叠结构而言,两相邻层之间的距离一般都远远小于1.4mm,因此,对处在相邻层之间的高、低压电路,同样要求满足爬电距离。

误区三,用GND(单板上的普通信号地)对高压电路进行隔离。GND属于低压电路,其与高压电路之间同样要求满足1.4mm的爬电距离。因此,在高压电路下的内层,建议将对应的电源平面、地平面做挖空处理。

误区四,既然在机框上将GND和HV_GND连在一起,那么单板上可以将这两个地合成一个。事实上,机框上将普通信号和高压地连在一起,是基于EMC、防护等多方面的因素,若在单板上直接将这两种地连在一起,则无法对低压电路起到保护作用。

【案例11】GND和HV_GND混用导致电源控制电路失效

某产品的业务板为-48V电源电路添加了关闭功能,关闭信号由主控板输出,但测试发现,在业务板上,该关闭功能无法实现。

【讨论】

关闭信号由主控板上的FPGA输出,该信号的参考回路是GND,而-48V电源电路的参考回路是HV_GND,HV_GND和GND在该产品上没有短接,导致关闭信号和电源电路的参考电平不同,关闭功能无法实现。

2)单板与机壳地的搭接

静电放电测试一般在面板接口部分进行,因此,在面板接口处加强电荷的泄放路径有利于对内部电路的保护。RJ45是常见的用户接口,在面板上,通过焊接使RJ45接口与金属机壳可靠搭接,可有效地实现第一级电荷泄放。

在单板上,利用金属化过孔使单板地与金属机壳可靠搭接,同样有助于防护。

单板与机壳搭接的设计中,常见的错误有两个:其一是使绿油阻焊剂上金属化过孔,其二是在金属机壳上涂漆。这两种做法都将削弱单板与机壳之间的可靠搭接,无法发挥防护的效果。

3)对用户面板上按钮等器件的保护

电子产品的用户面板上,往往提供有供用户使用的按钮,以实现复位等功能。由于按钮与面板间不可避免地存在间隙,导致静电冲击极易通过该间隙泄放到电路上,因此,对按钮等器件的保护也是防护设计的一项重要课题。

有三项措施可用于该项保护:

措施一,使用气体放电管等ESD防护器件。

措施二,在按钮的信号线上,靠近面板处放置一个新高压电容,如额定电压为2000V的100pF电容。

措施三,在与按钮相连接的器件端,靠近器件放置一个330Ω的串联电阻。

4)变压器的应用

在电子产品中,变压器被广泛地用做隔离防护器件。除防护功能外,变压器还能实现电压变换、阻抗变换、信号隔离能力的提高、信号质量的改善等功能。

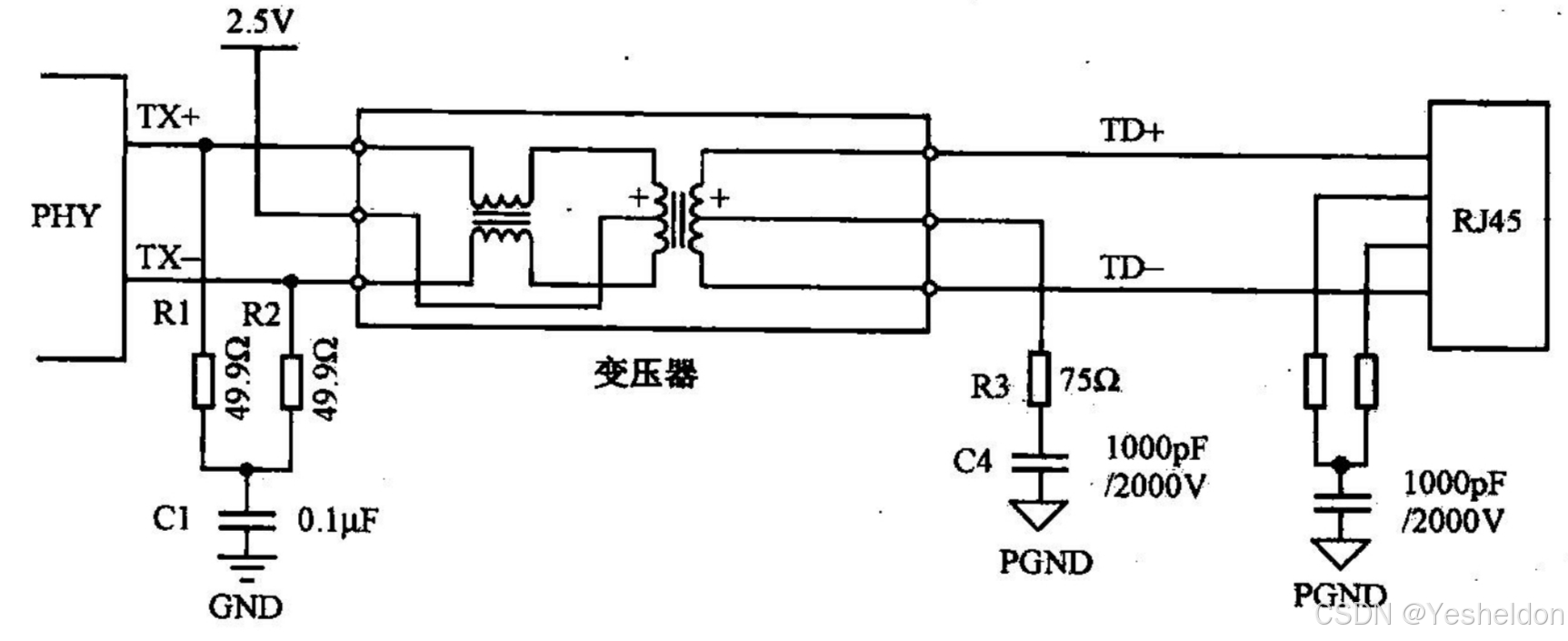

如图8.44所示,以以太网电接口的发送端为例,对变压器的应用要点进行介绍。

下图中,PHY芯片输出的差分对信号TX+/-与变压器的初级相连,变压器的次级与RJ45连接器相连。在初级一侧,R1和R2差分对信号提供100Ω的终端匹配,C1的作用是为差分对信号的共模分量提供回路,变压器初级的中央抽头连接到2.5V,作用是为差分对信号提供2.5V的直流偏置。

在次级一侧,TD+/-信号与RJ45连接器相连,变压器次级的中央抽头和RJ45连接器的空闲引脚需通过Bob Smith电路连接到保护地(用PGND代表)。

Bob Smith电路由75Ω电阻和高额定电压的电容组成,其作用是,一方面实现信号的阻抗匹配,另一方面为共模噪声提供到PGND的回路。该电路能有效地降低接口部分的EMI。

在以上电路中,有以下要点需要注意:

要点一,在选型中,需关注变压器初、次级之间的绝缘耐压度,如PULSE公司的H1200变压器的耐压度为1500V。在应用中,应根据隔离的要求对该参数进行选型。同时,还需关注变压器的插损和回损参数,这些参数对接口的眼图、回损等性能指标都有一定影响。

要点二,信号地GND和保护地PGND应在变压器处进行分割,变压器下方的各层均应做挖空处理。变压器初级侧电路的参考为GND,而次级侧电路的参考为PGND,以变压器为界限,初级电路和次级电路应严格分开,不能交会走线。要求PGND与金属机壳可靠搭接。

要点三,Bob Smith电路中的电阻,应选择通流能力的型号,电路中的电容,应选择高额定电压的型号。在静电放电测试中,该电阻和电容将作为电荷的重要泄放通路,因此,对其通流能力和额定电压都有一定的要求。在PCB设计中,Bob Smith电路的走线应加粗,且走线长度应尽量地短。推荐将电容的接地端直接与单板的金属安装孔相连,以便充分地发挥安装孔的放电通路作用。

要点四,Bob Smith电路属于高压电路,电路中的电阻、电容的焊盘及其走线等,应远离LED指示灯等低压电路信号线。此处需特别注意的是,电阻和电容的焊盘尖角,是放电的重要路径,因此,必须使低压电路远离Bob Smith电路的电阻、电容的焊盘。

要点五,不可将多个电接口的Bob Smith电路合并成一个,以避免在静电放电测试时,出现各接口间相互干扰的情况。

要点六,变压器初级的中央抽头与2.5V的连线应加粗。

要点七,从防护的角度看,变压器与RJ45连接器之间的距离越近越好(某些RJ45内置有变压器)。在主板上,PHY与RJ45连接器之间的距离较远(例如,PHY位于业务板,而RJ45连接器位于另一块接口板的情况),此时,需借助变压器实现对差分信号的驱动,在这种情况下,又希望变压器与PHY离得近一些,因此,对芯片、变压器、RJ45连接器三者的布局,应权衡考虑。

要点八,在GND与PGND之间,至少应保证100mil以上的距离,两者之间可通过高额定电压的电容等器件形成桥接,在GND和PGND之间保持一定的距离,其目的是避免在静电放电测试时,出现绝缘层击穿而短路的现象。

要点九,在变压器次级,可根据信号速率、防护等级,相应地增加TVS管、压敏电阻、气体放电管等防护器件。

5 PCB设计与结构、易用性

结构设计是硬件设计的一个专业领域,本小节并不介绍与结构设计相关的专业知识,而是从电子设计工程师的角度出发,探讨在PCB设计中,针对结构与易用性方面,应考虑的问题。由于结构设计的专业性较强,本小节不再罗列设计要点,而是以案例为出发点,结合具体案例进行探讨。

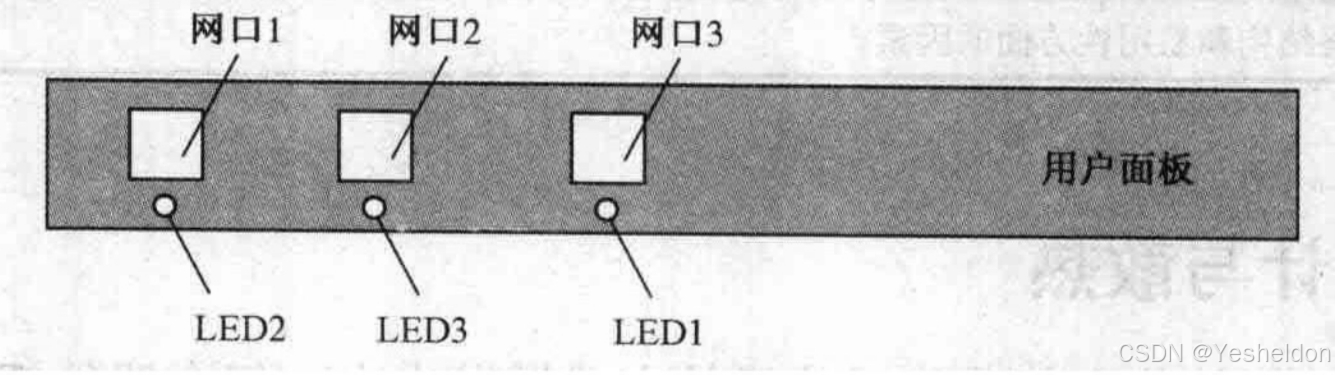

【案例12】网口指示灯排列顺序出错

某以太网接口板的网口采用指示灯与RJ45连接器分离的设计,设计完成后发现,指示灯的排列顺序与RJ45连接器的排列顺序不对应,如下图所示。

RJ45网口信号线与LED信号线由同一个PHY芯片驱动,但在PCB布局中,设计者没有考虑到二者之间的对应关系,仅仅因为小小的指示灯,就导致了PCB的改版。

【讨论】

对产品结构的忽略,是电子设计初学者常犯的毛病。在本案例中,面板上RJ45网口连接器与指示灯的位置由结构工程师定义,但其排列顺序以及与单板上信号线的对应,却是电子设计工程师的职责。出现类似问题另一个可能的原因是,原理图设计者没有很好地与PCB设计者进行沟通,如像第1章提到的,在原理图上对应位置加注释,应能避免该类问题的出现。

【拓展】

类似的问题还有很多,以下再增加几例。

(1)用户接口的排列顺序与用户说明书不符合。

(2)用户接口的序号与用户应用软件不符。面板上往往提供用户接口的序号,用户应用软件中,对接口也有对应的序号,这两个序号是否相同?有时会出现面板上用户接口的序号从0开始增长,而用户软件中,接口的序号却是从1开始增长,这种情况应注意避免。

(3)用户接口的排列方式与产品中同系列的其他单板不同。

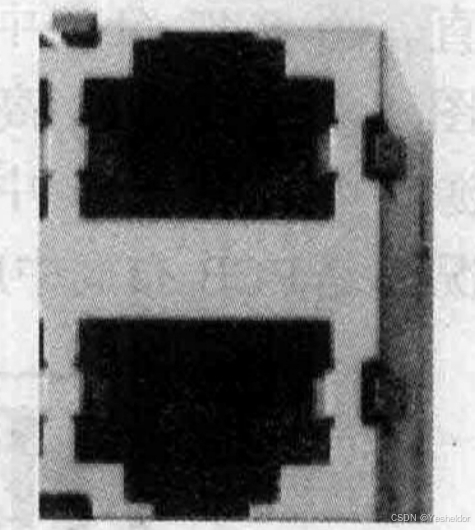

【案例13】网口连接器堆叠方式与易插拔特性

堆叠式的RJ45网口连接器如下图所示,该设计体现了易插拔的特性。在RJ45连接器上有一个缺口,用于容纳电缆水晶头的卡钩,对堆叠式连接器而言,两RJ45连接器背对背的设计方法,有利于电缆的插拔。

【讨论】

易用性是PCB设计的一个基本要求,以下再举几个例子:

(1)在调试阶段,某些设计上采用了跳线以选择不同的电路工作模式,在高密度板上,需注意,在这些位置,跳线帽是否容易插拔。

(2)在调试阶段,某些器件(如电阻、电容等)需要经常更换,则这些位置是否便于电烙铁焊头的可靠接触。

(3)某些经常使用的测试点,是否被器件的散热片覆盖,使得探头无法接触。

理解要点:

在PCB设计中,不能忽略结构和易用性方面的因素。

6 PCB设计与散热

器件工作时,功耗的绝大部分将以热量的方式散发出去。每个器件都有一个稳定工作的温度范围,在器件资料中以结温或壳温定义,一旦超过这个范围,器件的性能将受到影响。

在高速电路设计中,对散热的考虑应结合几个要点:器件自身的功耗、器件功耗对周围器件的影响、散热通道。以下分别进行讨论。

1. 器件自身的功耗

在概要设计阶段,设计者应对板上关键器件的最大功耗进行估计,根据该估计值,评估风扇风力、散热片是否足够。

某些高速器件片内带有温度传感器,温度超出阈值后,可输出告警信号,推荐将这种告警信号连接到控制器的中断处理引脚。

在测试时,应用用温度探头监测器件外壳的温度,确保器件工作时,表壳温度处于器件资料所定义的范围之内。

2. 器件功耗对周围器件的影响

晶振、存储器、YSV型的电容等器件,都属于温度敏感器件,在设计时,应尽量远离电源模块、LDO、高功耗器件等热源。

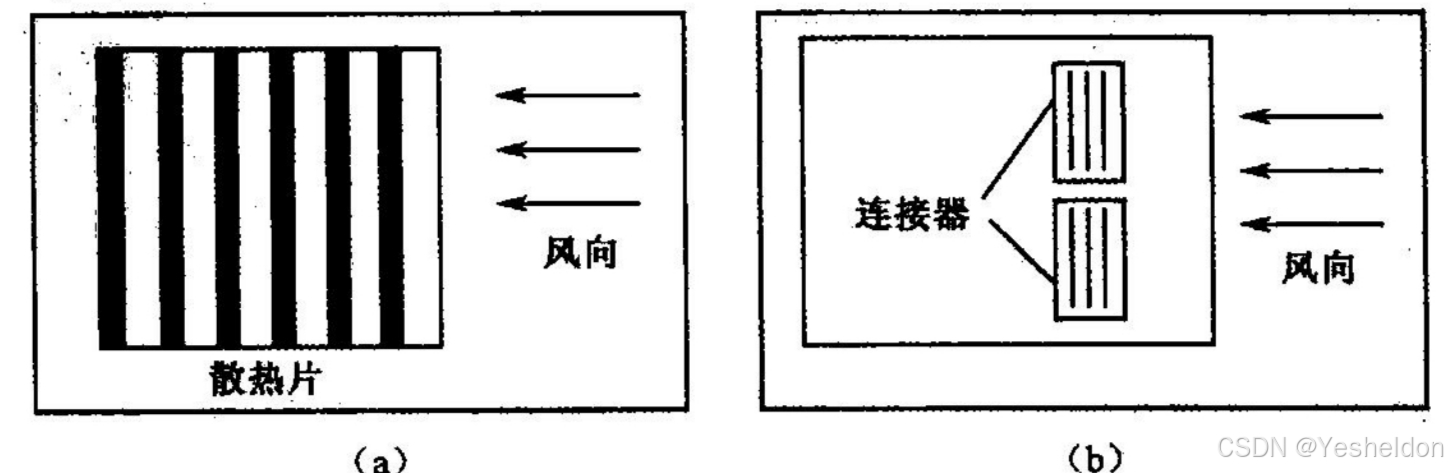

3. 散热通道

如下图所示,列举几个散热通道不好的例子。图(a)中,散热片的齿型突起与风向垂直。图(b)中,连接器的排列方向与风向垂直,这两种布局都将构成对风道的阻挡。图(c)中,高功耗的器件处于进风口,对下风向的器件而言,其散发的热量等同于热源。图(d)中,高个器件位于进风口,对下风道的整个器件起到阻挡作用。这四种情况都是PCB布局中应避免的。

理解要点:

在PCB设计中,需从器件自身的功耗、器件功耗对周围环境的影响、散热通道等几个方面对散热进行考虑。

7 PCB设计与可测试性

“可测试性”包括两个方面的内容,其一,生产的可测试性,其二,设计验证中的可测试性。

1. 生产的可测试性

生产可测试性的目的是检查单板加工过程中可能出现的短路、断路、虚焊、误焊、漏焊、错料等情况。单板越复杂,器件密度越高,可测试性的要求也越高。

单板设计中与可测试性相关的技术包括边界扫描、ICT等。

1)边界扫描

边界扫描基于芯片的JTAG接口,将具有JTAG接口的芯片连成一条链路,通过该链路,可验证链路上各芯片之间的连接是否正确。

JTAG是Joint Test Action Group(联合测试行为组织)的缩写,现在已成为国际组织IEEE定义的边界扫描测试的标准接口,其标准编号为IEEE1149。JTAG接口不仅可用于器件引脚之间的连通性验证,还被广泛地用于可编程器件(如CPLD、FPGA等)的程序加载。

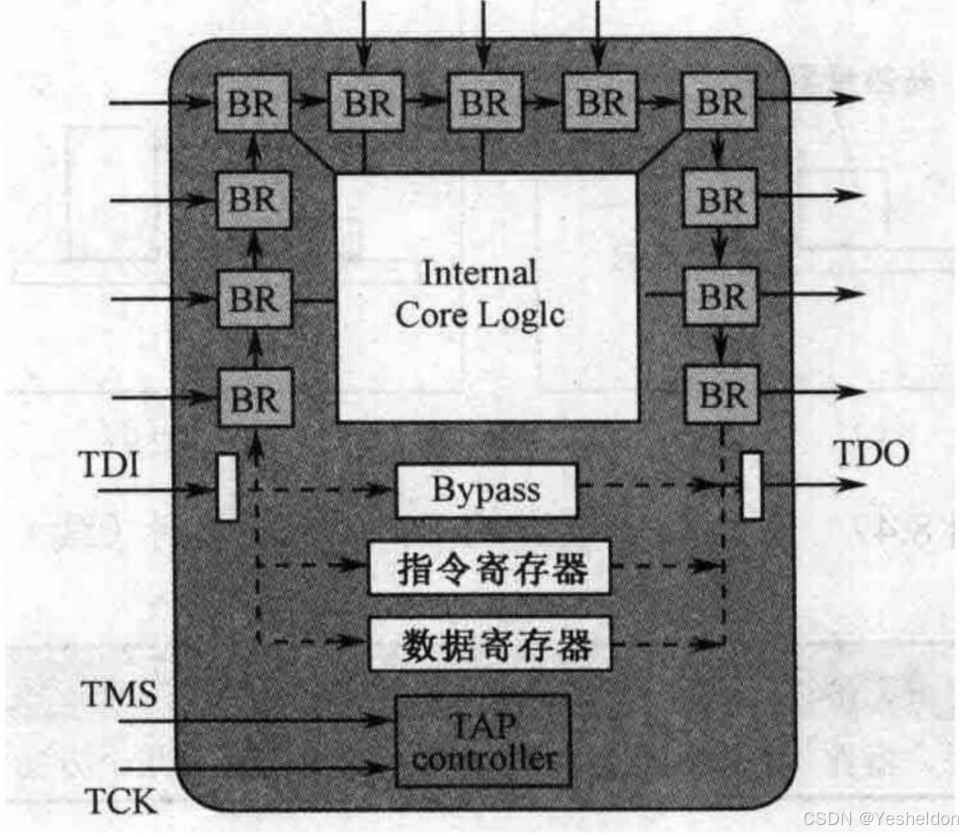

JTAG接口包括五个信号:TCK、TDI、TMS、TDO、TRST,其中,TCK为时钟输入信号,TDI为数据输入信号,TMS为模式选择信号,TDO为数据输出信号,TRST为复位输入信号。链路方式参见之前图。

对于支持JTAG接口的器件,其内部边界扫描单元如下图所示。

边界扫描单元为器件的每个I/O引脚各增加了一个边界寄存器(BR),并将这些边界寄存器连成链路,链路的输入端接TDI引脚,输出端接TDO引脚,从而构成边界扫描通道。测试数据由TDI输入,经器件内部边界寄存器链路后,从TDO输出,该链路的时序参考为TCK,模式选择由TMS提供。

由于链路上所有的器件通过JTAG接口构成了一条完整的通路,通过TDI输入数据控制下的边界寄存器,即可发送测试数据到相邻的器件,同时又可接收来自相邻器件的测试数据,通过核对收发数据是否匹配,即可验证相邻器件之间的连接是否正确。

器件正常工作时,边界扫描功能被复位,边界寄存器被旁路,因此,边界扫描功能的存在,对器件的正常工作并不构成任何影响。

JTAG接口的应用要点如下:

要点一,测试数据从TDI输入,由TDO输出。TDI接口输入的数据参考TCK的上升沿,TDO接口输出的数据参考TCK的下降沿。TDO接口最先输出的数据来自链路上最后一个器件。因此,在JTAG链路调试时,若发现在某器件处链路中断,一般可得出结论,即在链路中,该器件所处位置之后的链路是正确的。TMS信号的参考为TCK的上升沿。TRST为低电平有效的信号。

要点二,为保证器件的正常工作,JTAG接口信号应作下拉处理。

TCK下拉1kΩ电阻(当链路上共用TCK信号的器件较多时,需相应地减小下拉电阻的阻值,但建议下拉电阻阻值不低于220Ω),将TCK下拉处理的原因是,防止在TCK引脚上产生有效的上升沿,进而误触发对TDI和TMS的采样。

TMS上拉4.7kΩ电阻(同理,当链路上共用TMS信号的器件较多时,需相应地减小上拉电阻的阻值,但建议上拉电阻阻值不低于0.5kΩ),将TMS上拉处理的原因在于,在TMS连续若干周期保持为高电平的情况下,JTAG接口将进入旁路状态,以便保证对器件的正常工作不造成任何影响。

TDI上拉4.7kΩ电阻,且靠近输入端放置,将TDI上拉处理的目的是,在器件正常工作时,使JTAG接口能可靠地处于旁路状态。

由于发送端器件的TDO信号与接收端器件的TDI信号直接相连,无需再对TDO做上下拉处理。

TRST下拉1kΩ电阻(同理,链路上共用TRST信号的器件较多时,需相应地减小下拉电阻的阻值,但建议下拉电阻阻值不低于220Ω),对TRST作下拉处理的目的是,在器件正常工作时,使JTAG接口进入旁路状态。

在设计中需注意,某些器件的JTAG接口已经内置了下拉电阻,则无需再进行外部上下拉。

要点三,各个器件的JTAG接口电平标准可能不同,此时,需利用74LVC125等逻辑器件进行电平的转换。

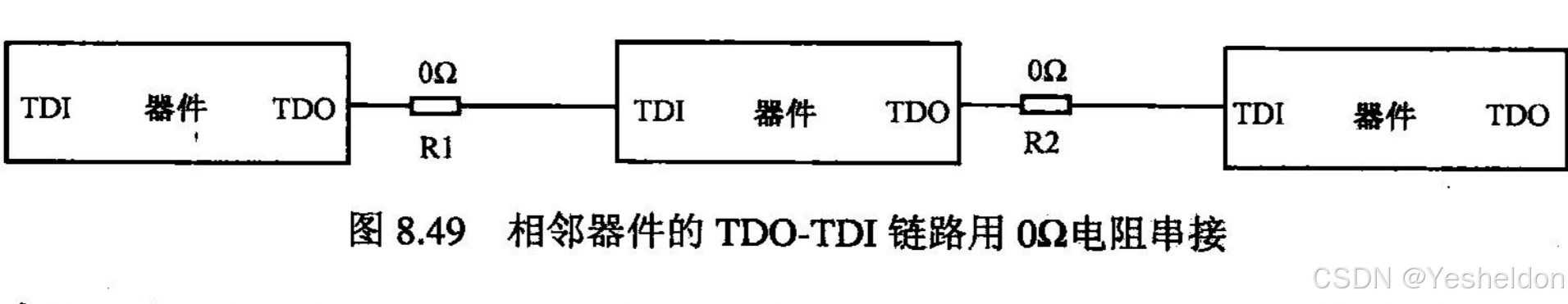

要点四,为方便链路调试,建议在相邻器件的TDO-TDI链路上串接100Ω电阻,如下图所示。对于边界扫描链路上彼此相邻的三个器件,若怀疑链路的某处可能存在故障,为定位问题,可将R1和R2断开,用飞线将第一个器件的TDO引脚和第三个器件的TDI引脚直接相连,若链路恢复,则故障可定位到中间的器件。

要点五,若CPU选用了Freescale公司的PowerPC,需注意CPU的调试接口与JTAG接口存在复用的关系,例如,MPC8XXX系列CPU的BDM(后台调试接口)和JTAG接口是复用的,在边界扫描测试时需注意将接口配置为JTAG模式。

2)ICT测试

虽然边界扫描具有高效、标准化的优势,但其也存在以下局限性。

局限性一,测试只能在支持JTAG接口的器件之间进行,对不支持该接口的器件则无能为力。

局限性二,测试必须在单板上电后才能进行,若单板本身无法上电,则测试无法进行。

局限性三,通过边界扫描测试,无法获得两器件之间电阻的阻值、电容的容值等信息。

边界扫描的以上局限性,使其无法成为高密度单板唯一的测试方法,需配合其他的测试方法,共同实现生产中的可测试性。

ICT则基本克服了边界扫描测试的局限性。ICT指在线测试(In Circuit Test),是生产中最常用的测试方法。

与边界扫描相比,ICT不仅能实现对短路、断路、虚焊等故障的检查,还能实现对电阻、电容等器件参数的测试。另外,与边界扫描相比,ICT也能实现对可编程器件的程序加载。

ICT测试通过针床夹具来实现与单板测试点的接触,一次只能并行测试有限的若干点,通过飞速地移动针头,以便在短时间内完成对全板的测试。ICT测试夹具的设计需针对单板而进行,不同单板之间不能套用同样的夹具。因此,ICT测试主要的缺陷有:一方面,夹具的成本相对较高;另一方面,ICT程序的编写和夹具的设计需要一定的开发时间,且程序和夹具往往不具备通用性。

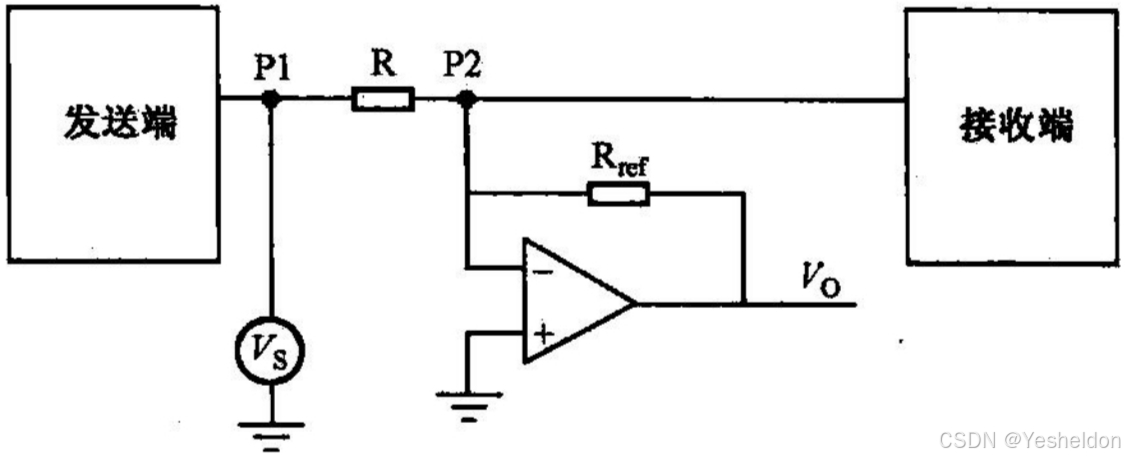

以下以电路中串阻阻值的测试为例,简单地介绍ICT的测试方法,如下图所示。

电阻R是串联在发送端和接收端之间的匹配电阻,可利用放大器实现对R阻值的测量。如上图中,使ICT夹具的两个针头P1、P2与R两端的ICT测试孔接触,同时,基于夹具提供的电压源VS和参考电阻Rref,可由式8.13获得电阻R的阻值:

R = Rref×Vs/Vo (8.13)

3)测试的覆盖率

边界扫描和ICT是针对生产的两种测试手段,在单板的详细设计阶段,就需要评估这两种测试方法对单板信号的覆盖率。

为了实现ICT测试,在PCB设计时,需为对应的过孔加ICT测试属性,在PCB设计完成后,可获得一份ICT测试覆盖率的表格,根据这份表格,检出无法添加ICT测试孔的信号,并判断这些信号能否被边界扫描测试覆盖。结合ICT覆盖率和边界扫描覆盖率,就可以获得整个单板的测试覆盖率。一般而言,对复杂的单板,测试覆盖率应在90%以上。

2. 设计的可测试性

电路的设计是否成功,需通过周密的测试以验证。在详细设计阶段,设计者就需要考虑如何对设计进行验证。

对单板板内电平性的测试,包括以下项目:信号完整性测试、信号时序测试、电源纹波和噪声的测试、温度测试。

对前三项测试,前面章节已经有过详细的介绍,这里补充对温度测试进行简单的介绍。温度测试是指,通过人为引入的故障,加强电路的耐受力,以验证电路在极端条件下是否能正常工作。以下是几种常见的温度测试方法:

方法一,电源电路的强度测试,可在输入端人为地增加干扰,验证输出端的抗扰性。

方法二,时钟驱动器的强度测试,时钟驱动器对输入时钟的占空比、精度、抖动等都有一定要求,可通过频率发生器产生输入时钟,同时外加抖动,以使该时钟达到时钟驱动器所要求的极限,以验证时钟驱动器在极限条件下是否能正常工作。

方法三,对数据总线的强度测试,可用金属片轻轻划正常工作中器件的数据引脚,以验证在短暂的数据出错后,器件能否恢复正常工作。

为了提高设计的可测试性,在PCB设计中,有以下要点需要注意:

要点一,对所有的关键信号,是否都有测试点,并且能有效地被探头接触?此处,有两点容易被忽略。其一,由于单板上其他器件(如散热片、较高的电源模块等)的存在,使得探头无法接触到测试点,而这种情况又难以从PCB设计图中发现。建议在PCB设计时,对关键的部分,应立体地思考问题;其二,在BGA封装的器件上,总线的某些控制信号可不连接,设计者可能忽略对该信号做BGA扇出处理,但在时序测试中却发现,这些信号对数据类型的判断起着重要的作用。因此,建议对BGA封装器件的所有信号,都做扇出处理。

要点二,在信号测试点附近,是否有地孔可被探头利用?高速信号测试中,探头地线的长短对测量结果有重要的影响,为测得真实的信号质量,应缩短地线的长度,避免地线成环,这就要求被测信号附近有地孔,以便探头的就近接地处理。

要点三,是否预留有板级测试的输入端。某些器件有专门的引脚,用于连接外界强度测试的输入,对于这些引脚,应连接有过孔以方便接触。

理解要点:

① 在PCB设计阶段,需考虑边界扫描和ICT测试对单板信号的覆盖率。

② 在详细设计阶段就应考虑如何对电路进行测试,并在PCB设计中预留测试点等。

2356

2356

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?