aarch64 linux4.9

arm64 mmu的 hardware page walke 和kernel中的重要概念

swapper_pg_dir 内核空间level 0页表物理地址

VA_BITS 39 mmu 看到的虚拟地址的长度

stage1 stage2 translation 当前系统没有el2 所有的translation 的规则遵守stage 1 的规则,如下来自arm中文社区

ttbr0 hardware page walker时level 0页表物理地址

ttbr1 up address page walk level 0 页表物理地址

t0sz 0x19 ttbr0 和 ttbr1 的mem region range是0~0x0000 00ff ffff ffff 和 0xffff f100 0000 0000 ~ 0xffff ffff ffff ffff

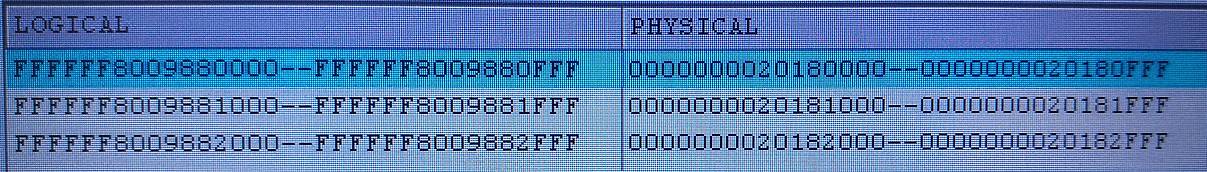

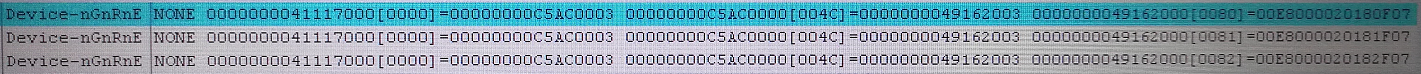

根据虚拟地址0xffff ff80 0988 0000 level 0 页表物理地址选ttbr1_el1 0x021e 0000 4111 7000,只有39bit有效物理地址 0x41117000 ,后面table walker 的截图是每一级页表根据offset查到的物理地址的整个过程

TCR_EL1 T0SZ 64-T0SZ=VA_BITS 39bit

armv8 每级页表offset计算方式(48bit arm文档为例)

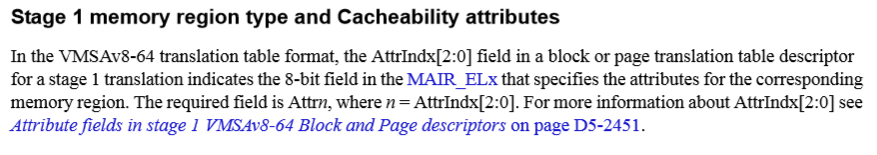

上面截图的第一列GnRnE属性的查询的方法:

1652

1652

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?