目录

一、 实验目的 3

二、实验环境 4

三、 设计和调试任务 4

四、实验原理 4

1.硬布线控制器 4

2.TEC-8数据通路 6

3.机器指令流程设计 8

4.指令设计 9

五、设计步骤与实验过程 10

六、模块设计 10

1.实体定义 10

2.初始化 11

3.写存储器模块 11

4.读存储器模块 11

5.写寄存器模块 12

6.读寄存器模块 12

7.取指令模块 12

7.1 ADD 12

7.2 SUB 12

7.3 AND 12

7.4 INC 13

7.5 LD 13

7.6 ST 13

7.7 JC&JZ 13

7.8 JMP 13

7.9 OUT 13

7.10 OR 14

7.11 NOT 14

7.12 XOR 14

7.13 STP 14

8.验收测试程序 14

八、流水实现 14

九、中断实现 16

十、实验心得 19

四、实验原理

1.硬布线控制器

控制器负责从主存中取指令并确定指令类型,控制器是计算机系统的指挥中心,控制器的主要功能有:

- 从主存中取出一条指令,并指出下一条指令在主存中的位置;

- 对指令进行译码或测试,产生相应的操作控制信号,以便启动规定的动作;

- 指挥并控制CPU、主存、输入和输出设备之间的数据流动方向;

控制器控制整个计算机系统的运行,分为CPU内部控制(依靠数据通路)和系统外部控制(依靠一组系统总线-数据总线 地址总线 控制总线):

• 系统内部的控制:根据控制信号构建数据通路,完成微操作规定的功能;

• 系统外部的控制:依靠一组系统总线进行控制;

尽管硬件可以直接执行机器指令,但是当我们研究其本质时发现它还能被拆分为多个小的微操作,这些微操作对应相应的控制信号,根据产生微操作控制信号的方式不同(也就是根据微操作信号发生器的结构不同),控制器分为硬布线和微程序;

硬布线控制器:

• 主要由PC IR 指令译码器 MAR MDR 时序系统 微操作发生器组成;

• 微操作控制信号由组合逻辑电路根据当前指令码、状态和时序即时产生;

• 执行速度快,不易扩充,常用于RISC;

微操作发生器:

• 输入:IR中的操作码、时钟脉冲、指令标志、外来信号;

• 输出:微操作控制信号(CPU内部控制信号/到控制总线的控制信号);

• 微操作控制信号以微程序的形式存放在控制存储器中;

• 执行速度慢,易扩充,常用于CISC;

硬布线控制器是一种将控制部件看作产生专门固定的时序控制信号的逻辑电路,当执行不同的机器指令的时候,通过激活一系列不相同的控制信号来实现对指令的解释。每个微操作控制信号C是一系列输入向量的逻辑函数,使用组合逻辑实现其表达式如下:

C=f(Im,Mi,Tk,Bj)

其中Im是机器指令操作码译码器的输出信号,Mi是节拍电位信号,Tk是节拍脉冲信号,Bj表示来自执行部件的反馈信息,即状态条件信号。

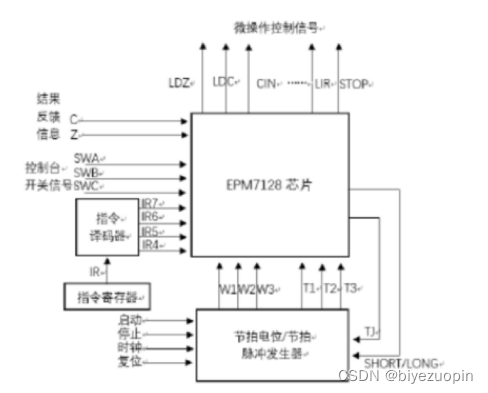

硬布线控制器的逻辑结构如下,在TEC-8系统中,节拍脉冲信号Tk(即T1T3)直接送入数据通路,Im由4位指令操作码以及SWA、SWB、SWC组成,Mi是时序发生器产生的节拍信号W1W3,Bj包括ALU产生的进位信号C、结果为0信号Z等。

地址 程序指令 机器码 16进制 第一次执行该指令 第二次执行该指令 第三次执行该指令

00H LD R0,[R2] 0101 0010 52 R0=67H

01H INC R2 0100 1000 48 R2=61H

02H LD R1,[R2] 0101 0110 56 R1=80H

03H ADD R0,R1 0001 0001 11 R0=E7H R0=E7H,C=1 R0=86H

04H JC 06H 0111 0001 71 不跳转 跳转到06H 不跳转

05H AND R1,R0 0011 0100 34 R1=80H R1=82H

06H SUB R0,R2 0010 0010 22 R0=86H R0=04H R0=83H

07H INC R1 0100 0100 44 R1=81H R1=82H R1=83H

08H STA R0,[R1] 0110 0100 64 [81H]=86H [82H]=04H [83H]=83H

09H INC R3 0100 1100 4C R3=FEH R3=FFH R=00H

0AH JZ 0DH 1000 0010 82 不跳转 不跳转 跳转到0DH

0BH LD R2,[R3] 0101 1011 5B R2=03H R2=03H

0CH JMP [R2] 1001 1000 98 跳回到03H 跳回到03H

0DH INC R3 0100 1100 4C R3=01H

0EH INC R3 0100 1100 4C R3=02H

0FH SUB R0,R2 0010 0010 22 R0=80H

10H LD R2,[R0] 0101 1000 58 R2=60H

11H ADD R3,R2 0001 1110 1E R3=62H

12H LD R3,[R3] 0101 1111 5F R3=FDH

13H OUT R0 1010 0000 A0

14H STP 1110 0000 E0

检测寄存器 R0= 80H R1= 83H R2= 60H R3= 0FDH

检测存储器 [81H]= 86H [82H]= 04H [83H]= 83H

文章详细介绍了实验中基于TEC-8系统的硬布线控制器设计,包括实验目的、环境、设计步骤和流程。控制器通过取指令、译码、产生微操作控制信号来协调CPU操作,涉及RISC架构的特性。文中还给出了指令设计和执行的实例,展示了一个简单的程序执行过程。

文章详细介绍了实验中基于TEC-8系统的硬布线控制器设计,包括实验目的、环境、设计步骤和流程。控制器通过取指令、译码、产生微操作控制信号来协调CPU操作,涉及RISC架构的特性。文中还给出了指令设计和执行的实例,展示了一个简单的程序执行过程。

3379

3379

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?