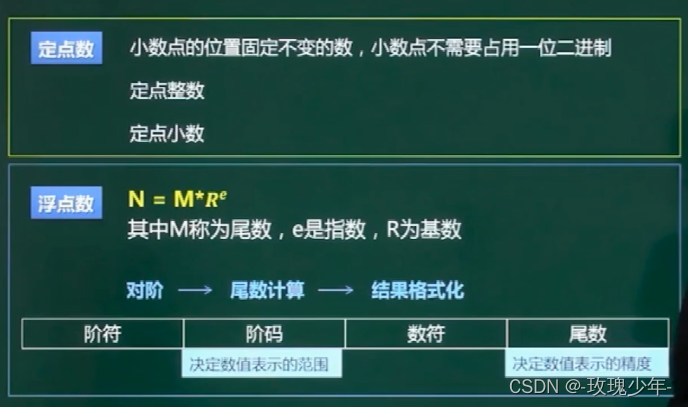

1、定点数与浮点数

定点整数的小数点在最低有效数位之后,也就是00000000.;

因为定点整数只表示整数,不涉及小数;

定点小数的小数点在符号位之后,也就是最高有效数位之前,也就是0.0000000;

浮点数,计算机中需要保存M和e,R都是2;

假如用16位表示浮点数,就需要分m位放阶码,分n位放位数;m+n=16;

阶码看成指数e,它决定数值的表述范围;

尾数决定数值的表示精度(保留小数点后几位);0.5×10^2 、0.005×10^4;

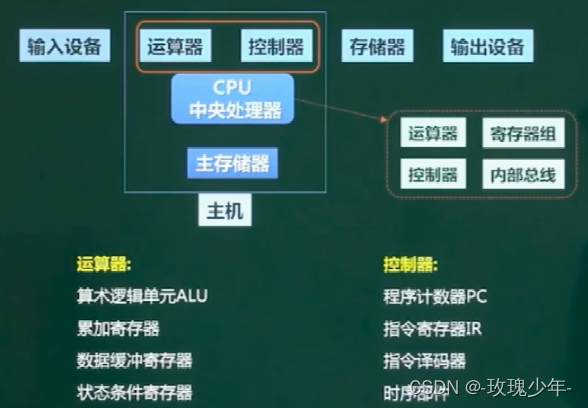

2、计算机的组成

冯诺依曼体系5大部件:输入设备、运算器、控制器、存储器、输出设备;

CPU组成:运算器、控制器、寄存器组、内部总线;

内部总线:连接芯片内的各个部件;运算器控制器只有连接才能进行通信;

主存储器:即内存;

主机:CPU+主存储器;不是生活中看到的主机;

运算器和控制器的各个部件需要重点记忆!!!!

具体讲解看这篇

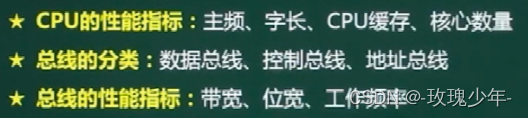

CPU性能指标,考点不固定,适当扩展;

主频:CPU的运行频率;

字长:CPU一次能处理二进制的位数;(重点理解)

CPU缓存:cache;

核心数量:CPU中独立计算引擎的数量;

总线的分类,重点掌握!!!

按功能分类:数据总线(传送数据)、控制总线(传递控制信号)、地址总线(决定系统寻址范围,即系统能够使用多少的内存);

32位操作系统,计算机内存一般不超过4GB,因为地址总线是32位,2^32= 4G;

现在64位就可以到8G、16G;

总线的性能指标:

带宽:单位时间内传送数据的量;单位MB/s;

位宽(常考):总线能够同时传送多少位二进制;一般位宽=字长;

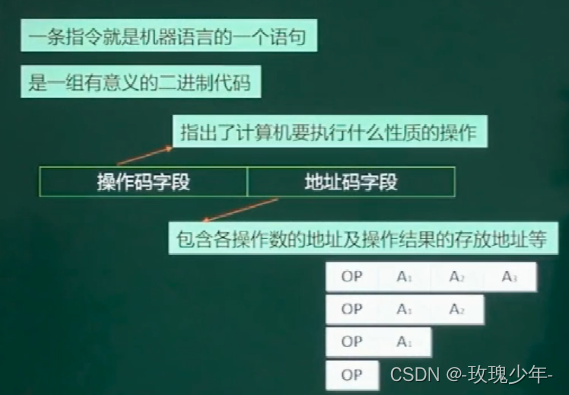

3、指令

指令由操作码字段和地址码字段组成;

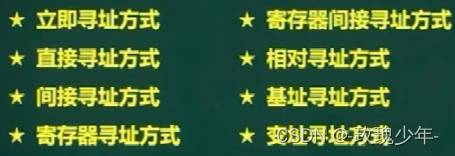

4.寻址方式:指令找到操作数的方式

立即寻址方式:操作数直接放在地址码部分;

将指令读到CPU里的时候,操作数也就一起被读到了CPU中,不需要在主存中找操作数了;

直接寻址方式:操作数放在主存中,地址码中存放的是操作数在主存中的地址;

间接寻址方式:操作数放在主存中,在主存中的地址是0002,地址码中存放的地址是0001,0001地址中存放的是操作数的地址,即0002;

寄存器寻址方式:地址码存放的是操作数所在的寄存器的地址;

寄存器间接寻址方式:操作数放在寄存器A中,寄存器A在主存中的地址是0002,地址码中存放的地址是0001,0001地址中存放的是寄存器B的地址,寄存器B中又存放了寄存器A的地址,即0002;

以下三个很少考:

相对寻址方式:当前指令+1,即下一条指令的位置;当前指令-1,即上一条指令的位置;

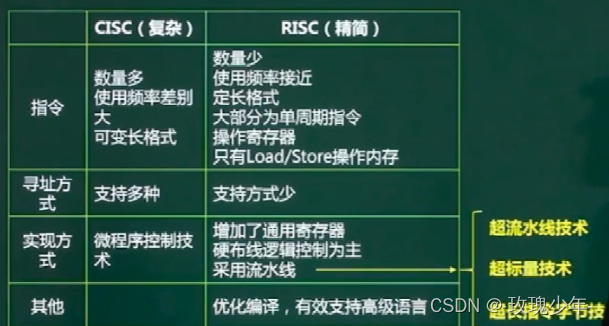

CISC(复杂指令集)和RISC(简单指令集)

一般考特点和实现方式;

RISC的操作对象是寄存器;

硬布线逻辑;即集成电路;

微程序控制,即软件控制;

超流水线技术:增加流水线的级别,使得在单周期内完成更多的运算;

超标量技术:多条流水线部件;空间换时间;

超长指令字节技术:多条指令组合在一起,使在周期内完成的指令更多;

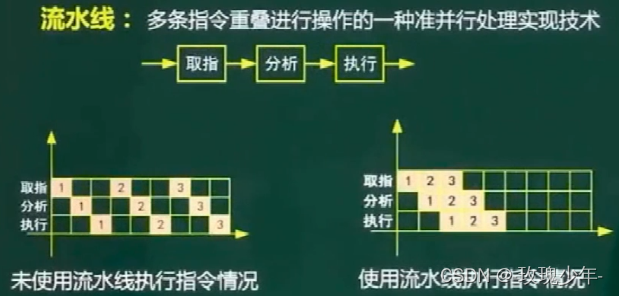

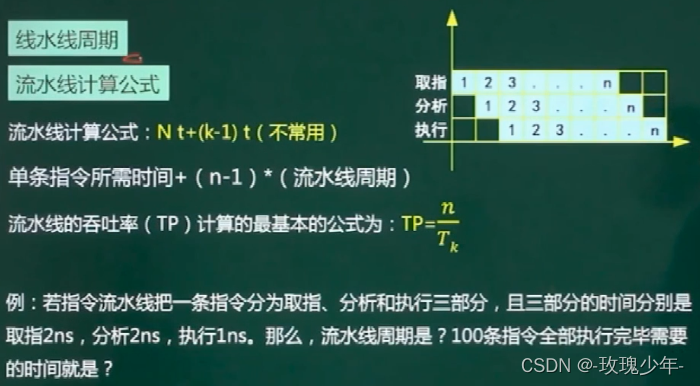

5.流水线(考察频率不高)

关键字:准并行;

选择执行时间最长的阶段为流水线周期;

吞吐率:单位时间内完成指令的数量,指令数/执行所有指令所需的时间;

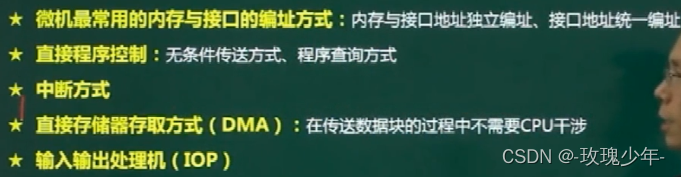

6.输入输出

主要看中断和DMA;

中断:外存传数据时,发出中断信号,CPU收到信号后,停止当前执行的工作,保存当前工作,转而响应外存的请求;

中断响应时间:保存当前过程,去响应请求的时间;

中断向量/中断矢量:CPU通过中断向量获取上次停止执行工作的位置;

DMA:IO传数据到主存很慢,CPU全程负责会十分影响性能,而DMA在传送数据的时候不需要CPU干涉,CPU的性能就得到充分的应用;

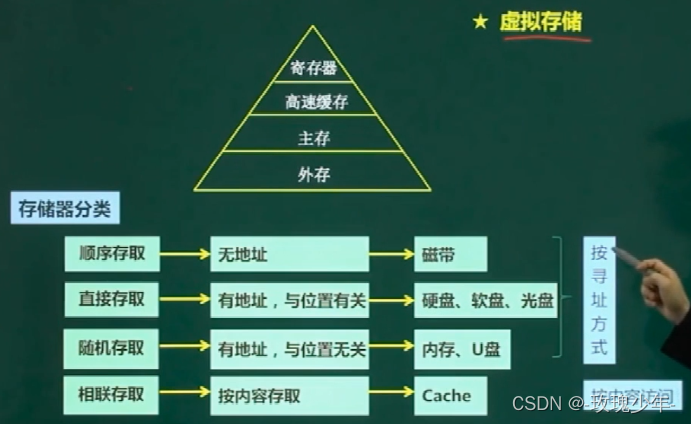

7.多级存储器结构

基于计算机的成本、容量、速度来确定的结构;

存取越快越昂贵;机械硬盘便宜、固态硬盘贵、内存更贵;

虚拟存储:在主存与外存之间扩展主存的技术;

几十G的游戏为啥能在几G的内存中运行?

允许先运行一部分,另一部分用到了再加入到内存;在外存上开辟一部分存储空间,加载程序的另一部分,这部分就可以存储到外存,最后需要这部分数据的时候,再读取到内存中;

顺序存取:数据的存储是没有地址的;如磁带,想要播放上一首歌,得快退到上一首歌的位置才行;主要原因是数据存储在存储器上的位置是没有地址的;无法准确定位;磁带往往会用于数据备份;

直接存取:有地址,与位置有关;磁头需要转到固定的磁道才能读取当前位置的数据;方位不同位置的数据所需的时间不一样;

随机存取:有地址,与位置无关;访问任意位置的数据所需的时间都一样;

相联存取:按内容存取;按内容的特点放到存储器中,按内容的特点进行访问;

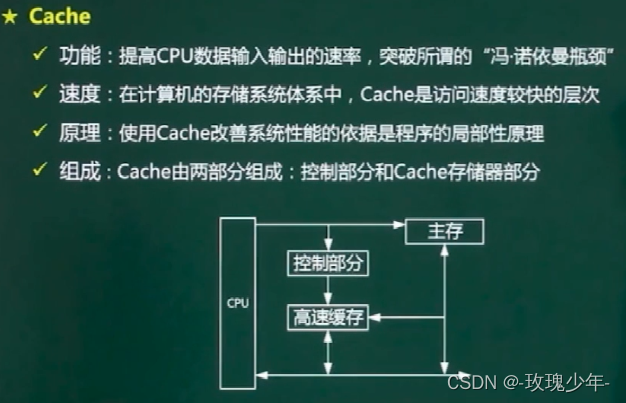

7.Cache(高速缓冲存储器)

Cache由两部分组成:控制部分和Cache存储器部分;控制部分由硬件进行控制;

Cache在主存和CPU之间;

局部性原理:内存中某个存储单元的数据被访问了,这个位置附近的其他存储单元被访问的概率就比较高;

CPU要数据,先去Cache中获取,有则直接拿,无则去主存中拿,同时此数据也在Cache中存一份;

8.地址映像

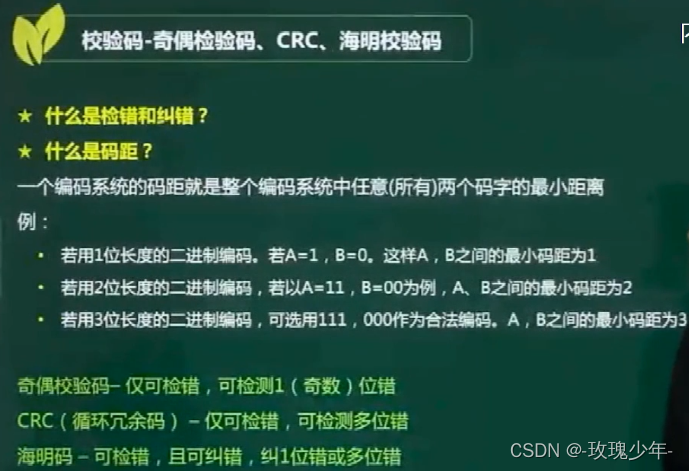

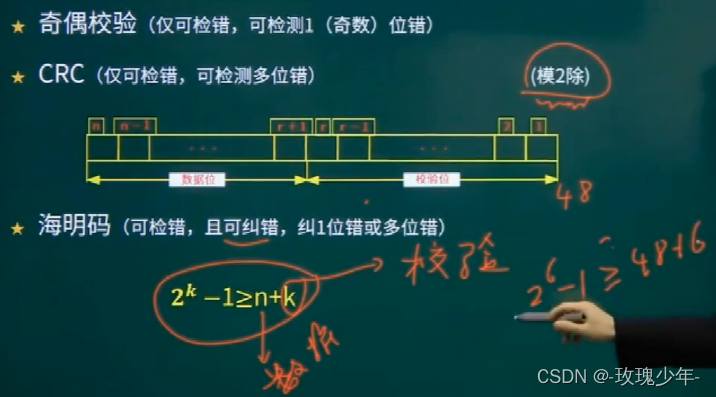

9.校验码—奇偶校验码、CRC、海明码

要记住三个校验码的特点,奇偶校验要记住其编码机制;

奇偶校验:在数据位的基础上再增加一个校验位,使得1的个数为奇数个,即奇校验;反之为偶校验;

奇校验:

1的编码:00001;2的编码:00010;3的编码:10011;(1的数字是偶数个,校验位得补1,否则不需补);

例如:传的数据是00010,但是在收到的是00011,1的个数不是奇数个,就代表传输的过程中发生了错误;

n表示的是数据的二进制位数;k表示的是校验位;

例如数据位是64位,则校验位是6位;

864

864

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?