78K0芯片的I/O引脚共45个,由MOS管组成。由于MOS管的逻辑电压具有自身的特点,当与TTL或其它类型的电路连接时,需要进行电平转换。

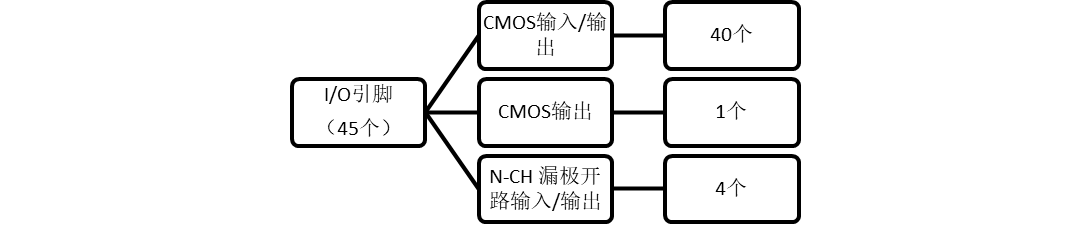

I/O引脚的分类如下图。

一.I/O输出电路

1.1 CMOS推挽输出

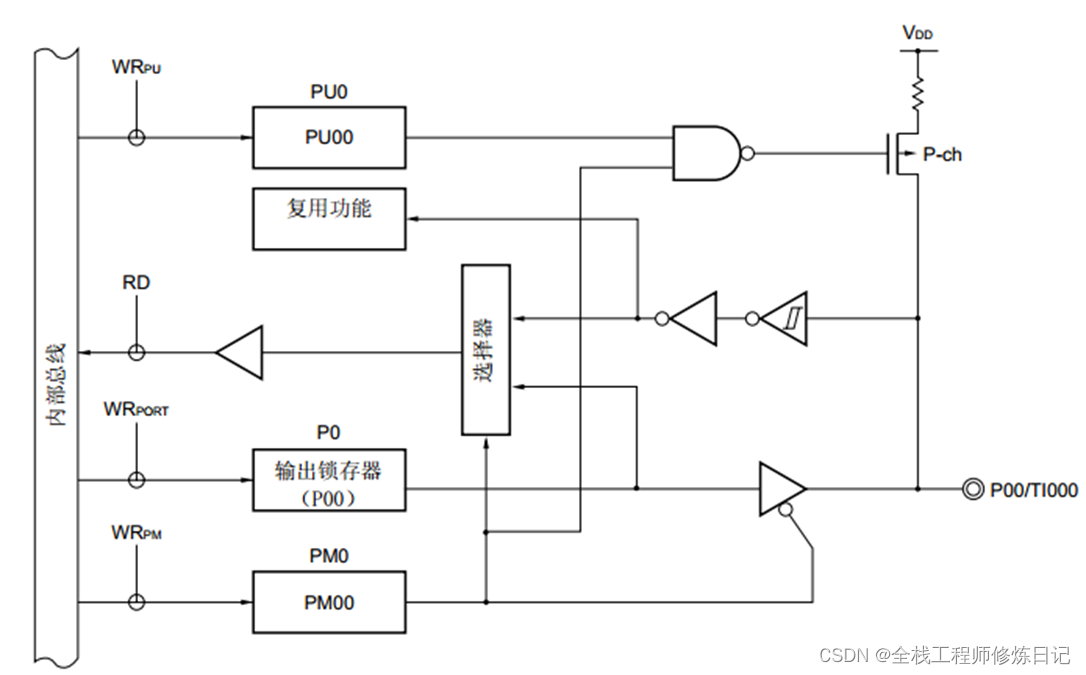

P0的引脚电路如下图所示。输出端由两个P沟道和 N沟道绝缘栅型场效应管组成,通过上下两个场效应管的交替截止与导通,输出高电平和低电平。

①输出高电平时:P-ch导通,N-ch截止。因为P-ch导通时的电阻很小,因此带负载能力较强。

②输出低电平时:P-ch截止,N-ch导通。因为N-ch导通时的电阻也很小,因此其允许外部电路输入较大的“灌电流”,但不能大于场效应管的漏极电流的极限。

此外,因场效应管导通电阻很小,故RC常数很小,其高低电平转变速度很快。

芯片手册中有这样一句说明:设置为输出模式的引脚和用作复用功能的输出引脚都不连接内部上拉电阻。

根据P0端口的电路框图(下图),可知,输出模式下,与上拉电阻串联的P-ch场效应管的栅极为高电平,因此,场效应管截止,即上拉功能失效。

1.2 N-ch漏极开路输出

IIC总线使用开漏输出引脚。

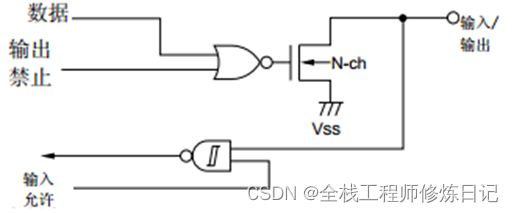

开漏输出主要有如下特点:

①可以将多个开漏引脚连接在一条线上,形成“线与逻辑”。即挂接在线上的任意一个IC的逻辑电平变低,开漏线上的逻辑即为0。电平置高时,变成高阻态,内外电路隔离,因此,释放IIC中的SDA或SCL时,必须将电平此引脚电平置高。

②可以利用改变上拉电源的电压,改变传输电平。

③开漏引脚必须在外部接上拉电阻,才有高电平输出,否则只能输出低电平。

为什么IIC总线不用CMOS引脚?

如下图所示。 假设左边的A输出高电平,右边的 B输出低电平,由于场效应管的导通电阻很小。因此,VDD相当于直接与地连接,造成很大的短路电流,会烧坏场效应管。

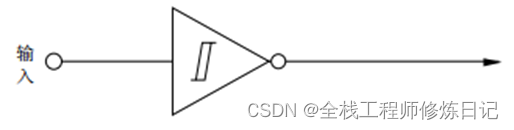

二.施密特输入电路

部分引脚采用了施密特输入,如P0引脚和IIC引脚。施密特输入电路由滞回比较器组成。此种比较器的特点是,输入信号ui逐渐增大时的阈值电压与逐渐减小时的阈值电压不相等,其传输特性具有“滞回”曲线的形状。而在单限比较器中,输入电压在阈值电压附近的任何微小变化,都会引起输出电压的跃变。因此,虽然单限比较器很灵敏,但是抗干扰能力差;而滞回比较器具有惯性,有一定的抗干扰能力。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?