本文来自https://www.systemverilog.io/网站上的关于LPDDR5的一篇文章,详细探讨了LPDDR5内存的物理结构,从基础开始逐步深入,收获颇多,分享给大家(翻译水平有限,大家包涵!)。这些内容协议上面也有,但往往只是跳过这些,但通过这篇文章我们可以清晰理解与LPDDR5内存物理结构相关的关键术语,包括:

1)LPDDR5接口:命令总线(CA)、数据总线(DQ/DQS)、片选(CS)、时钟(CK)

2)Bank与Bank Group架构

3)Rank与page大小

4)LPDDR5内存通道

5)x16/x32/x64位宽的解释

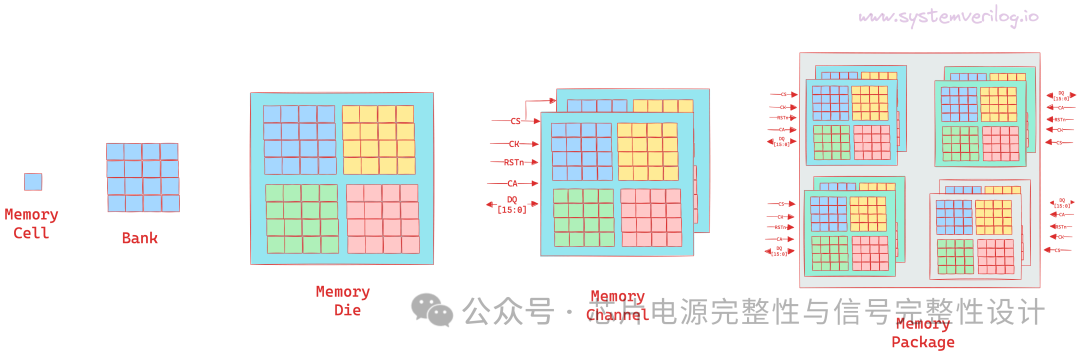

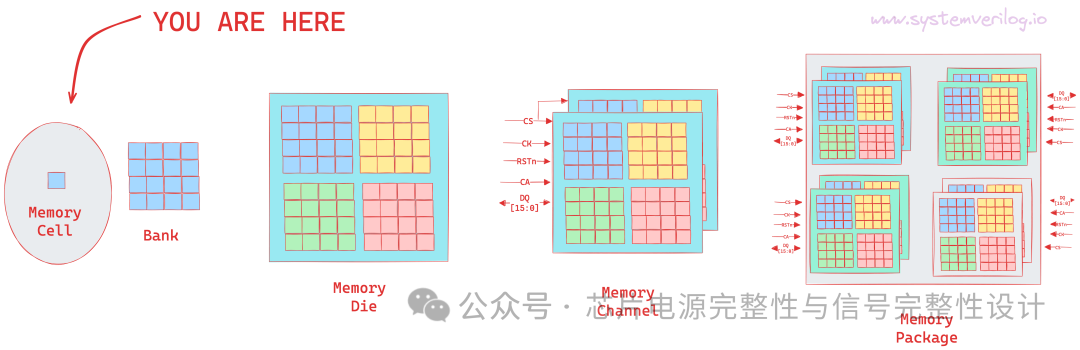

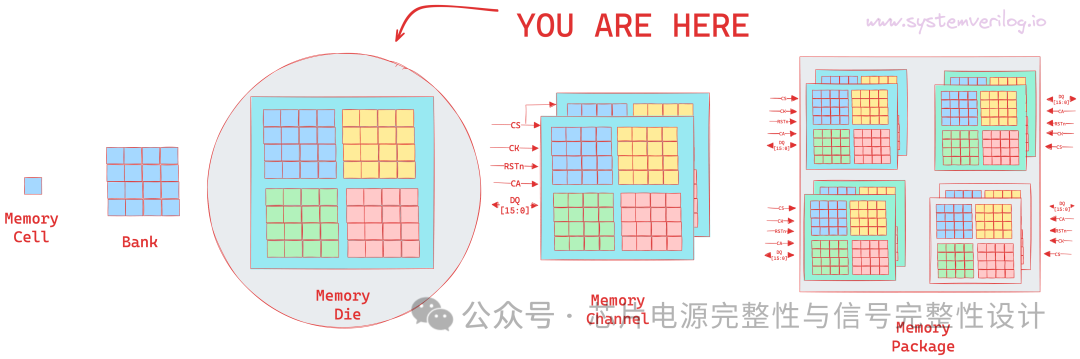

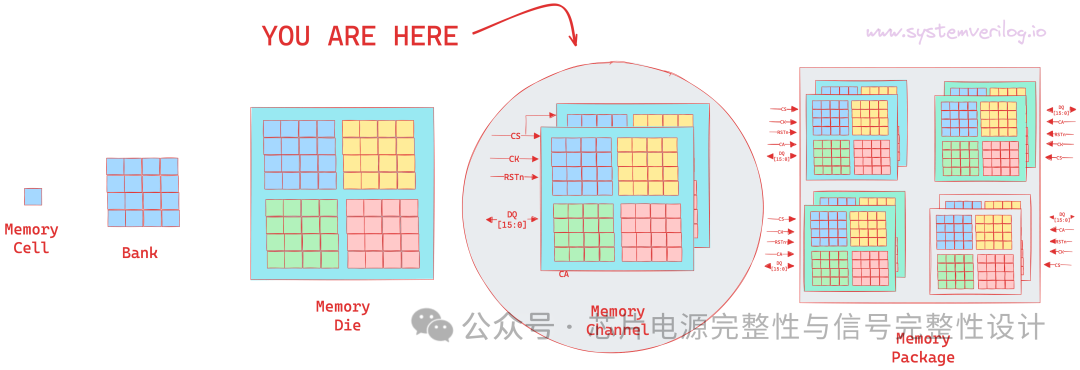

接下来将从单个DRAM存储单元开始,逐步探索其如何构成一个完整的焊接在PCB上的内存封装。

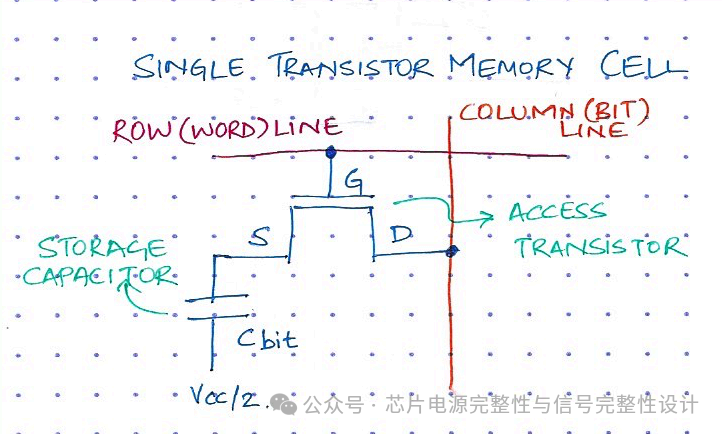

Memory Cell

在最底层,一个比特本质上是一个存储电荷的电容器和一个作为开关的晶体管组成。由于电容器会随时间放电,除非定期刷新(REFRESH),否则信息最终会丢失。这正是DRAM中“D”(动态)的由来,与SRAM中的“S”(静态)相对应。

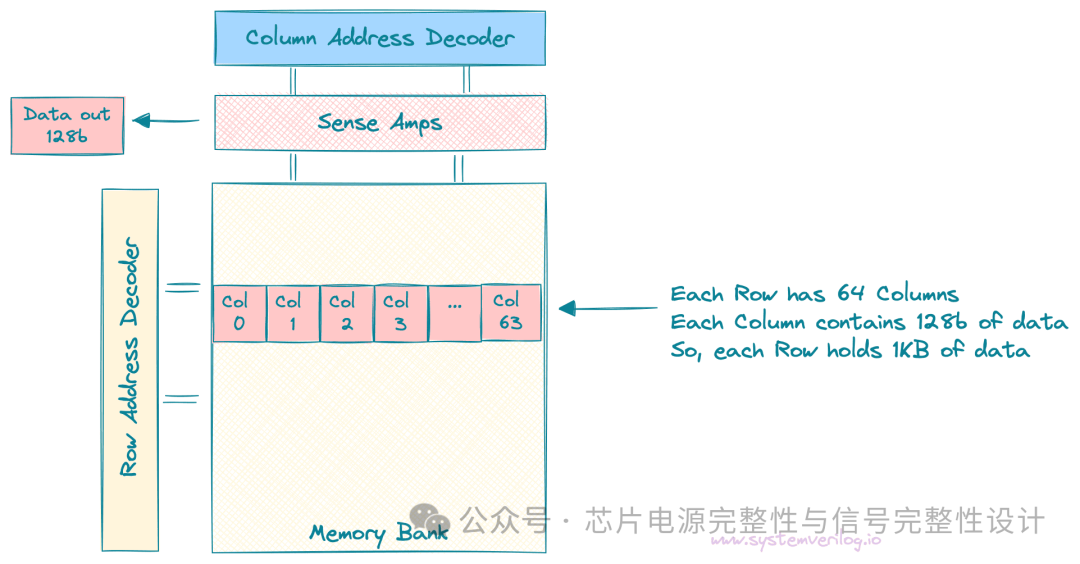

Bank, Rows, Columns

当将bit cell往上放大一级时,就会看到存储单元按行和列的网格排列;一个网格称为Bank,每个Bank还包含一个称为Sense Amps(灵敏放大器)的结构。在读取操作中,行首先被激活(ACTIVATE)并加载到Sense Amps中,随后通过列地址读取相应的列数据。

在LPDDR5规格中可以看到:

w每个Bank的一行存储1KB(8192bits)数据。

w这1KB数据按64列×128位排列(64×128b=8192b)。

w每次读/写操作需指定行地址和列地址,Bank返回128位数据。

LPDDR5 Bank Architecture

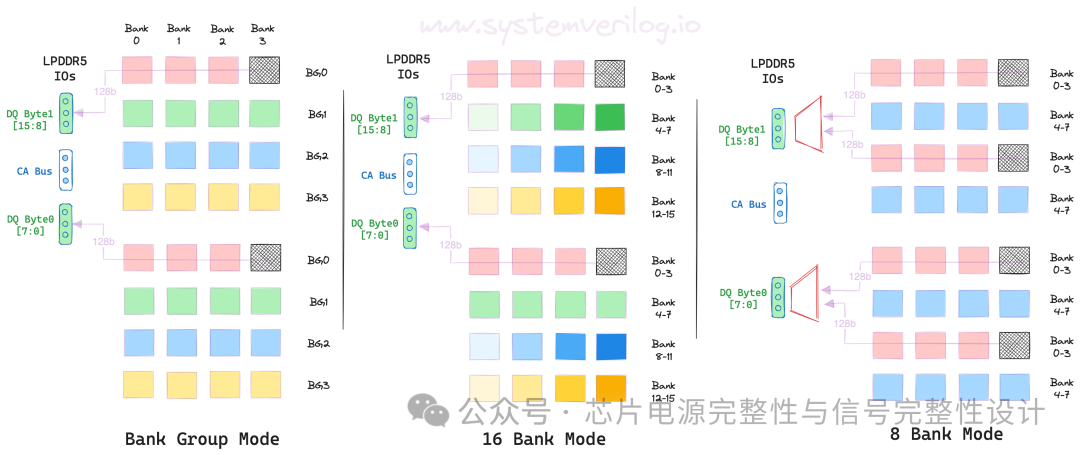

Bank模式

每个LPDDR5芯片(Die)包含32个Bank单元,可通过以下三种模式配置:

1.Bank Group模式(BG模式)

o32个Bank单元分为2组,每组4个Bank Group,每个Group包含4个Bank(2×4×4=32)。

o读/写操作时激活2个Bank,共访问256位数据(每个Bank返回128位)。

o适用场景:速度>3200 Mbps。

2.16 Bank模式

o32个Bank单元分为2组,每组16个Bank(2×16=32)。

o适用场景:速度≤3200 Mbps。

3.8 Bank模式

o32个Bank单元分为4组,每组8个Bank(4×8=32)。

o读/写操作时激活4个Bank,共访问512位数据。

那为何需要多种Bank模式?一般取决于两个:

一个是取决于所需要支持的速率:

w> 3200Mb/s选择BG mode

w<= 3200Mb/s选择16Bank mode

w8Bank mode全速支持

第二个取决于数据访问的宽度:

w在16 Bank模式和Bank Group模式下,一个Read操作并行激活2个Bank并访问256b的数据(记住每个Bank返回128b)。在LPDDR5中,数据总线是16位宽(DQ[15:0])。因此,256b的数据随后以16块的形式流出,每个块为16b (16x16 = 256)。这也被称为BL16或突发长度16。

w在8 Bank Mode中,如上图所示,每个READ/WRITE操作激活4个Bank,总共获取512b的数据。然后,这些数据以32拍的形式输出,每拍保存16b的数据(32x16 = 512)。这就是所谓的突发长度32。

上述bank mode的选择通过初始化时设置模式寄存器MR3来完成选择。

Page size

Page size是指激活行时加载到Sense Amps中的位数:

·16 Bank模式与BG模式:2KB

·8 Bank模式:4KB

在上两图中,我们看到bank中的每一行保存1KB的数据(64列,128b);以及16bank和bank group mode同时激活,得到256b。因此,从内存die的角度来看,激活了2个bank,总page size大小为2x1KB = 2KB。而在8bank mode模式下,一次访问激活4个bank,因此page大小为4KB。

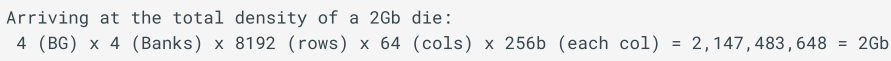

Density

LPDDR5存储目前已经量产了从2Gb到32Gb不同的容量,主要的不同是在一个die内 2Gb容量和32Gb容量每个bank的rows数,如下表是不同容量的对比信息。

这个容量的计算可以参照如下的方式,以2Gb为例:

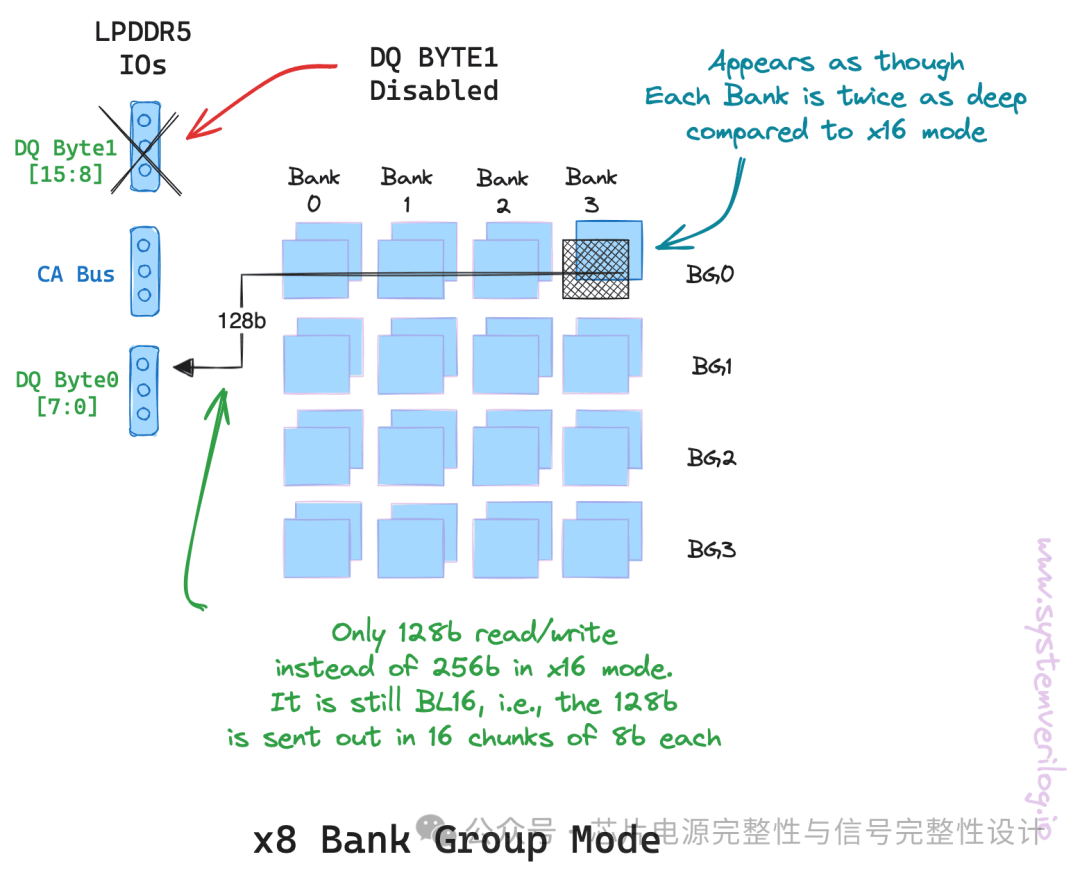

x8 DQ Mode

LPDDR5接口有16个DQ(数据)引脚。因此,默认情况下,内存以所谓的x16 DQ模式启动。从应用角度看,可以禁用8个DQ引脚并将内存置于x8 DQ模式。在这种模式下,在读或写访问期间只有一个Bank被激活(而不是2)。这样做的好处是将得到一个更深的内存,即,与x16模式相比,每个Bank似乎具有两倍的行数(将访问宽度减半,深度增加了一倍)。

请注意,这个表与前表相比,数组预取和page大小减半,行数翻倍。x16 VS x8模式在模式寄存器MR8中设置。

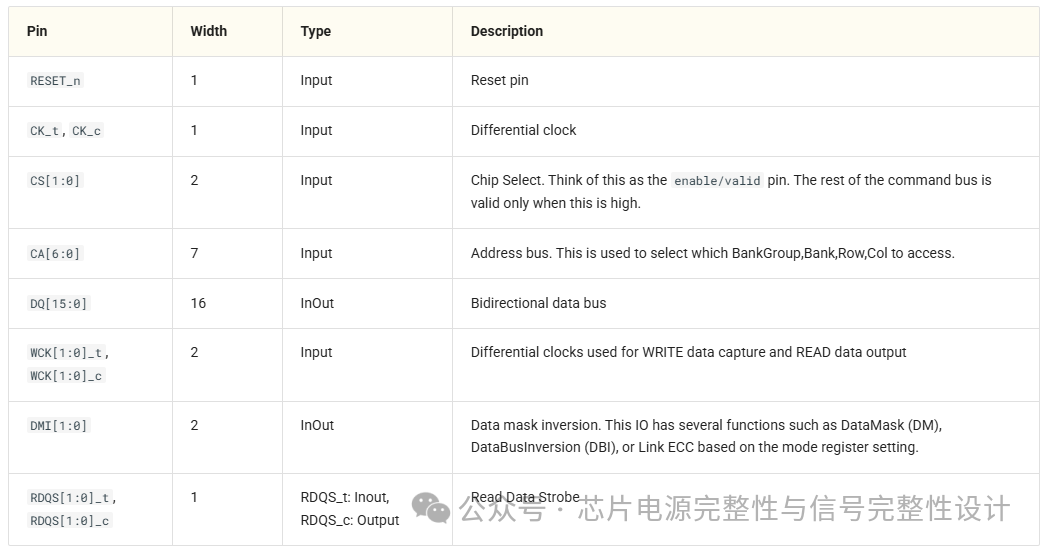

LPDDR5 Memory Channel

在LPDDR5设计中,有一个术语叫“通道数”。用最简单的术语来说,内存通道就是LPDDR5控制器与之交互的东西。内存控制器和内存通道之间的接口如下表IO描述。

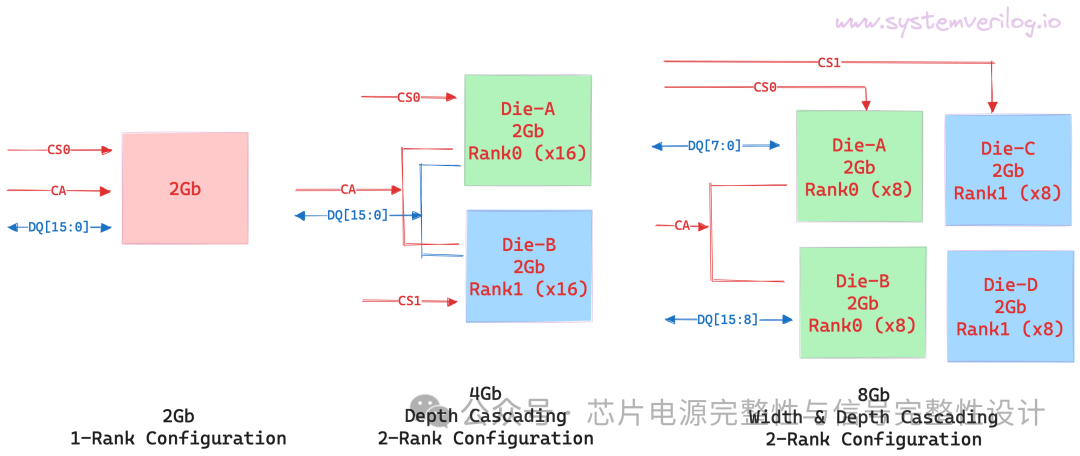

Ranks, Width cascading and depth cascading

一个通道可以由一个或多个LPDDR5内存芯片组成。在下面的图中,展示了如何配置多个2Gb内存模块来增加通道中可用的总内存容量。

1. 2Gb通道容量:只有一个2Gb的内存芯片连接到LPDDR5 IOs。

2. 4Gb通道容量:有2个2Gb的“宽度级联”芯片,也称为2- rank配置。通过设置ChipSelect0 (CS0引脚)访问Die-A,使用CS1引脚选择Die-B。但是,两个die共享相同的地址和数据总线,因为一次只有一个Chip Select引脚是活动的。

3. 8Gb通道容量:有4个2Gb die。与4Gb容量类似,有2-rank。但在每个rank中,有2个“宽度级联”的DIE,即每个DIE配有x8的宽度。

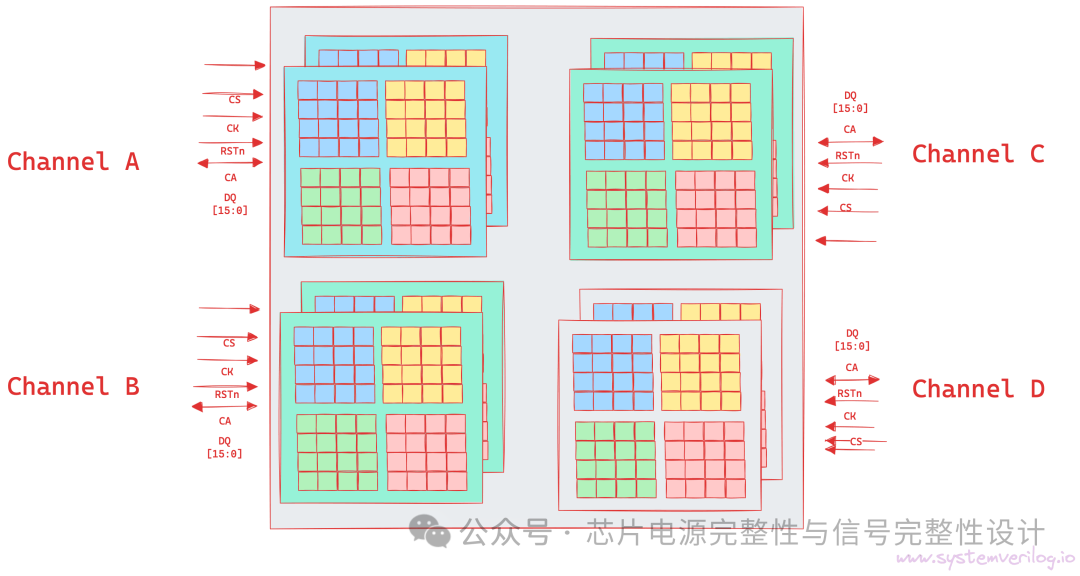

LPDDR5 Memory Package

通常,一个内存包含多个通道,这允许存储器制造商创建具有不同宽度和容量的存储器设备,以适应各种应用。供应商器件目录中的典型宽度和容量是:

•容量:4GB、8GB、16GB等。

•宽度:x16(1通道),x32(2通道),x64(4通道)。每个通道都可以独立访问,并且有自己的一组CA和DQ引脚。

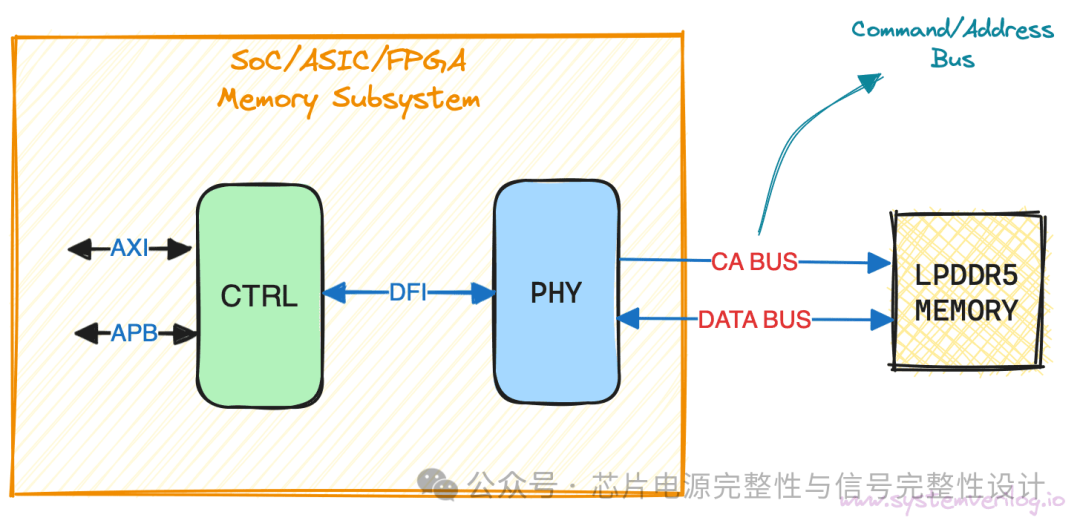

The SoC-LPDDR5 Interface

为了与LPDDR5存储器通信,SoC, ASIC, FPGA或处理器需要控制器和PHY。这三个实体——控制器、PHY和LPDDR5内存设备共同构成了LPDDR5内存子系统。

DFI Interface

可以将控制器视为逻辑层,确保在执行读、写或刷新操作时严格遵循LPDDR5协议的大型状态机。另一方面,PHY是物理层。它具有所需的所有模拟部件,以保证可靠的发射和捕获时钟,地址和数据信号进出存储器。

PHY和Controller通过一个称为DFI接口的标准接口相互通信。无论是在初始化阶段、校准阶段,还是准备执行READ/WRITE操作,PHY都可以通过该接口与控制器通信。

Controller Interface

访问DDR内存是一个微妙的过程,例如,要将数据写入内存,需要向内存发出多个命令来激活右行、行和列,并且必须在一个精确的时间间隔(称为WRITE - latency)之后启动数据。在所有这一切之间,需要在固定的时间内刷新内存,这样就不会丢失任何数据。

控制器抽象了上述所有复杂的问题,并提供了一个简单的接口,如AXI,通过它可以发出Write或Read操作。

除了提供一个简单的接口来访问内存,控制器还具有几个功能(如地址重新排序),以帮助SoC/处理器最大限度地提高内存带宽。这一点很重要,因为当涉及到笔记本电脑,手机或复杂的ASIC的性能时,内存几乎总是瓶颈。

283

283

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?