• Call gates

• Trap gates

• Interrupt gates

• Task gates

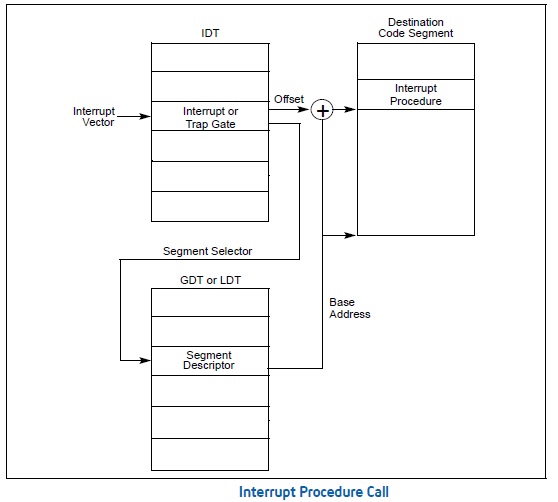

An interrupt gate or trap gate references an exception- or interrupt-handler procedure that runs in the context of the currently executing task. The segment selector for the gate points to a segment descriptor for an executable code segment in either the GDT or the current LDT. The offset field of the gate descriptor points to the beginning of the exception- or interrupt-handling procedure.

When the processor performs a call to the exception- or interrupt-handler procedure:

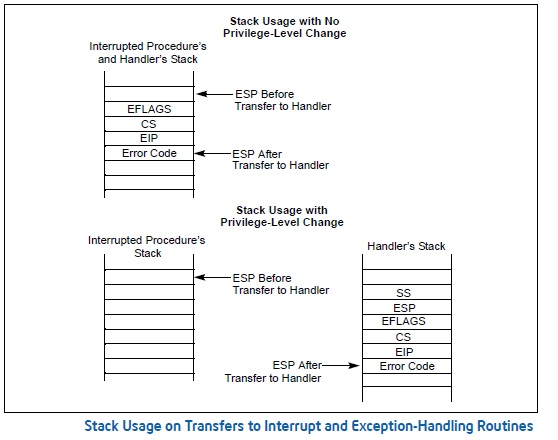

• If the handler procedure is going to be executed at a numerically lower privilege level, a stack switch occurs. When the stack switch occurs:

a. The segment selector and stack pointer for the stack to be used by the handler are obtained from the TSS

for the currently executing task. On this new stack, the processor pushes the stack segment selector and

stack pointer of the interrupted procedure.

b. The processor then saves the current state of the EFLAGS, CS, and EIP registers on the new stack

c. If an exception causes an error code to be saved, it is pushed on the new stack after the EIP value.

• If the handler procedure is going to be executed at the same privilege level as the interrupted procedure:

a. The processor saves the current state of the EFLAGS, CS, and EIP registers on the current stack

To return from an exception- or interrupt-handler procedure, the handler must use the IRET (or IRETD) instruction. The IRET instruction is similar to the RET instruction except that it restores the saved flags into the EFLAGS register. The IOPL field of the EFLAGS register is restored only if the CPL is 0. The IF flag is changed only if the CPL is less than or equal to the IOPL. If a stack switch occurred when calling the handler procedure, the IRET instruction switches back to the interrupted procedure’s stack on the return.b. If an exception causes an error code to be saved, it is pushed on the current stack after the EIP value.

1421

1421

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?