0. 状态

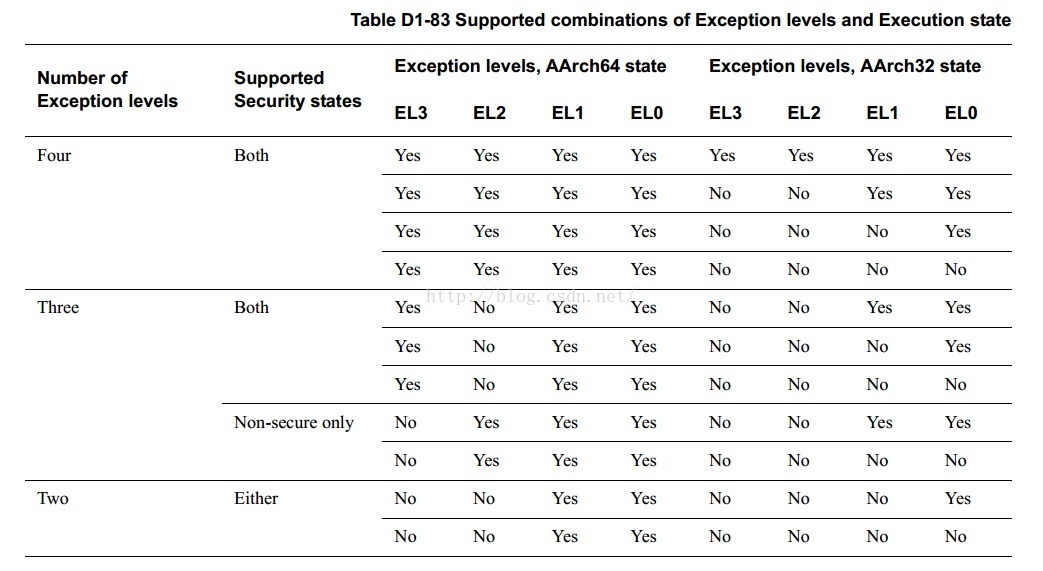

执行态: AARCH64, AARCH32

最高异常等级只能工作在Aarch64, 其他EL可以工作在Aarch64或者Aarch32. SCR_EL3.RW, HCR_EL2.RW和PSTATE控制执行状态。

Security态: Security 和 non-Security

SCR_EL3.NS 控制security状态

1. 寄存器

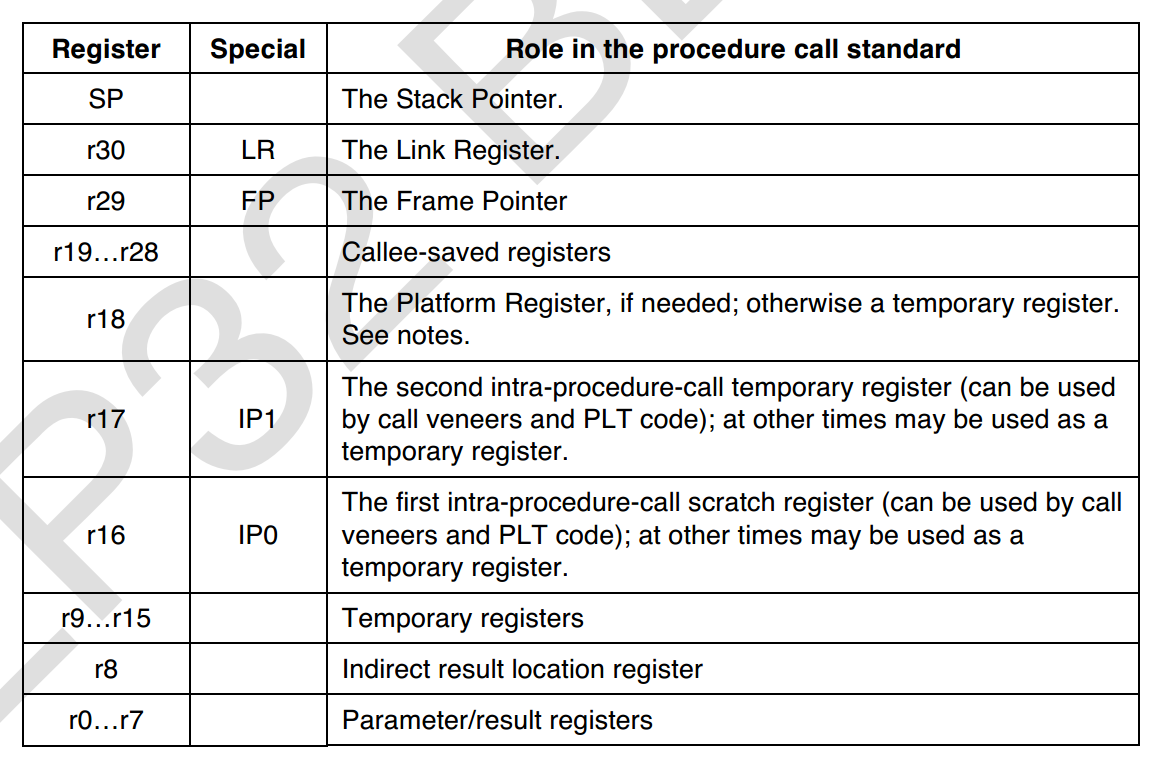

共31个64bit GPR寄存器X0~X30 ,X29做为FP, X30作为LR。

另外还有PC,SPs(SPEL0~SPEL3), ELRs(exception link register)。

32个128bit 浮点寄存器V0~V31

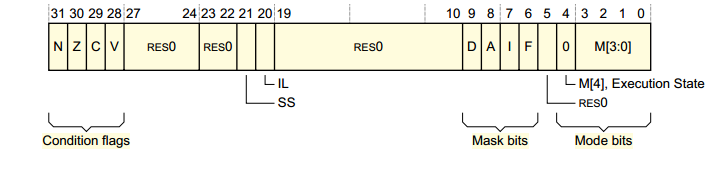

PSTATE:处理器状态,pstate不是一个寄存器,由几个寄存器组成(条件寄存器:NZCV, 异常mask寄存器:DAIF, SP选择寄存器:SPSEL. 异常等级寄存器: CurrentEL)

SPSRs:当异常发生时,PSTATE在SPSRs里面保存。

M[3:2] Encodes the Exception level, 0-3. M[1] Reserved

M[0] Selects the SP:

0 SP_EL0

1 SP_ELx

2. 指令集

A64指令集, 寄存器位宽 w-32位, x-64位

寻址:寄存器索引寻址,PC相对寻址,Load/Store寻址

3. 异常模型

异常分为同步异常和异步异常。

同步异常有如下特点:

a.由直接执行或者试图执行一条指令产品

b.精确的 (能保证给出正确的pc)

异步异常也就是中断,包括SError,IRQ,FIQ。

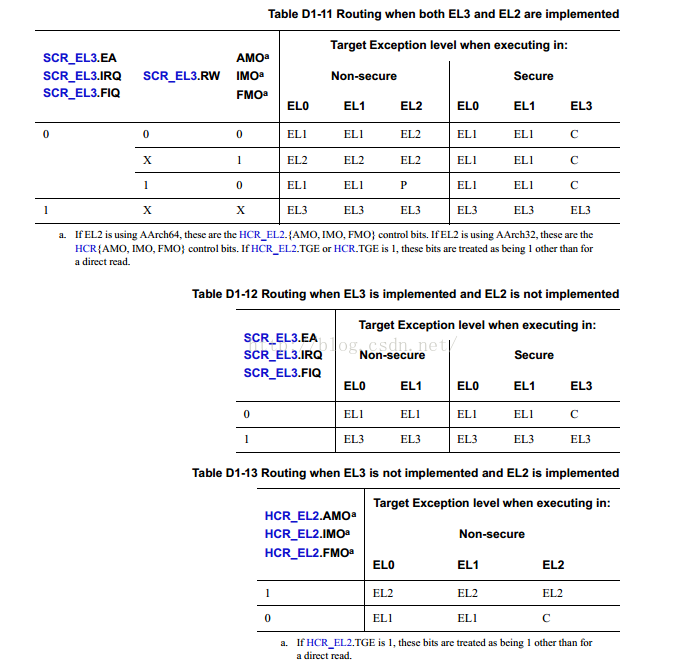

ARMv8异常模型,Exception Level 从EL0到EL3. EL3权限最大

EL0 Applications.

EL1 OS kernel and associated functionsthat are typically described as privileged.

EL2 Hypervisor.

EL3 Secure monitor.

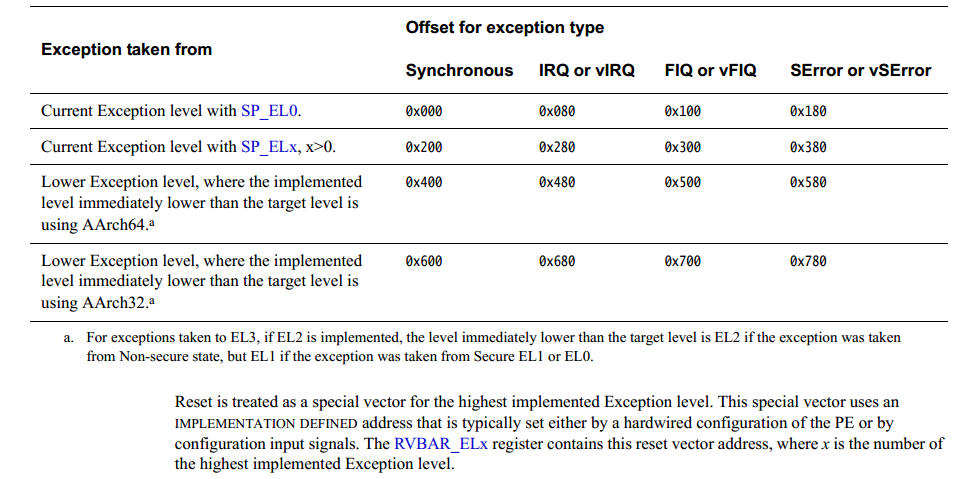

异常基址寄存器:VBAR_ELx, 要求1k字节对齐。

Exception Entry:

PSTATE -> SPSR_ELx

PC -> ELR_ELx

PSTATE(D,A,I,F) -> 0b1111

更新ESR_ELx 如果是同步异常或者SError

选择SP_ELx

跳转到异常向量定义的地址

Exception return:

执行ERET指令从异常返回

ELR_ELx ----> PC

SPSR_ELx ----> PSTATE

异常返回同时执行:

设置Event Register

清local exclusive monitor,实现定义是否清global exclusive monitor

异常优先级(由高到低):

1). Software Step exceptions

2). Misaligned PC exceptions

3). Instruction Abort exceptions

4). Hardware Breakpoint exceptions or Address Matching Vector Catch exception

5). Illegal Execution State exceptions

6). Exceptions taken from EL1 toEL2 because of one of the following configuration settings:

• For exceptions taken from AArch64 state:

— HSTR_EL2.Tn.

— HCR_EL2.TIDCP.

• For exceptions taken from AArch32 state:

— HSTR.Tn.

— HCR.TIDCP.

7). Undefined Instruction exception

......19). Trapped floating-point exceptions

20). Stack Pointer Alignment faults

21). Data Abort exceptions other than a Data Abort exception generated by a Synchronous external abort that was

not generated by a translation table walk

22). Watchpoint exceptions.

23). Data Abort exception generated by a Synchronous external abort that was not generated by a translation table

walk

如果中断进入pending态先于以下情况,cpu会先响应中断处理(当然在中断没有关闭的情况):

An ISB instruction.

Exception entry.

Exception return.

Exit from Debug state.

4. MMU

内存属性:和armv7相比,去掉了strong order。只有nomal和device了。

None-security: EL1&0 VA --Stage 1----> IPA ---Stage 2---> PA

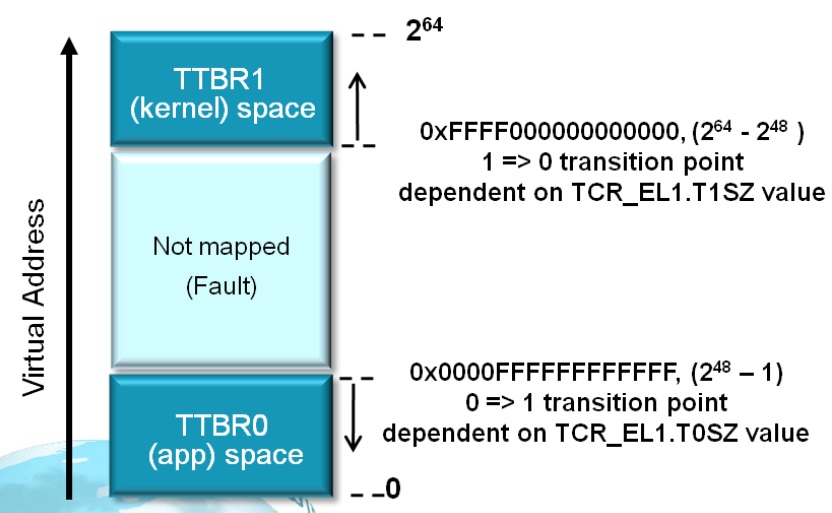

VA: 地址宽度48 bit。分为两个虚拟地址空间,0x0~2^48 和 2^64-2^48 ~ 2^64。

PA: 地址最大宽度为48 bit,可以从ID_AA64MMFR0_EL1读取实际支持多少bit。

EL1模式下的控制MMU的主要寄存器:

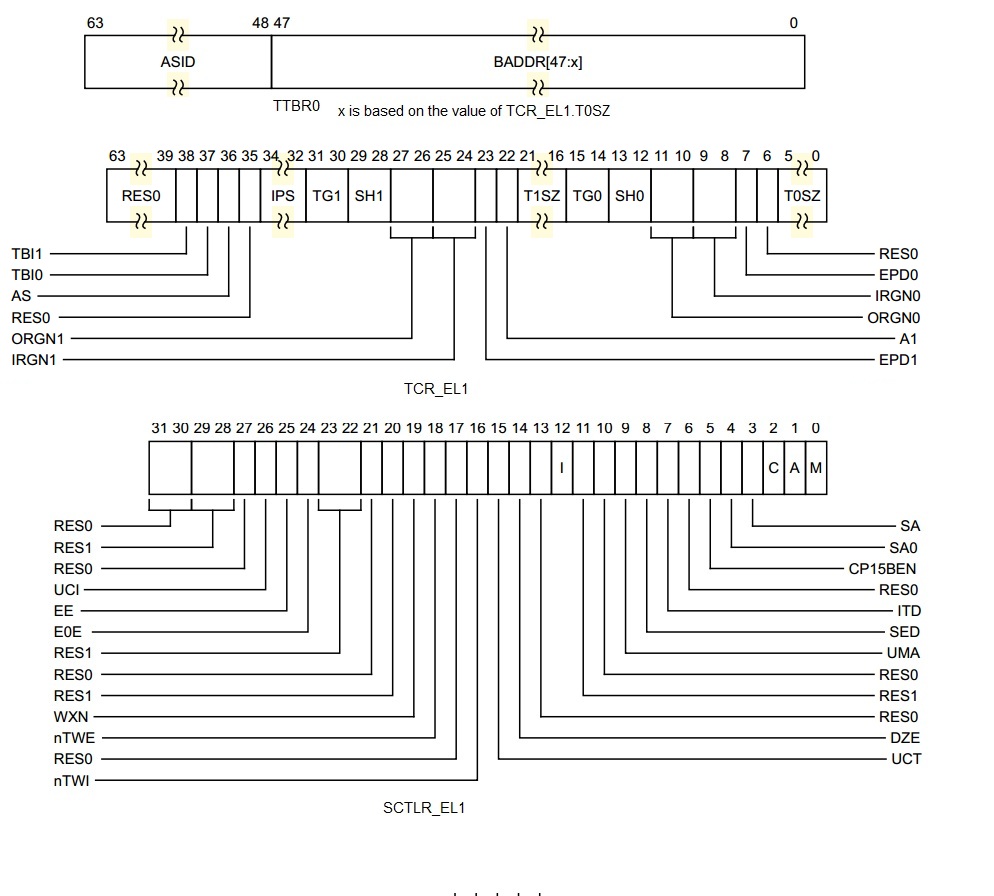

TTBR0_EL1/EEBR1_EL1 转换表的基地址寄存器。VA[55]为0使用TTBR0,为1使用TTBR1。

SCTLR_EL1 (EE, M)控制转换表的大小端和MMU使能

TCR_EL1转换表控制寄存器,可以设置ASID宽度,页的大小,虚拟地址范围。设置页表的内存属性等等。

MAIR_EL1内存属性间接寄存器,提供内存属性编码,为页或块的内存属性attribIdx提供索引。

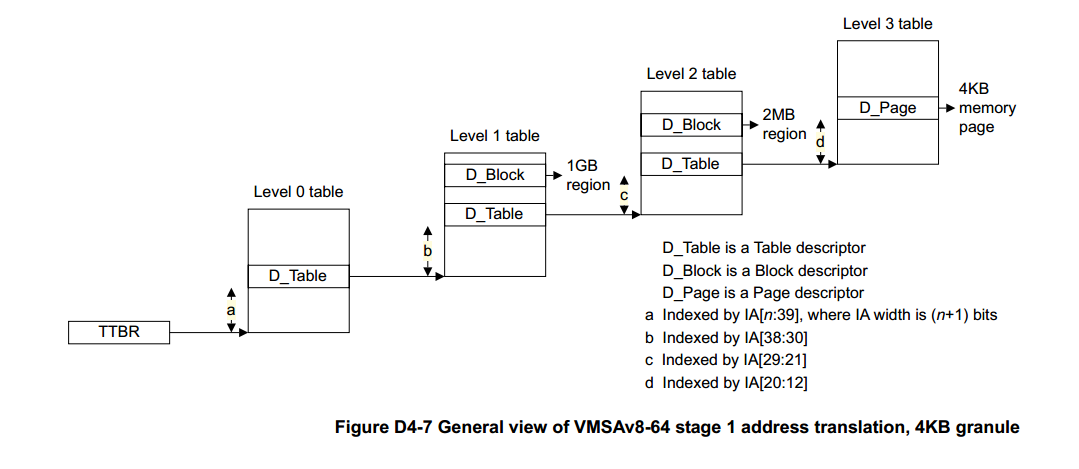

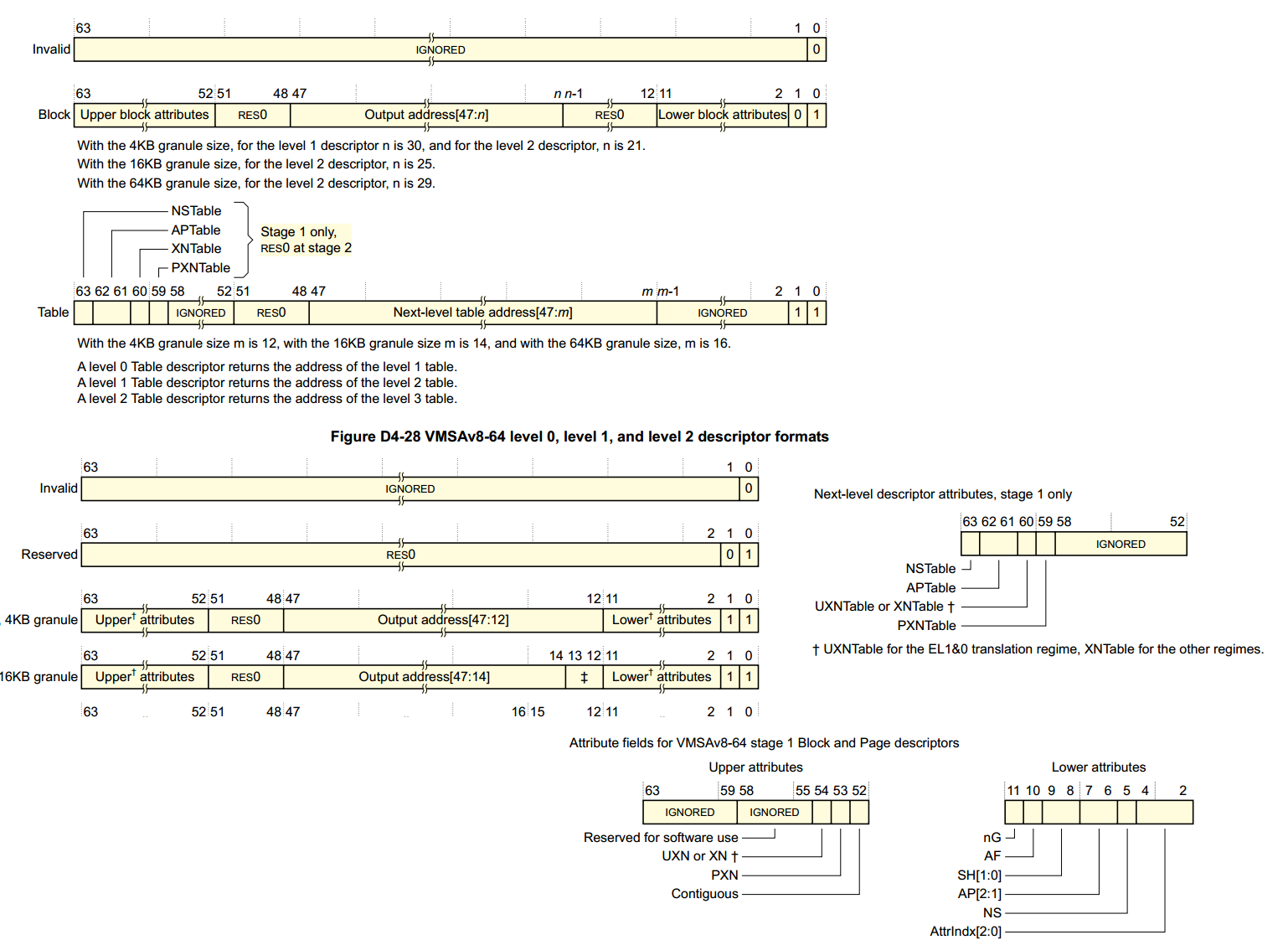

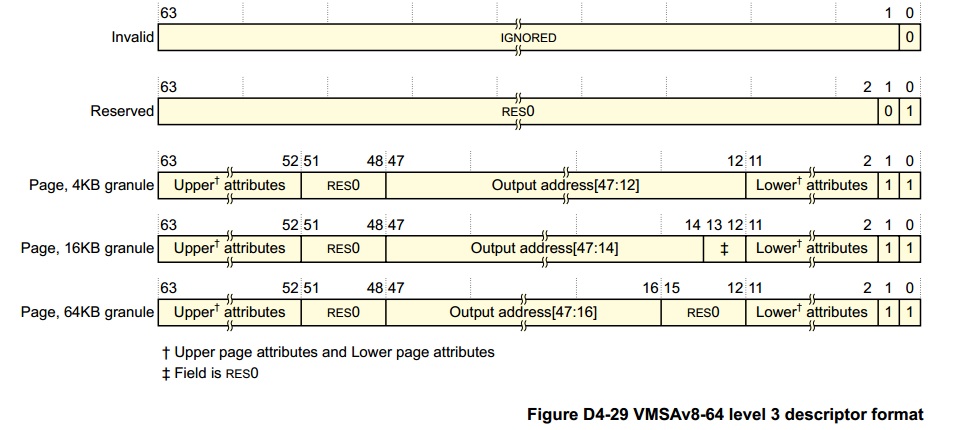

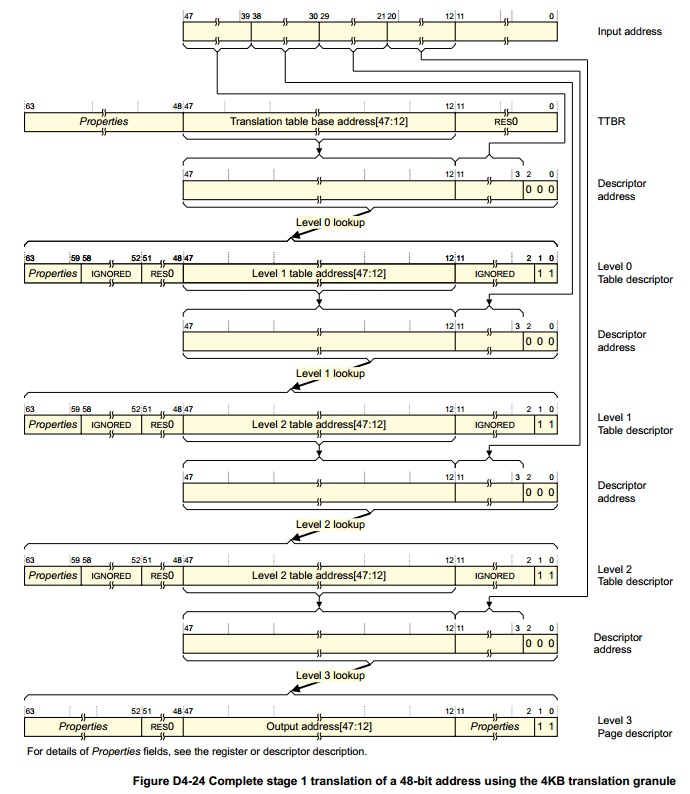

转换表格式: 最多四级地址转换,Input Address/Output Address 48bit.

页粒度:4k/16k/64k。

块粒度:

4k页:level1的块支持1G,level2的块支持2M。 level0不支持块。 level0是必须的如果地址宽度大于等于40bit。最多四级转换,页目录9bit(47-39:38-30:29-21:20-12)

16k页:level2的块支持32M。 level0和level1不支持块。最多四级转换,页目录11bit(47:46-36:35-25:24-14)

64k页:level2的块支持512M。 level1不支持块。无level0, 最多三级转换,页目录13bit(47-42:41-29:28-16)

5. Cache

指令cache

支持PIPT(physical index physical tag),VIPT,VIVT。

数据cache

Non-cacheable

Write-Through cacheable

Write-Back cacheable

cache分配策略:

Read-Allocate, Transient Read-Allocate, or No Read-Allocate

Write-Allocate, Transient Write-Allocate, or No Write-Allocate

non-cacheable 不等于cacheable with both no read-allocate and no write-allocate. non-cacheable的内存能和除cacheable with both no read-allocate and no write-allocate以外的内存保证一致性。

cache的使能:

SCTLR_EL1的I bit控制指令cache的使能. C bit控制数据cache和unified cache的使能。

PoU(Point of Unification):PoU is the point in the memory system where the data, instruction and table walk (MMU) interfaces of this core see the same copy of a location

PoC(Point of Coherency):PoC is where this core and an other master (e.g. a DMA) see the same copy

6. AAPCS64 (Procedure Call Standard for the ARM 64-bit Architecture)

ARM64的栈要求16字节对齐

962

962

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?