一、SOI工艺相比于传统体硅工艺的优缺点

1.SOI工艺相较于传统体硅工艺在衬底上增加了氧化层,该绝缘层使SOI射频器件从衬底的泄露大大降低

2.衬底的氧化层使SOI射频器件天然无闩锁效应

(闩锁效应:闩锁效应是晶体管的漏源与阱、衬底之间形成PNPN四层结构,其本质是由于寄生的双极型晶体管形成的正反馈回路,使器件进入低阻态并持续导通,使电流急剧增大)

3.氧化层阻断了SOI晶体管器件到衬底的寄生电容,能够降低开关延时并提升电路速度

4.SOI工艺器件在射频应用中有更好的隔离度

5.SOI工艺材料成本较高、工艺复杂;氧化层的存在使得晶圆变得脆弱,生产过程中易破裂;氧化层使得SOI器件散热性能差

相比于传统CMOS工艺,SOI工艺更适合用在射频IC器件的设计中。

二、晶体管的选择

1.导通电阻分析:

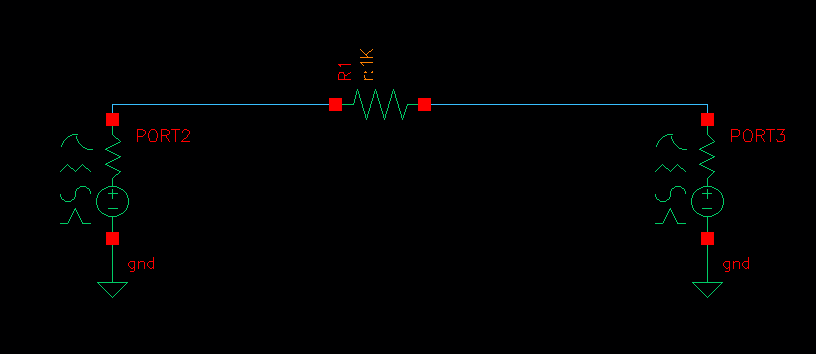

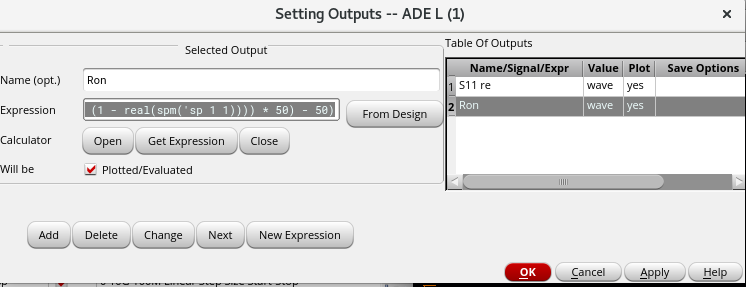

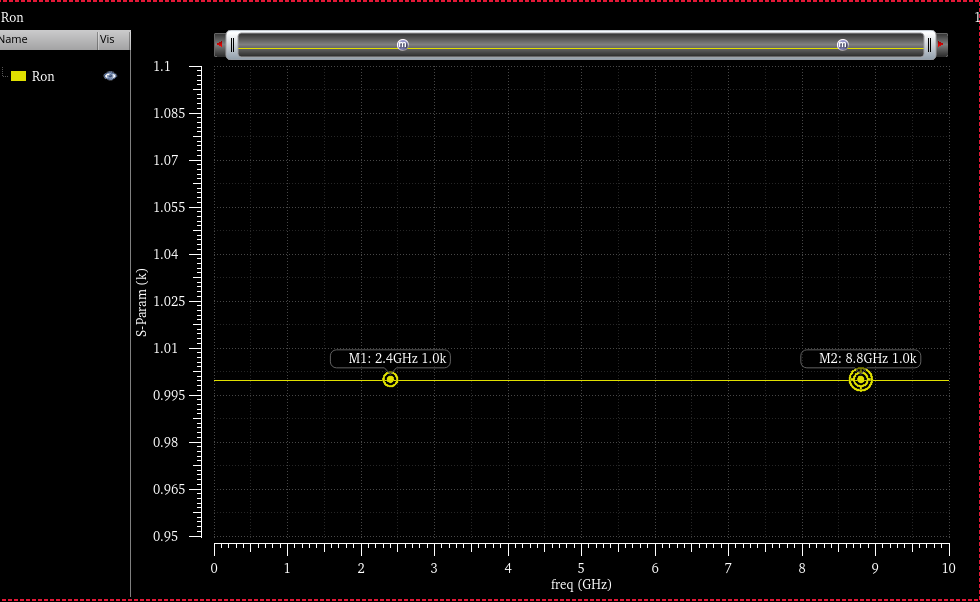

1>先用理想电阻确定公式的准确性

((((1 + real(spm('sp 1 1))) / (1 - real(spm('sp 1 1)))) * 50) - 50)

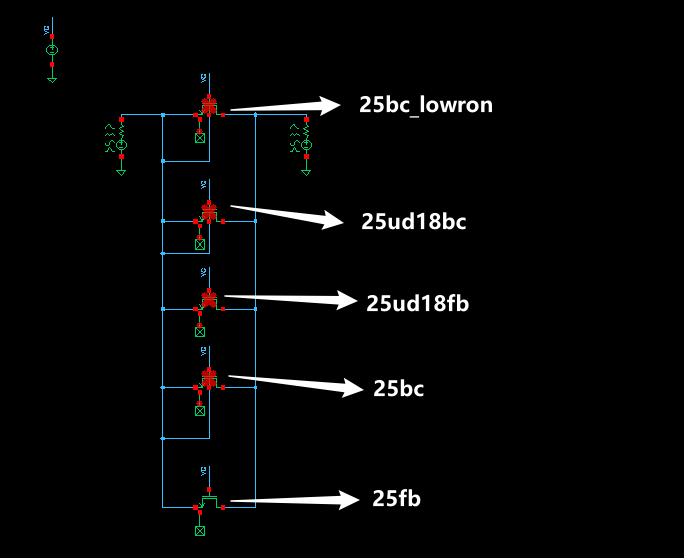

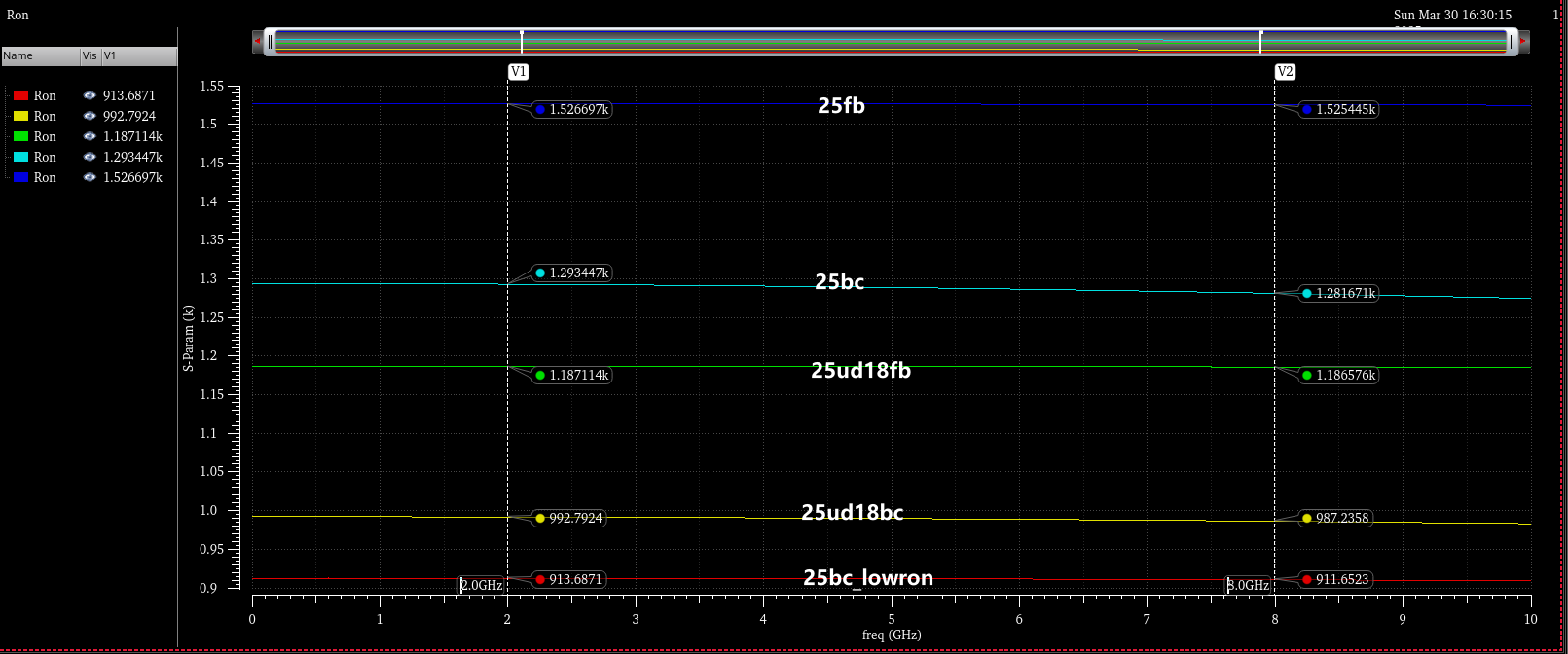

2>对比工艺库中的几种晶体管的导通电阻(仅对比射频管)

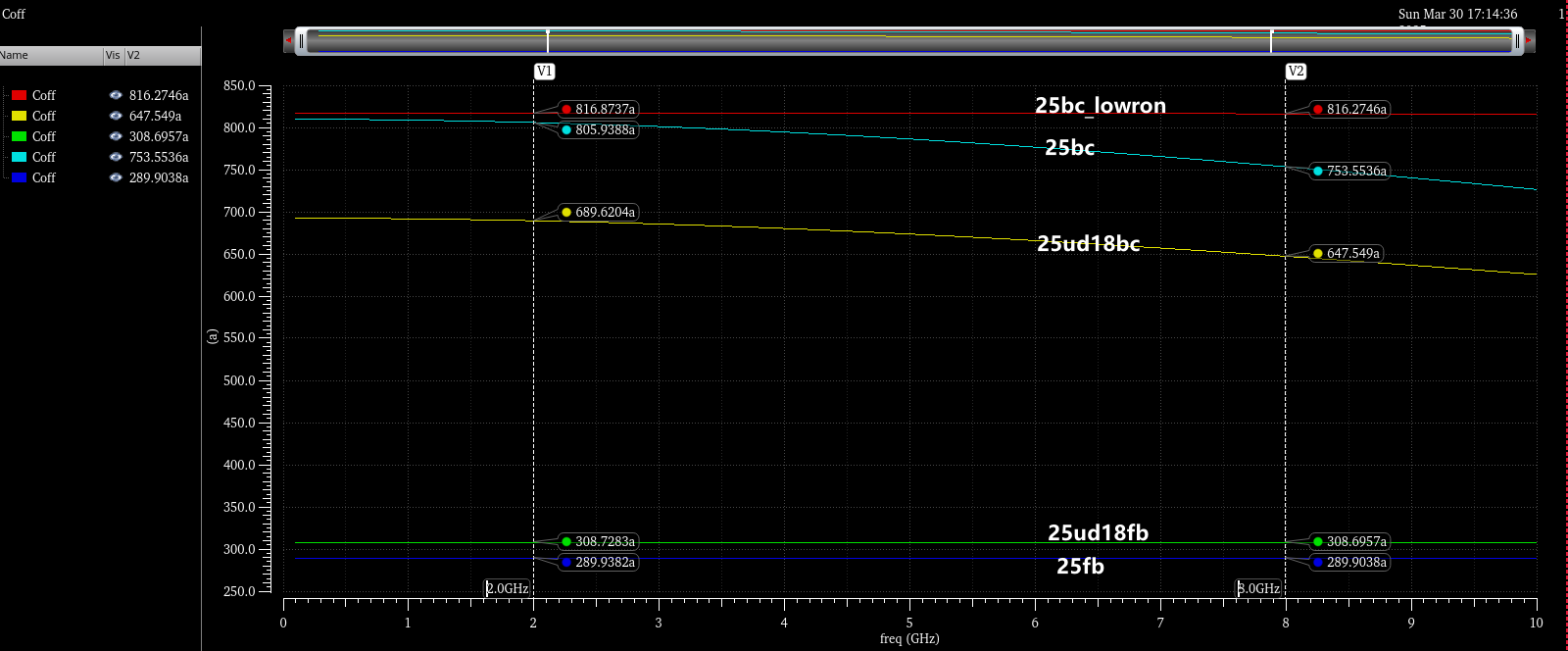

对比工艺库中几种2.5V控的射频晶体管(晶体管尺寸均为该类型最小尺寸),其中25bc_lowron管子的等效导通电阻最小。

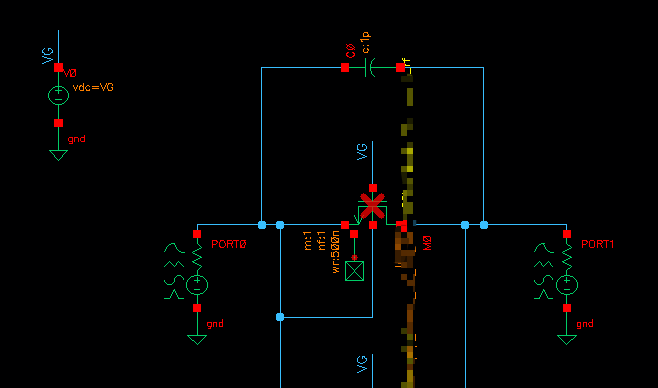

2.等效关断寄生电容分析

用1pF的理想电容验证公式的准确性

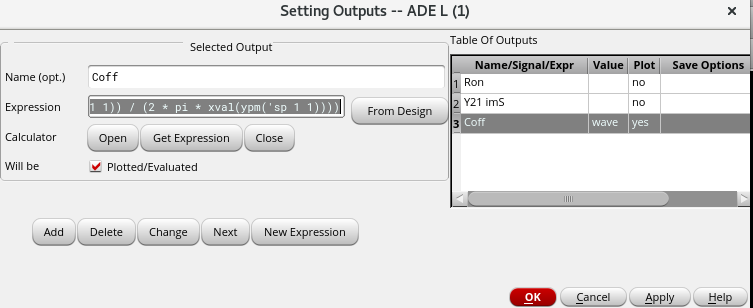

(imag(ypm('sp 1 1)) / (2 * pi * xval(ypm('sp 1 1))))

(imag(ypm('sp 2 1)) / (2 * pi * xval(ypm('sp 2 1))))

(这里我不是特别理解用21和11两种方式计算的具体等效电容分别代表什么,待以后分析)

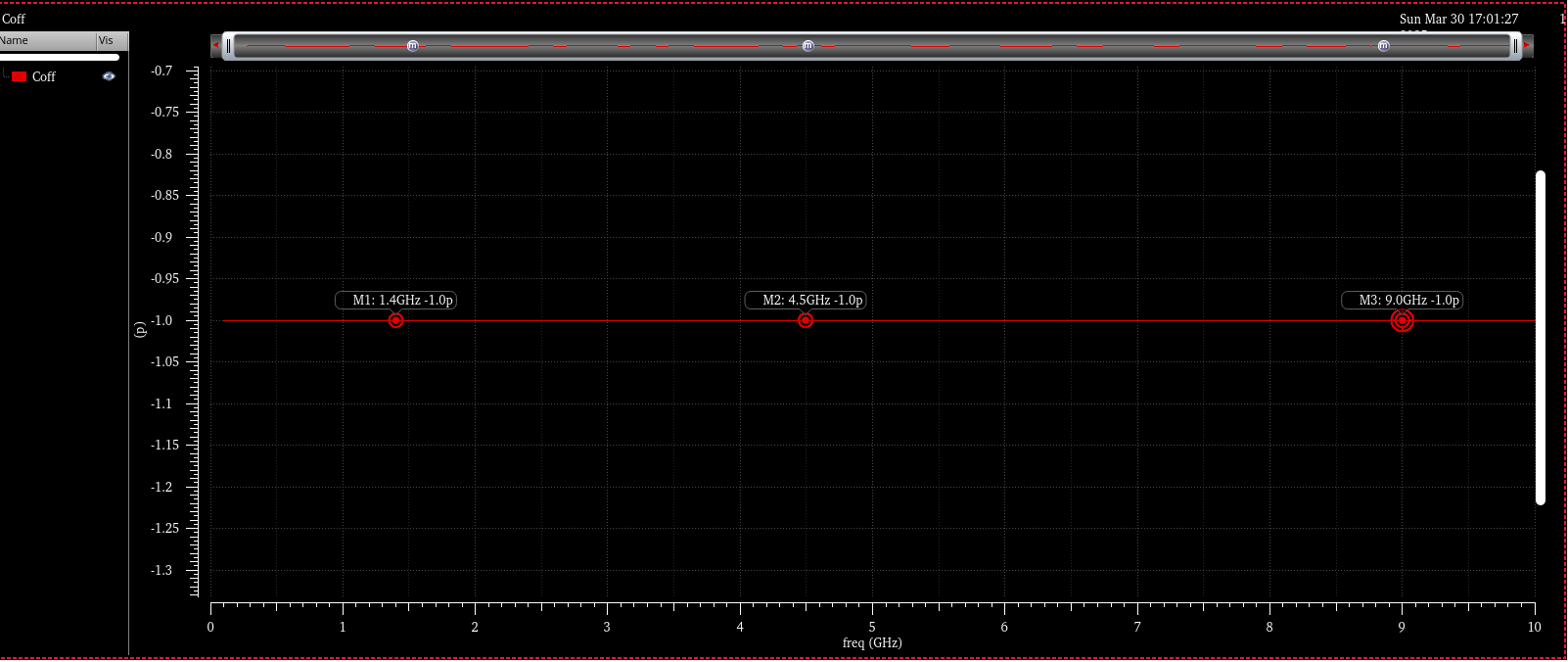

用S11计算出的关断等效电容(仍然保持晶体管最小尺寸,所以寄生电容非常小)

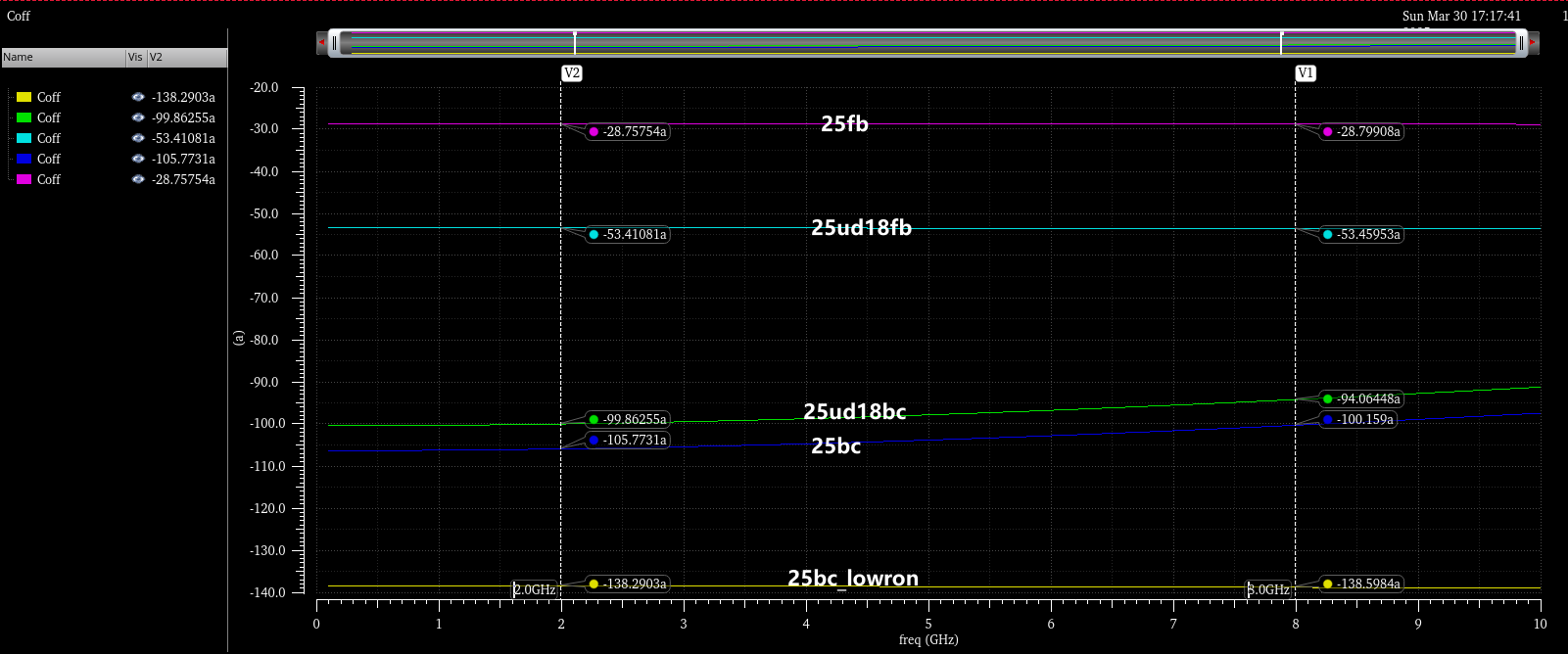

用S21计算出的关断等效寄生电容

用S21计算出的关断等效寄生电容

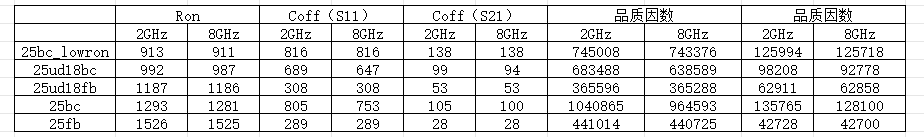

整理品质因数表格如下:

若单纯从品质因数来看的话,相同类型的晶体管中浮体管明显要优于体接触式晶体管,但浮体管因体区悬浮,随时间会累积电荷,大量电荷的累积可能导致晶体管阈值电压的变化(体端又称为背栅,VSB的电压会影响到阈值电压 )其开关速度也可能因为电荷的累积变慢,相对于体接触型晶体管,浮体更适用于对阈值电压、开关速度波动不敏感的电路中,如低功耗SRAM电路等。所以在射频开关应用中不优先选择浮体管。

)其开关速度也可能因为电荷的累积变慢,相对于体接触型晶体管,浮体更适用于对阈值电压、开关速度波动不敏感的电路中,如低功耗SRAM电路等。所以在射频开关应用中不优先选择浮体管。

25bc管的品质因数明显劣于25bc_lowron和25ud18bc管,所以不选择该类型晶体管。

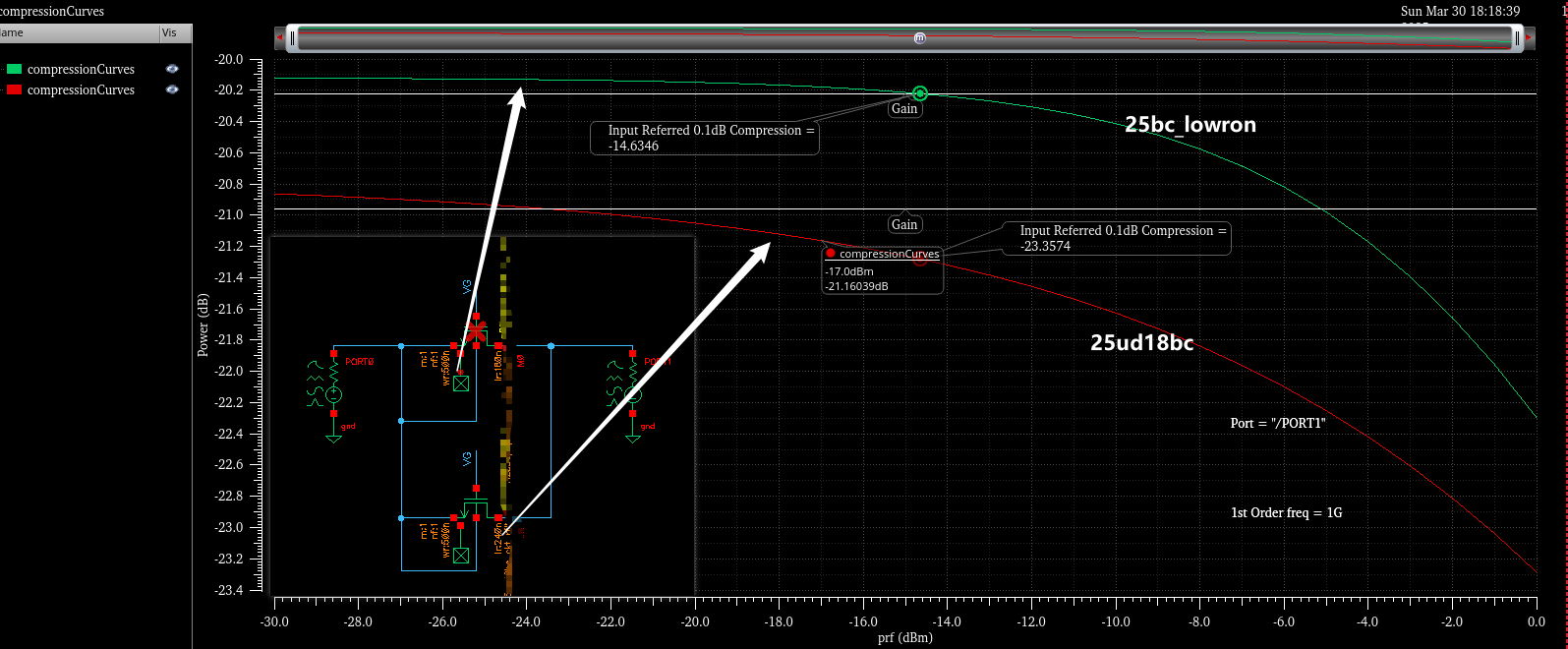

25bc_lowron晶体管相对于25ud18晶体管Ron小,但Coff大,这点要综合取舍,我们对导通状态下两种类型晶体管仿真P0.1B:

在相同条件下,25bc_lowron晶体管有着明显的P0.1dB的优势,所以在后续的分析设计中,选取该类型晶体管作为开关电路的核心射频管。

670

670

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?